# Size Reduction and Tuning of Integrated Folded Patch Antennas Using Slots

P. M. Mendes, M. Bartek<sup>(1)</sup>, J. N. Burghartz<sup>(1)</sup>, J. H. Correia

(1)Lab. of ECTM/DIMES, Delft University of Technology

Dept. of Industrial Electronics, University of Minho

Tel.: +351-253510382, Fax: +351-253-510189, e-mail: paulo.mendes@dei.uminho.pt

Abstract — We report on the use of slots for size reduction and tuning of folded patch antennas operating in the 5-6 GHz ISM band, with intended application in short-range wireless communications. Varying the slot length modifies the antenna electrical length, thus providing a new degree of freedom to control the antenna operating properties, and is the main novelty of our work. This technique was used for antenna tuning, input impedance control, and, very important, for antenna size reduction. Keeping the operating frequency at 5.7 GHz, application of slots allows an antenna size reduction close to 30%. Keeping the antenna dimensions constant, application of slots allows its tuning from 5.7 GHz down to 4.8 GHz and is potentially suitable for dynamic antenna reconfiguration.

#### I. INTRODUCTION

Sensor networks are expected to be the 21<sup>st</sup> century holly Graal in sensing [1]. Furthermore, application of such distributed sensing systems will be highly facilitated if cheap and easy-to-use 'on-chip' or 'in-package' solutions, equipped with short-range wireless communication capabilities, would be available.

The necessary on-chip integrated transceivers, from baseband to antenna input/output, are already available, where short-range wireless communication systems operating in the 5-6 GHz ISM band play an important role in the actual communication standards. However, the antenna, as the key element in achieving a fully integrated solution, notwithstanding all the development efforts, still remains to be an open challenge. Full integration requires the availability of very-small antennas that can be fitted into a single chip.

Several small and planar antenna types have been proposed for wireless communications [2] but none of them was designed to fulfil all the restrictions and requirements set by on-chip integration. restrictions include the properties of available substrate materials and the way they can be processed. Many of the previously proposed solutions to integrate antennas on-chip have been based on the design of planar antennas using silicon as substrate. Since the low-ohmic silicon substrate suffers from high losses, high-resistivity silicon or bulk micromachining have to be used in order to increase the antenna efficiency. Nevertheless, the aforementioned solutions have the drawback of increased cost, and the micromachining solution have also the penalty of large area used for antenna implementation. In this way, a preferable solution to decrease the antenna losses may be to use a combination of a low-loss material with silicon. The new material can be used as antenna substrate and any required high-quality factor passives [3], and the silicon will be used to implement the necessary circuitry.

The combination of materials may be achieved with the use of WLCSP techniques, like adhesive wafer bonding and through-wafer electrical via formation, which allows the use of silicon together with different silicon-compatible substrates [4]. However, typical silicon-compatible substrates (e.g. glass, BCB, polyimide, SU-8) have lower dielectric constant compared to silicon. In this way, the use of such materials reduces the losses at the expense of a size increase in the integrated antenna. Therefore, the use of an advanced antenna design may be required to overcome this drawback, providing a small and effective radiator.

In our previous work [5] and other related work [6], the use of shorted-folded patch antennas was considered as a solution to obtain a small antenna. Notwithstanding the obtained success, the dimensions of the developed antenna are still rather large.

In this work, we discuss how the use of properly positioned slots allows a more compact antenna solution or, if desired, a new way for antenna tuning. We will present different options to use the slots for folded patch antenna design.

## II. ANTENNA DESIGN

A folded patch antenna was first designed to operate at 5.7 GHz, a frequency chosen to be inside the 5-6 GHz ISM band. The antenna modeling was carried out with a high frequency structure simulator (HFSS) software, where all the simulation analysis was performed. This simulation tool was already used previously for antenna design, where good match between modeling and experimental results was achieved.

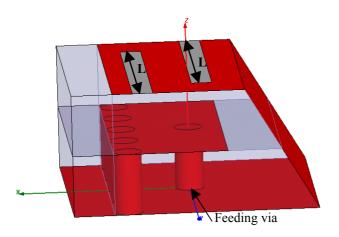

The proposed antenna is formed by three horizontal metal sheets that are electrically connected and by two vertical metal walls, where the walls can be made by via fences or slots. All this is embedded in a dielectric substrate having certain electrical permittivity and dielectric losses. These two parameters together with the antenna geometry, and its effective dimensions, will determine the radiation characteristics and overall performance. Fig. 1 shows the model for the proposed double-slotted folded-patch antenna.

Fig. 1. HFSS model of the proposed double-slotted folded patch antenna model.

To obtain an antenna with high efficiency, the metal layers should have the minimum resistivity possible and the silicon-compatible material used for the antenna substrate should be as low-loss as possible.

The antenna design starts with the model of one antenna without slots. That design is based in the knowledge that the operating frequency can be adjusted by proper selection of the antenna size and middle patch length, or changing the substrate thickness [7].

Starting from the previous design of a folded patch antenna, the slots were placed on the top patch. The placement of these slots introduces a new degree of freedom in the antenna design. When the slots are added, the antenna operating frequency was shifted down and, consequently, the input impedance was also changed. From this observation, we found that it was possible to use the slots to tune the antenna operating frequency and to change its input impedance.

# III. ANTENNA FABRICATION

The designed antenna was then fabricated on a stack of two 4003 Rogers<sup>TM</sup> substrates. This substrate was chosen because it has electrical properties (dielectric permittivity and losses) similar to some silicon-compatible materials. In this way, it is possible to have a better idea of the properties of an integrated antenna fabricated with the silicon-compatible materials.

The antenna fabrication started with the drilling of the shorting and feeding vias on the bottom substrate. This was done using a standard PCB drilling machine. This machine was used to make holes that are 700  $\mu m$  in diameter. After that, the drilling machine was also used to remove the undesired foil copper in order to obtain the desired antenna configuration. The bottom and top antenna parts where then obtained by dicing using a PCB cutting machine. The feeding and shorting vias were created and both substrates placed together. Finally, a strip of copper tape was used to perform the angled wall interconnecting the ground plane and top patch.

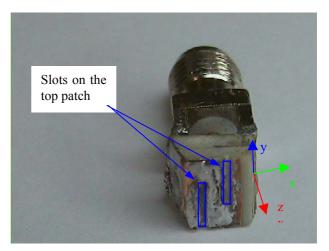

Fig. 2 shows the fabricated prototype, where the slots on the top patch are highlighted.

Fig. 2. Proposed double-slotted folded patch antenna fabricated prototype.

The very last step was to solder the antenna to a SMA connector, which was then used to perform the measurements. Since the ground plane is very small, this connector is a possible source of influence in the antenna behaviour and should be included in the antenna model.

### IV. RESULTS AND MEASUREMENTS

All the S-Parameter measurements were performed with a vector network analyzer previously calibrated with one-port calibration.

# A. Antenna Tuning

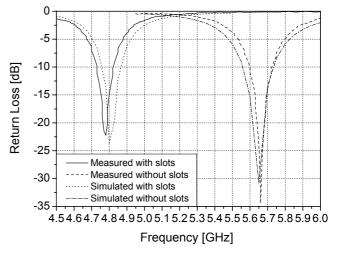

The plot in Fig. 3 shows the effect of placing two slots on the top patch.

Fig. 3. Measured and simulated return loss with and without slots on the top patch.

When the slots are inserted, the antenna operating frequency is shifted from  $\sim 5.65$  GHz to  $\sim 4.8$  GHz. Since the slots interrupts the direct path of the current from edge to edge in the antenna, they have the effect of making the electrical path longer, and the antenna operating frequency shifts down. The matching also

decreases from -32 dB to -22 dB, but it can be adjusted back with a small shift in the feeding point.

The drawback is a small reduction in the efficiency from 96% to 92%, and a bandwidth reduction from 180 MHz to 90 MHz. However, depending on the antenna application, a smaller bandwidth can be a benefit.

After the determination of the implications of slots in the operating frequency it was analyzed its influence in the radiating properties.

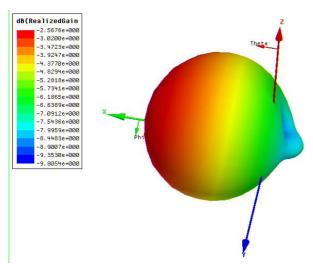

Fig. 4 displays the simulated 3D radiation diagram.

Fig. 4. Simulated 3D radiation pattern of the slotted antenna at 4.8 GHz.

The plot shows the radiation pattern at  $4.8\,\mathrm{GHz}$  because we are mainly interested in the properties of the new antenna with slots. This figure shows that the antenna radiation is mainly in the xx direction, which is due to the aperture formed by the ground plane and the top patch. Comparing this plot with the obtained for  $5.7\,\mathrm{GHz}$ , it was observed an increase of  $\sim\!2\,\mathrm{dB}$  in the antenna gain.

After verifying that the use of slots on the top patch is an effective way to change the operating frequency, it was analyzed how the slot length can be used to control the antennas operating frequency.

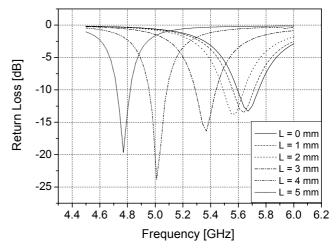

Fig. 5 shows the effect on the antenna operating frequency when the slot length, L, is varied from 1 mm to 5 mm, and compared to the situation without slots.

It is observed that longer slots reduce the operating frequency and the bandwidth. It was an expected behavior since the electrical length of the antenna increases when the slots are longer. For longer slots, the current has to go almost from one side of the antenna to the other, before reaching the radiating edge.

The next step was to verify how much the area could be reduced if the slotted antenna was modified to operate at 5.7 GHz. The longer slot option was used, since this is the solution to obtain the smallest antenna possible, and the antenna was redesigned. It was found that to move the operating frequency back to 5.7 GHz, the antenna size

could be reduced from 6x6 mm<sup>2</sup> to less than 5x5mm<sup>2</sup>.

This means that the final antenna uses only 70% of the initial area. The drawback is the decrease of the available bandwidth from 180 MHz to 120 MHz. But, as abovementioned, in some applications this can be a benefit.

Fig. 5. Simulated return loss for different slot lengths, L.

## B. Antenna Matching

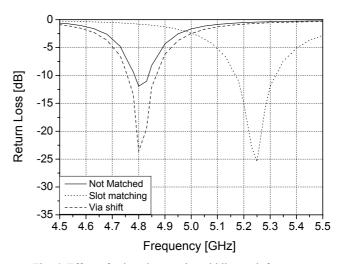

The placement of slots on the top patch, besides the operating frequency shift, introduces mismatch between antenna input and feed line. As already discussed, the frequency shift can be used for antenna tuning or for size reduction. The mismatch introduced by the slots can also be used as a way to perform the antenna matching. Instead of using a shift in the feeding via, the antenna can be matched with the use of a slot in the middle patch. Fig. 6 compares both methods of matching.

Fig. 6. Effect of using slots on the middle patch for antenna matching.

If the matching is achieved with a shift in the feeding via, it can be seen that the operating frequency remains unchanged while the matching is improved. If a slot is placed in the middle patch, the current distribution on that patch is modified and, consequently, the input impedance changes. Placing that slot in the proper

position, the antenna will be matched to the feeding line. The drawback of this technique is that it implies a frequency shift. However, this technique can be useful when a via shift is not enough to provide the necessary matching. That may be necessary if more slots are placed on the top patch to make the antenna electrically longer. That can make the antenna so inductive that it is not anymore possible to achieve matching.

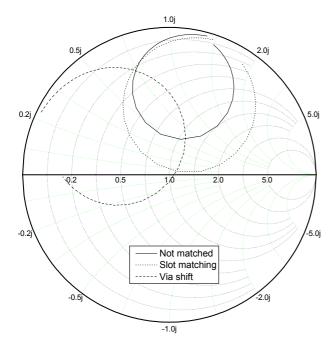

Fig. 7 shows, in a Smith diagram, how the input impedance changes when the two different solutions are used. If the antenna becomes too inductive, when shifting the feeding via, the input impedance changes. However, it remains in the top part of the Smith chart. One solution can be to use a slot in the middle patch.

Fig. 7. Effect of using slots on the middle patch for antenna matching.

# C. Antenna Reconfiguration

As shown in Fig. 5, when the length of the slots is changed, the operating frequency also changes. In this way, if a few switches can be used to control the length of those slots, it is possible to obtain a reconfigurable antenna.

The placement and control of such switches may not be an easy task, but one way to achieve this may be the use of MEMS switches. In previous work, series MEMS switches were combined with antenna sections, and used to obtain a reconfigurable multi-band antenna [8]. In the slotted-folded patch antenna, the MEMS switches would be used to change the electrical length of the top patch. When the switches are closed, the electrical path becomes smaller and the operating frequency shifts upward, and vice-versa.

### V. CONCLUSION

This work discusses a new option to design folded-patch antennas operating in the 5-6 GHz ISM band. The method consists of placing slots on the antenna top patch to control its electrical length. It is also shown how to use those slots to tune the operating frequency or to change the input impedance of a folded patch antenna. The use of this technique allows a reduction of the antenna area by a factor close to 30%.

With this option for antenna size reduction, the size increase due to the use of silicon-compatible substrates can now be compensated with this reduced size antenna. This offers potential of low cost, low profile and simplified assembly. A new step towards antenna integration in a RFIC chip for wireless short-range communications was given.

## ACKNOWLEDGEMENT

The authors wish to acknowledge the support by the Portuguese Foundation for Science and Technology (SFRH/BD/4717/ 2001, POCTI / ESE / 38468 / 2001, FEDER).

# REFERENCES

- [1] Chee-Yee Chong, Srikanta P. Kumar, "Sensor Netwoks: Evolution, Opportunities, and Challenges," *Proc. IEEE*, vol. 91, pp. 1247-1256, 2003.

- [2] Kin-Lu Wong, *Planar Antennas for Wireless Communications*, John Wiley & Sons, Inc., 2003.

- [3] A. Polyakov, P.M. Mendes, S.M. Sinaga, M. Bartek, B. Rejaei, J.H. Correia, J.N. Burghartz, "Processability and Electrical Characteristics of Glass Substrates for RF Wafer-Level Chip-Scale Packages", *in Proc.* 53<sup>rd</sup> ECTC, New Orleans, USA, 2003.

- [4] P.M. Mendes, S. M. Sinaga, A. Polyakov, M. Bartek, J.N. Burghartz, J. H. Correia, "Wafer-Level Integration of On-Chip Antennas and RF Passives Using High-Resistivity Polysilicon Substrate Technology", *In Proc.* 54<sup>th</sup> ECTC, Las Vegas, USA, 2004, pp. 1879 1884.

- [5] P. M. Mendes, A. Polyakov, M. Bartek, J. N. Burghartz, J. H. Correia, "Integrated 5.7 GHz Chip-Size Antenna for Wireless Sensor Networks," Transducers'03, Boston, USA, June 8-12, 2003, pp. 49-52.

- [6] R.L. Li, G. DeJean, E. Tsai, E. Tentzeris, J. Laskar, "Novel small folded shorted-patch antennas", *in Proc. Antennas and Propagation Soc. Int. Symp.*, vol. 4, 2002, pp. 26-29.

- [7] P.M. Mendes, A. Polyakov, M. Bartek, J.N. Burghartz, J. H. Correia, "Design of a Folded-Patch Chip-Size Antenna for Short-Range Communications," in 33rd Eur. Microwave Conf. Dig., Munich, Germany, Oct. 2003, pp. 723-726.

- [8] J. Kiriazi, H. Ghali, H. Ragaie, H. Haddara, "Reconfigurable dual-band dipole antenna on silicon using series MEMS switches", IEEE APS Symp., Vol. 1, pp. 403-406, 2003.