Adriano Dídimo Machado Carvalho

**Embedded-Systems-Oriented Virtualization Framework with Functionality Farming**

Adriano Didimo Machado Carvalho Embedded-Systems-Oriented Virtualization

Adriano Dídimo Machado Carvalho

# **Embedded-Systems-Oriented Virtualization Framework with Functionality Farming**

Tese de Doutoramento em Engenharia Electrónica e de Computadores

Trabalho realizado sob a orientação do

**Professor Doutor Adriano José Conceição Tavares** e do

**Professor Doutor Francisco Carlos Afonso**

## STATEMENT OF INTEGRITY

I hereby declare having conducted my thesis with integrity. I confirm that I have not used plagiarism or any form of falsification of results in the process of the thesis elaboration.

I further declare that I have fully acknowledged the Code of Ethical Conduct of the University of Minho.

University of Minho, Seplm Su 20th, 7016

Full name: Adriano Dídimo Machado Carvalho

Signature: Adviso C. Su. (40

# **Acknowledgments**

I would like to express my sincere gratitude to my adviser Prof. Adriano Tavares for the continuous support of my Ph.D. study and without which this work would not be possible.

I also would like to thank Prof. Francisco Afonso for his comments and encouragement throughout this work.

I would like to thank my Ph.D. proposal defense committee, Prof. Francisco Afonso, Prof. Jorge Cabral, Prof. João Cardoso and Prof. Júlio Martins, for their insightful comments and suggestions.

I would also like to thank everyone, family, colleagues and friends, who have accompanied me during this work, especially during my darkest hours.

My sincere thanks also goes to all of the developers of free and open source software for their dedication and, without which, this work (and many others) would not be possible.

This work has been supported by COMPETE: POCI-01-0145-FEDER-007043 and Fundação para a Ciência e Tecnologia within the Project Scope: UID/CEC/00319/2013. This work was also supported by Fundação para a Ciência e Tecnologia, grant SFRH/BD/81640/2011.

#### Resumo

Um: O uso de um hipervisor como *kernel* de separação em arquiteturas integradas está a ser considerado, visto que, um hipervisor não só proporciona separação temporal e espacial, mas também compatibilidade com software *legacy*. No entanto, nos dias de hoje, a maior parte dos hipervisores baseiam-se em paravirtualização ou dependem de hardware *high-end*; ambas as abordagens não cumprem os requisitos dos sistema embebidos críticos para a segurança. A paravirtualização, por um lado, não proporciona compatibilidade total com software *legacy*, sendo necessária a sua modificação e adaptação a uma interface especifica do hipervisor utilizado. Hardware *high-end*, por outro lado, apesar de proporcionar compatibilidade total com software *legacy*, dá origem a sistemas de grande dimensão, de elevado peso, com elevado consumo de energia, de elevado custo, etc. Nesta tese, a capacidade da virtualização completa em hardware *low-end* para resolver as limitações dos hipervisores existentes é investigada. Para isso, um hipervisor baseado em virtualização completa em hardware *low-end* é descrito e é apresentada uma avaliação da sua performance e do espaço ocupado em memória.

Dois: Métodos de desenvolvimentos convencionais não são capazes de acompanhar os requisitos dos sistemas embebidos críticos para segurança de hoje em dia. Nesta tese: (a) é apresentada uma abordagem baseada em modelos já existente, mais especificamente, geração de código baseada em modelos; (b) são descritas as modificações aplicadas a um compilador de modelos já existente por forma a que este suporte novas capacidades; e (c) é apresentada uma avaliação sobre a capacidade da geração de código baseada em modelos de reduzir o esforço de engenharia quando comparada com abordagens convencionais.

Três: A maior parte dos sistemas operativos de hoje em dia seguem uma arquitetura monolítica; esta arquitetura, no entanto, está associada a fraca confiabilidade, baixa segurança, esforço de certificação elevado, bem como baixa previsibilidade e escalabilidade. Para colmatar estes problemas, as soluções propostas na literatura apenas contornam a origem do problema, i.e., a elevada dimensão do *kernel* numa arquitetura monolítica, e não o resolvem diretamente. Nesta tese, *functionality farming* é proposto para atacar a origem do problema. *Functionality farming* apenas, no entanto, depende de um esforço de engenharia significativo. Visto isto, esta tese também apresenta FF-AUTO, uma ferramenta capaz de realizar *functionality farming* de forma semi-automática. Por último, esta tese demonstra como *functionality farming* é capaz de melhorar o design e a performance de um *kernel* já existente, e demonstra também como FF-AUTO permite uma redução significativa do esforço de engenharia.

## **Abstract**

First, the use of a hypervisor as the separation kernel on integrated architectures has been considered, as it not only provides time and space partitioning, but it also provides compatibility with legacy software. Nowadays, most hypervisors, however, either rely on paravirtualization or depend on high-end hardware, both of which do not fulfill the requirements of safety-critical embedded systems. Paravirtualization does not provide complete legacy compatibility as it requires legacy software to be modified to fit a hypervisor-specific interface. High-end hardware, on the other hand, even though it provides complete legacy compatibility, it leads to large system size, weight, power consumption, cost, etc. In this thesis, the feasibility of low-end hardware full virtualization to address the limitations of existing hypervisors is investigated. For that, a hypervisor based on low-end hardware full virtualization is described and an evaluation of its performance and footprint is presented.

Second, conventional development methods are unable to keep up with the requirements of nowadays and future safety-critical embedded systems. In this thesis: (a) an existing model-driven engineering approach to address the limitations of conventional development methods is presented; more specifically, a model-driven code generation approach; (b) the modifications applied to an existing model compiler in order for it to support new features are described; and (c) an evaluation of whether or not a model-driven code generation approach leads to lower engineering effort when compared to a conventional approach is presented.

Third, most operating systems, nowadays, follow a monolithic architecture; this, however, leads to poor reliability, weak security, high certification effort, as well as poor predictability and scalability. To address this problem, the solutions proposed in the literature just work around the source of the problem, i.e., the large size of the kernel in a monolithic architecture, and do not address it directly. In this thesis, functionality farming is proposed to tackle the source of the problem. Functionality farming alone, however, depends on a significant engineering effort. To address this problem, this thesis also presents FF-AUTO, a tool which performs functionality farming semi-automatically. At last, this thesis demonstrates how functionality farming is able to improve the design and the performance of an existing kernel, as well as how FF-AUTO enables a significant reduction of the required engineering effort.

# **Table of Contents**

| Acknowledgments                             | v   |

|---------------------------------------------|-----|

| Resumo                                      | vii |

| Abstract                                    | ix  |

| Table of Contents                           | xi  |

| Figures                                     | XV  |

| Tables                                      | xix |

| Listings                                    | xxi |

| 1.Introduction                              | 1   |

| 1.1.Full Virtualization on Low-End Hardware | 1   |

| 1.2.Model-Driven Engineering                | 6   |

| 1.3.Functionality Farming                   | 8   |

| 1.4.Thesis Structure                        | 11  |

| 1.5.Publications                            | 12  |

| 2.Rodosvisor                                | 13  |

| 2.1.Introduction                            | 13  |

| 2.1.1.Chapter Organization                  | 14  |

| 2.2.Virtualization and Hypervisors          | 15  |

| 2.3.Interface with the Host                 | 18  |

| 2.4.Full Virtualization                     | 20  |

| 2.4.1.Instruction Set                       | 20  |

| 2.4.2.Timers                                | 23  |

| 2.4.2.1.PIT                                 | 25  |

| 2.4.2.2.TSR                                 | 29  |

| 2.4.2.3.TCR                                 | 30  |

| 2.4.2.4.Interrupts                          | 31  |

| 2.4.2.5.Preemption                          | 33  |

| 2.4.3.Memory Management Unit                | 33  |

| 2.4.3.1.PowerPC 405 Memory Management Unit  | 33  |

| 2.4.3.2.Overview                            | 38  |

| 2.4.3.3.Real Mode Translation               | 41  |

|---------------------------------------------|-----|

| 2.4.3.4.Virtual Mode Translation            | 45  |

| 2.4.4.Interrupts                            | 48  |

| 2.5.I/O virtualization                      | 49  |

| 2.6.Paravirtualization                      | 52  |

| 2.7.Future Work                             | 53  |

| 2.8.Summary                                 | 54  |

| 3.POK/rodosvisor                            | 57  |

| 3.1.Introduction                            | 57  |

| 3.1.1.Chapter Organization                  | 58  |

| 3.2.ARINC 653                               | 58  |

| 3.3.Privileged Partitions                   | 63  |

| 3.4.POK and Rodosvisor Integration          | 70  |

| 3.5.Evaluation                              | 75  |

| 3.5.1.Evaluation Platform                   | 75  |

| 3.5.2.Cumulative Virtualization Overhead    | 79  |

| 3.5.3.Hypervisor's Performance Profile      | 82  |

| 3.5.4.Footprint.                            | 84  |

| 3.5.4.1.Trusted Computing Base              | 84  |

| 3.5.4.2.Memory Footprint                    | 86  |

| 3.6.Future Work                             | 92  |

| 3.7.Summary                                 | 92  |

| 4.Model-Driven Engineering using Ocarina    | 95  |

| 4.1.Introduction                            | 95  |

| 4.1.1.Chapter Organization                  | 95  |

| 4.2.Development Methods: State of the Art   | 96  |

| 4.2.1.Computer-Aided Software Engineering   | 96  |

| 4.2.2.Component-Based Software Engineering  | 97  |

| 4.2.3.Software Product Line Engineering.    | 98  |

| 4.2.4.Model-Driven Engineering              | 99  |

| 4.3.Architecture Analysis & Design Language | 101 |

| 4.4.Ocarina                                 | 107 |

| 4.5.Privileged Partitions                   | 109 |

| 4.6.Virtual Machines                                  | 114 |

|-------------------------------------------------------|-----|

| 4.7.Evaluation                                        | 117 |

| 4.8.Future Work                                       | 119 |

| 4.9.Summary                                           | 119 |

| 5.Functionality Farming                               | 121 |

| 5.1.Introduction                                      | 121 |

| 5.1.1.Chapter Organization                            | 123 |

| 5.2.Related Work                                      | 123 |

| 5.3.Functionality Farming Automated: ff-auto          | 125 |

| 5.3.1.Functionality Farming Configuration File        | 126 |

| 5.3.2.Function Call Farming and Complete Farming      | 128 |

| 5.3.3.Workers and Worker Threads                      | 129 |

| 5.3.4.Function Call Wrappers and Unwrappers           | 130 |

| 5.4.Use Case: Serial Port Device Driver               | 132 |

| 5.5.Use Case: Inter-Partition Communication Subsystem | 137 |

| 5.6.Future Work                                       | 142 |

| 5.7.Summary                                           | 143 |

| 6.Conclusion.                                         | 145 |

| 6.1.Full Virtualization on Low-End Hardware           | 145 |

| 6.2.Model-Driven Engineering                          | 146 |

| 6.3.Functionality Farming                             | 146 |

| Bibliography                                          | 149 |

# **Figures**

| Figure 1.1. Illustration of a federated architecture                                             | 3      |

|--------------------------------------------------------------------------------------------------|--------|

| Figure 1.2. Illustration of an integrated architecture                                           | 4      |

| Figure 1.3. Illustration of (a) a separation kernel vs. (b) a hypervisor                         | 5      |

| Figure 1.4. Illustration of functionality farming: (a) before functionality farming; (b) after   |        |

| functionality farming                                                                            | 9      |

| Figure 2.1. Illustration of (a) a separation kernel vs. (b) a hypervisor                         | 15     |

| Figure 2.2. Hypervisor types: (a) bare metal, (b) hosted, and (c) type 1.5                       | 18     |

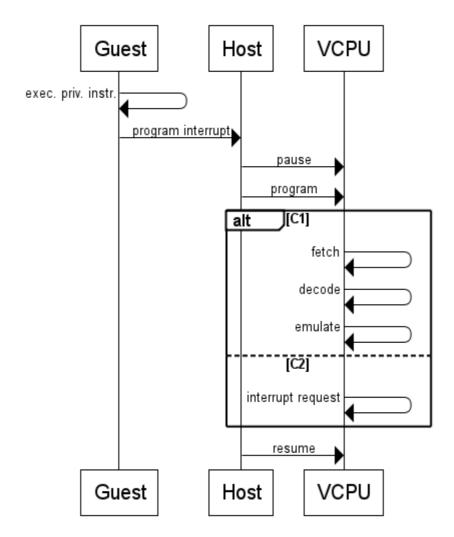

| Figure 2.3. Illustration of the interaction between the host, the VCPU and the guest             | 19     |

| Figure 2.4. A sequence diagram illustrating how the PowerPC 405 handles the user and privileg    | ged    |

| instruction subsets when in the user and privileged modes                                        | 21     |

| Figure 2.5. A sequence diagram illustrating how emulation of privileged instructions is          |        |

| accomplished                                                                                     | 22     |

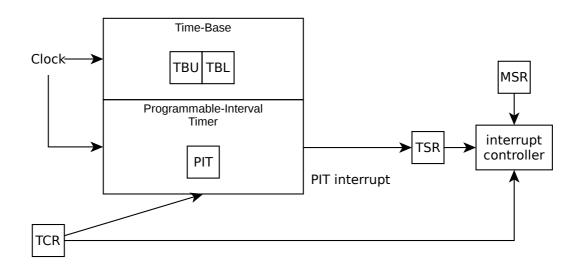

| Figure 2.6. The Time Base and the Programmable-Interval Timer in the PowerPC 405                 | 23     |

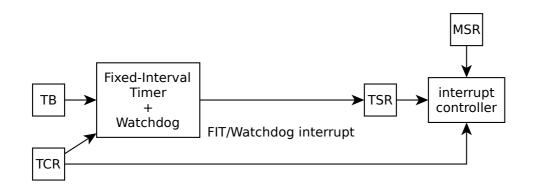

| Figure 2.7. The Fixed-Interval Timer and the Watchdog in the PowerPC 405                         | 24     |

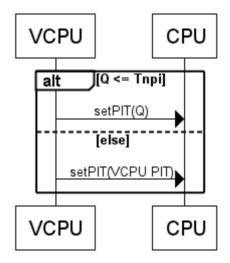

| Figure 2.8. A sequence diagram illustrating the configuration of the CPU's PIT with either (1) t | he     |

| time until the end of the partition window (a.k.a., the quantum, or Q), or (2) the               |        |

| VCPU's time until the next PIT interrupt (Tnpi)                                                  | 26     |

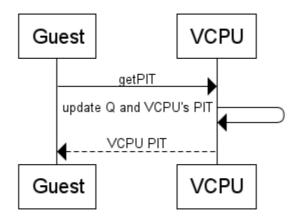

| Figure 2.9. VCPU operation when a guest requests the value of the VCPU's PIT                     | 28     |

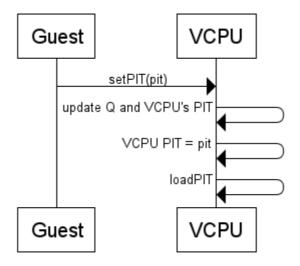

| Figure 2.10. VCPU operation when a guest requests a change to the value of the VCPU's PIT        | 28     |

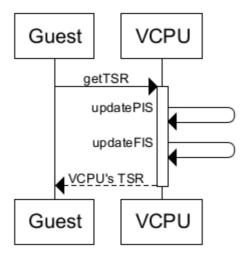

| Figure 2.11. VCPU operation when a guest requests the value of the VCPU's TSR                    | 29     |

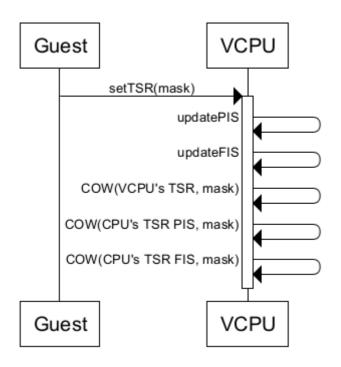

| Figure 2.12. VCPU operation when a guest writes to the VCPU's TSR                                | 30     |

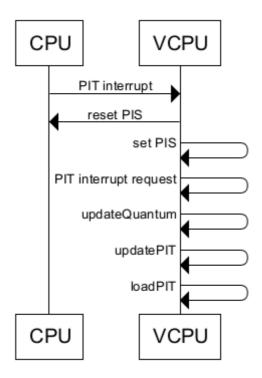

| Figure 2.13. VCPU operation when there is a CPU PIT interrupt and the system is in state P2      | 32     |

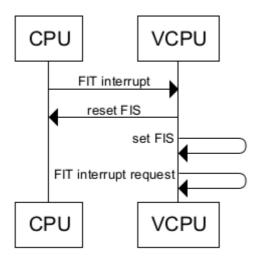

| Figure 2.14. VCPU operation when there is a CPU FIT interrupt                                    | 33     |

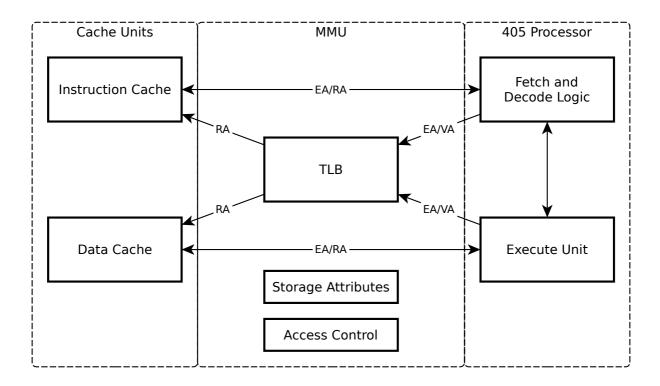

| Figure 2.15. The logical connections between the cache units, the memory management unit are     | ıd the |

| 405 processor within a PowerPC 405                                                               | 34     |

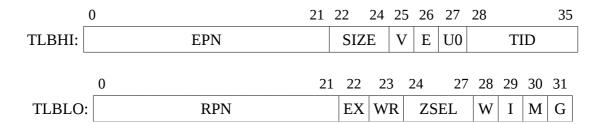

| Figure 2.16. TLBHI and TLBLO                                                                     | 35     |

| Figure 2.17. Handling of a change to the VCPU's real mode configuration                          | 39     |

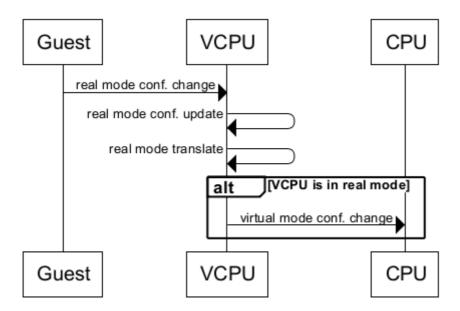

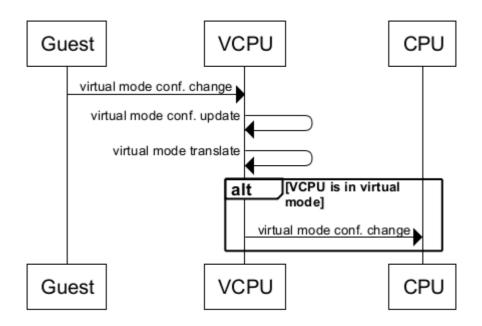

| Figure 2.18. Handling of a change to the VCPU's virtual mode configuration                       | 40     |

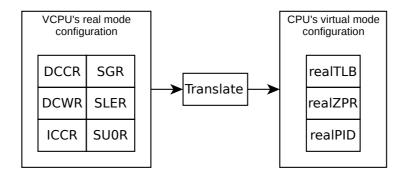

| Figure 2.19. Translation between the VCPU's real mode configuration and the CPU's virtual mode.  | ode    |

| configuration                                                                                    | 41     |

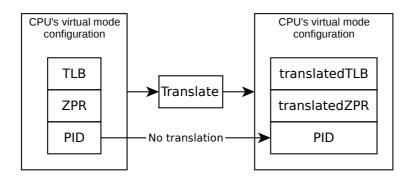

| Figure 2.20. Translation between the VCPU's virtual mode configuration and the CPU's virtual     |        |

| mode configuration                                                                               | 45     |

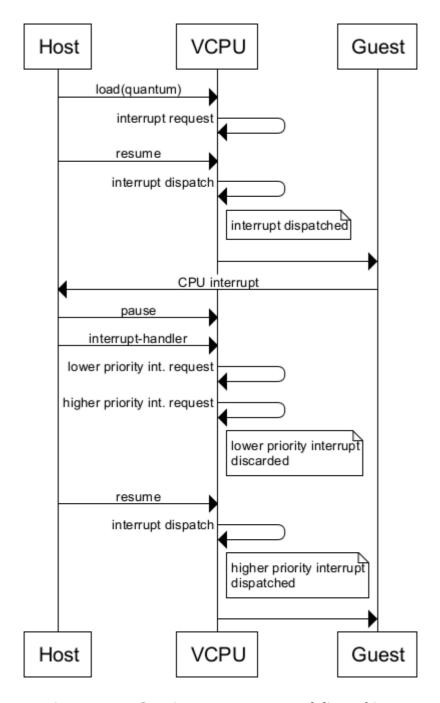

| Figure 2.21. VCPU interrupt requests and dispatching                                                              | 49      |

|-------------------------------------------------------------------------------------------------------------------|---------|

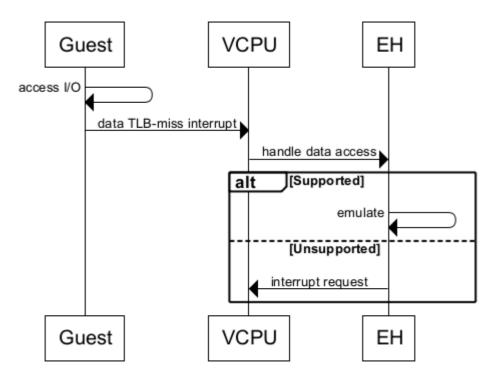

| Figure 2.22. Supervised memory-mapped I/O                                                                         | 51      |

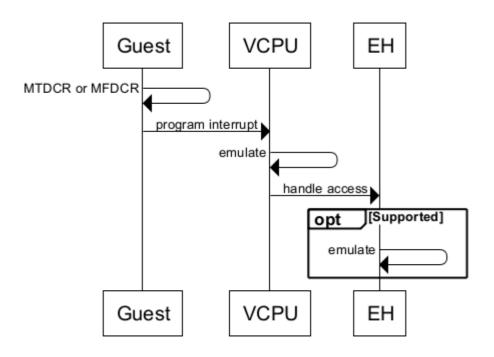

| Figure 2.23. Supervised DCR-mapped I/O                                                                            | 52      |

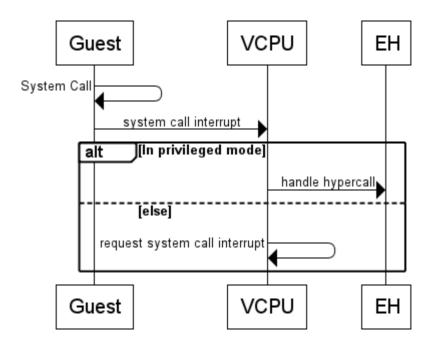

| Figure 2.24. Sequence diagram illustrating hypercall detection based on the system call interru                   | .pt53   |

| Figure 3.1. ARINC 653 software architecture                                                                       | 59      |

| Figure 3.2. ARINC 653 major and minor frames                                                                      | 60      |

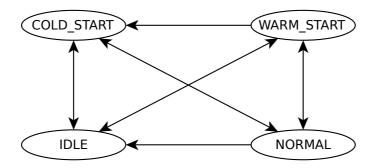

| Figure 3.3. ARINC 653 partition's operating modes                                                                 | 61      |

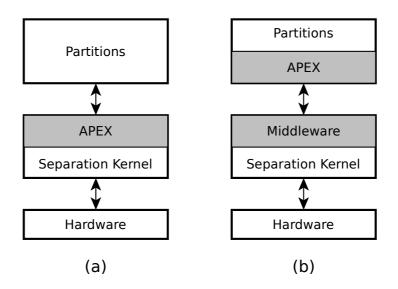

| Figure 3.4. Implementation of the APEX: (a) implemented in the separation kernel, (b) implementation of the APEX: | nented  |

| by partitions based on the separation kernel's middleware                                                         | 62      |

| Figure 3.5. Comparison between (a) ARINC 653 partitions and (b) privileged partitions                             | 64      |

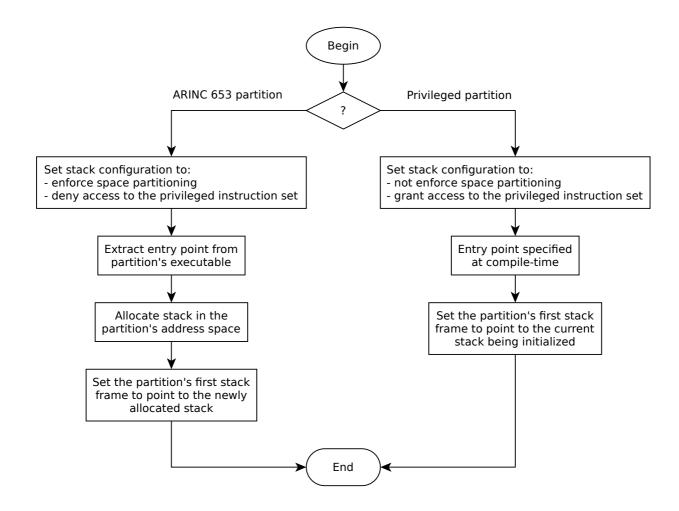

| Figure 3.6. Initialization process of a thread's stack for an ARINC 653 or privileged partition                   | 65      |

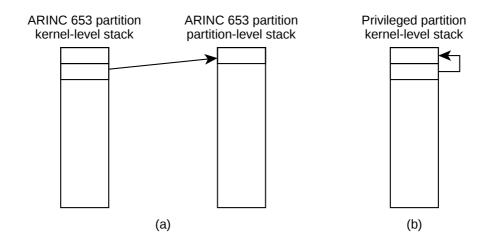

| Figure 3.7. Stacks required (a) by an ARINC 653 partition and (b) by a privileged partition                       | 66      |

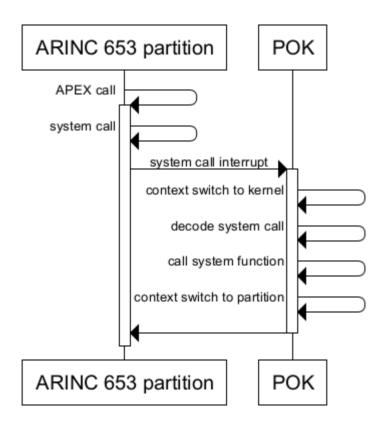

| Figure 3.8. An APEX call by an ARINC 653 partition                                                                | 67      |

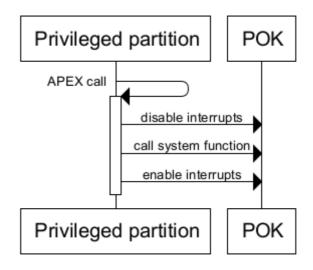

| Figure 3.9. An APEX call by a privileged partition                                                                | 68      |

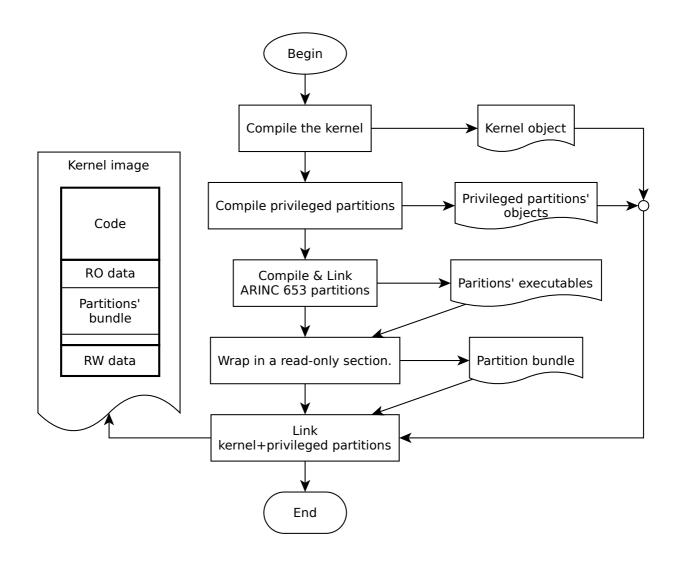

| Figure 3.10. POK/rodosvisor compilation process                                                                   | 69      |

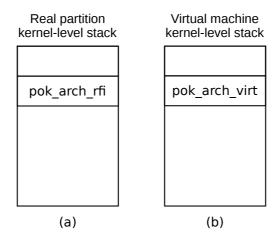

| Figure 3.11. Kernel-level stack (a) for a real partition and (b) for a virtual machine                            | 71      |

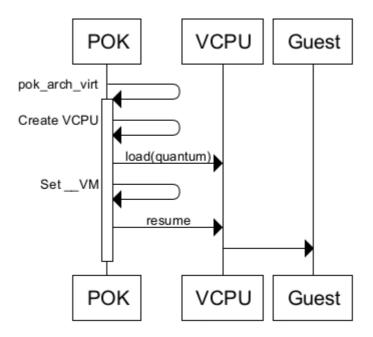

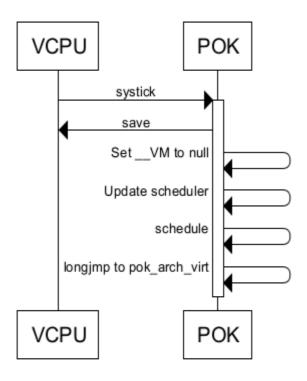

| Figure 3.12. Sequence diagram for "pok_arch_virt" in POK/rodosvisor                                               | 72      |

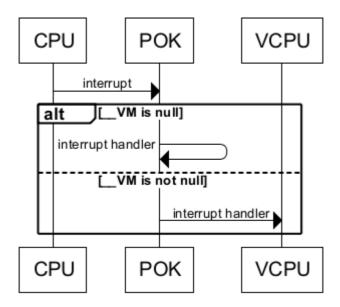

| Figure 3.13. Interrupt handling in POK/rodosvisor                                                                 | 73      |

| Figure 3.14. Sequence diagram for POK/rodosvisor's systick                                                        | 74      |

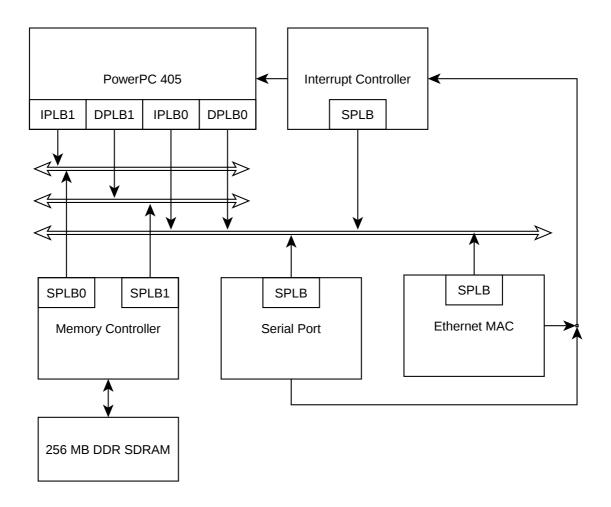

| Figure 3.15. Hardware architecture of the evaluation platform.                                                    | 76      |

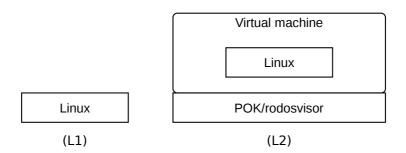

| Figure 3.16. Configurations (L1) and (L2).                                                                        | 79      |

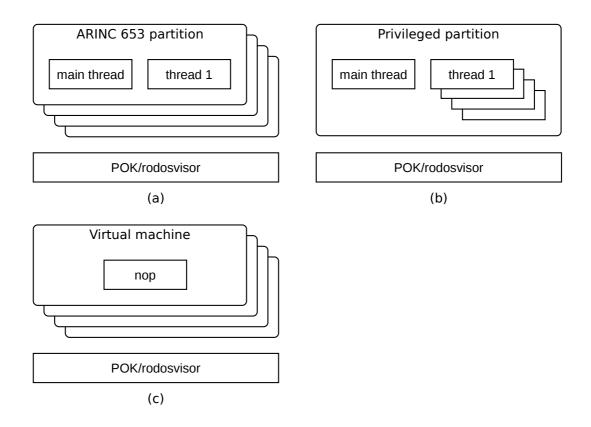

| Figure 3.17. Configurations based on (a) ARINC 653 partitions, (b) a privileged partition, and                    | (c)     |

| virtual machines                                                                                                  | 87      |

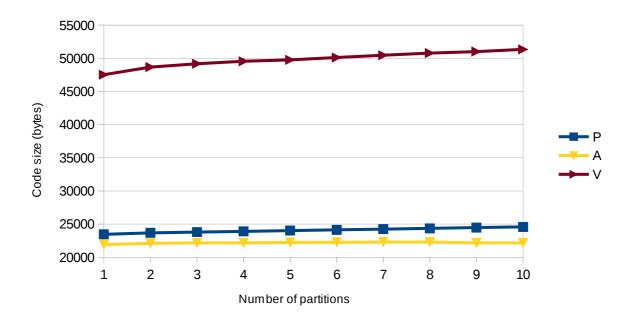

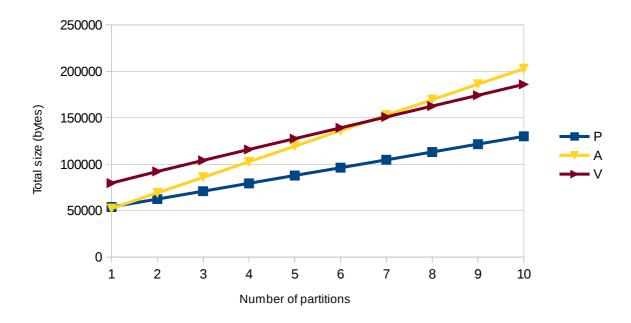

| Figure 3.18. Code size for all configurations                                                                     | 88      |

| Figure 3.19. Read-only data size for all configurations. When there is only one ARINC 653                         |         |

| partition, the size of read-only data is zero (data point not shown)                                              | 89      |

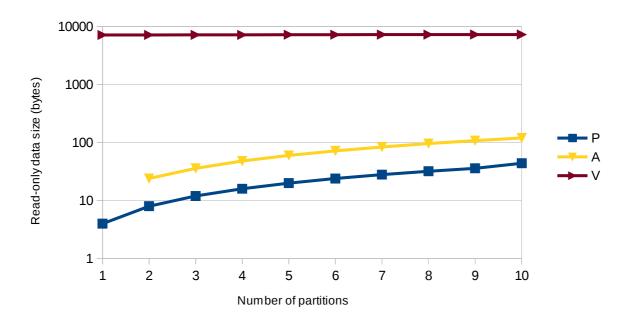

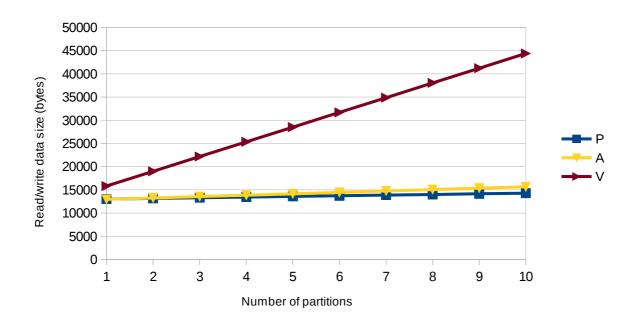

| Figure 3.20. Size of read/write data for all configurations                                                       | 89      |

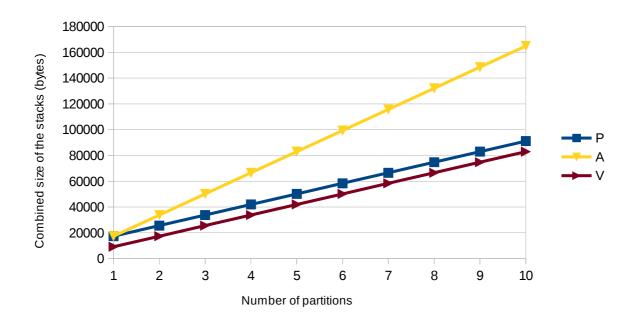

| Figure 3.21. Combined size of all stacks for all configurations                                                   | 91      |

| Figure 3.22. Combined size of (1) the code, (2) read-only and (3) read/write data, and (4) the                    |         |

| combined size of all stacks, for all configurations                                                               | 91      |

| Figure 4.1. Domain and application engineering in SPLE (adapted from [124])                                       | 99      |

| Figure 4.2. Standard AADL graphical representation of the model in Listing 4.1 and Listing 4.                     | .2. 104 |

| Figure 4.3. Standard AADL graphical representation for some AADL components                                       | 105     |

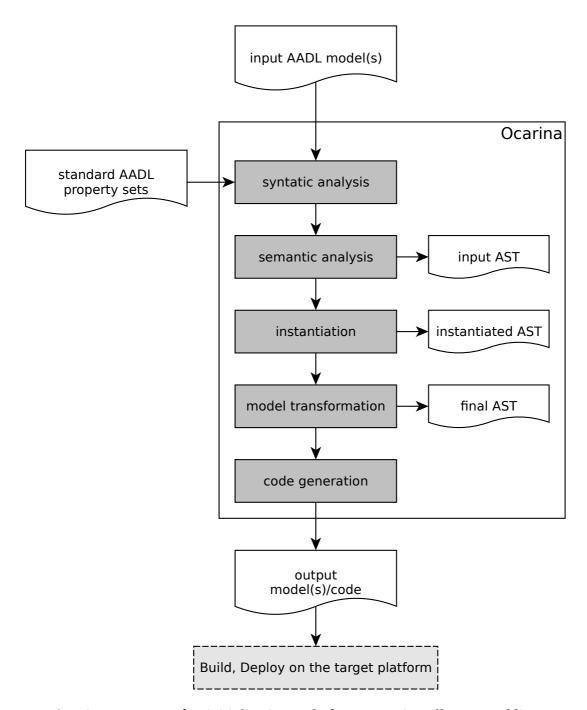

| Figure 4.4. Ocarina's process after initialization and after processing all command line argume                   | ents.   |

| 108                                                                                                     |

|---------------------------------------------------------------------------------------------------------|

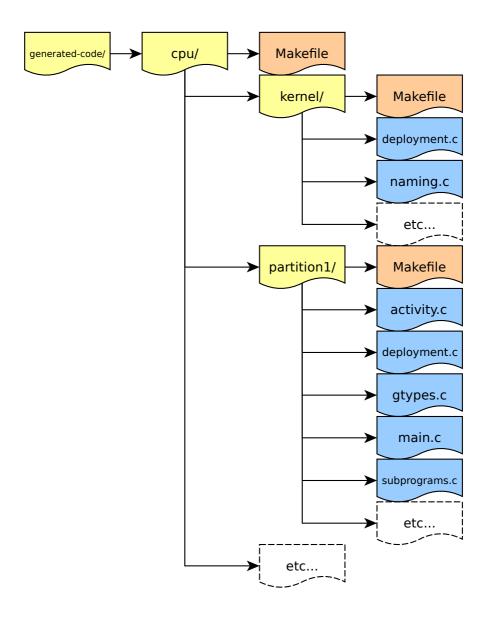

| Figure 4.5. An example on how the final AST can be stored in the file system. Example based on          |

| Ocarina's POK back-end109                                                                               |

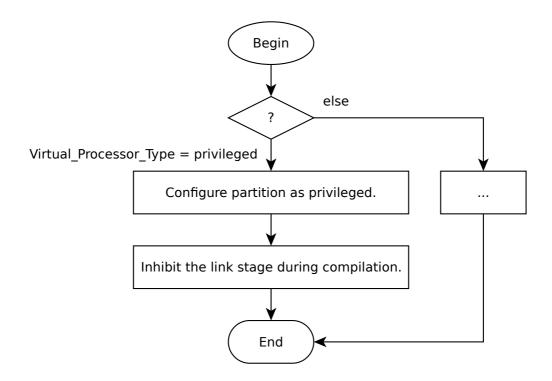

| Figure 4.6. Ocarina's modified operation during partition's code generation112                          |

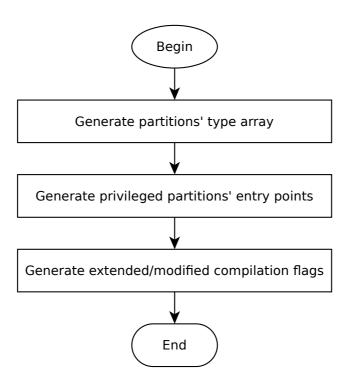

| Figure 4.7. Ocarina's modified operation, required by privileged partitions, when generating code       |

| for the kernel113                                                                                       |

| Figure 4.8. Ocarina's modified operation, required by virtual machines, when generating code for        |

| the kernel116                                                                                           |

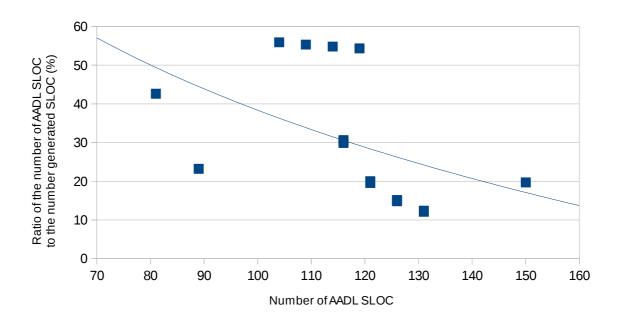

| Figure 4.9. The ratio of the number of AADL SLOC to the number of generated SLOC in relation to         |

| the number of AADL SLOC119                                                                              |

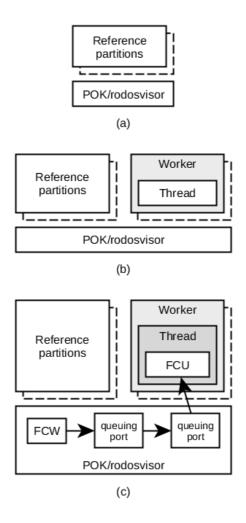

| Figure 5.1. Inputs and outputs of ff-auto                                                               |

| Figure 5.2. Illustration of the transformations applied to the reference configuration by ff-auto: (a)  |

| the reference configuration; (b) workers and worker threads added to the reference                      |

| configuration; (c) FCW, FCU, and associated communication channels added to the                         |

| reference configuration                                                                                 |

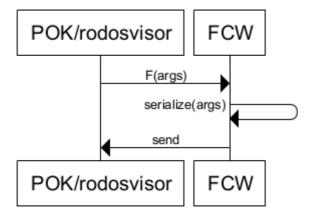

| Figure 5.3. Sequence diagram of a generic function call wrapper (FCW)130                                |

| Figure 5.4. Sequence diagram of a generic function call unwrapper (FCU)131                              |

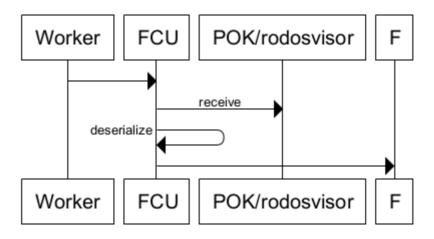

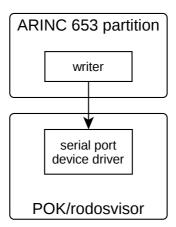

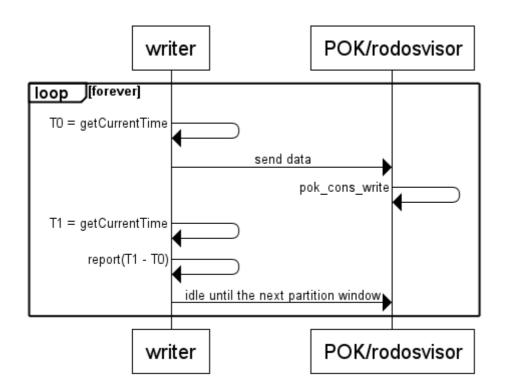

| Figure 5.5. The reference architecture used for the serial port device driver's use case: an ARINC      |

| 653 partition which sends data through the serial port                                                  |

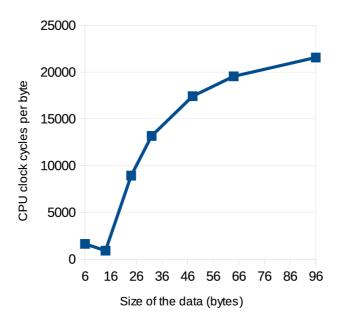

| Figure 5.6. A sequence diagram illustrating the process performed by the writer in the serial port      |

| device driver's use case                                                                                |

| Figure 5.7. The average number of CPU clock cycles per byte required to send data to the serial port    |

| for different sizes of data for the reference configuration134                                          |

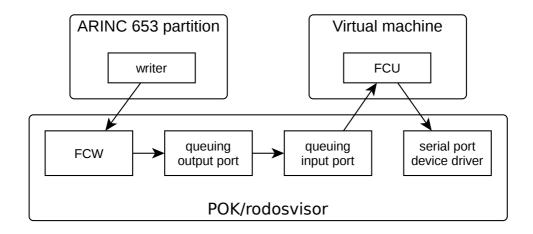

| Figure 5.8. The resulting architecture for configuration VM on the serial port device driver's use      |

| case135                                                                                                 |

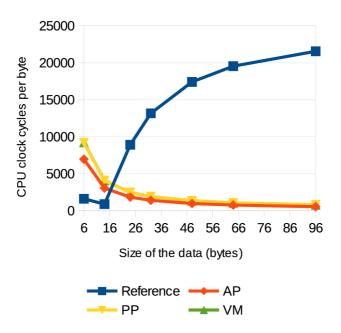

| Figure 5.9. Comparison of the average number of CPU clock cycles per byte required to send data         |

| to the serial port for different sizes of data between the reference configuration and                  |

| after functionality farming. "VM" is barely seen because it is overlapped by "PP."136                   |

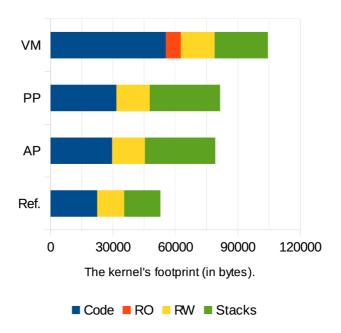

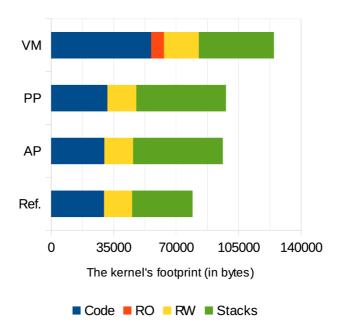

| Figure 5.10. The kernel's footprint for the reference and all the modified configurations in the serial |

| port device driver's use case, in terms of the size of the code, read-only (RO) and read-               |

| write (RW) data, as well as the size of the stacks137                                                   |

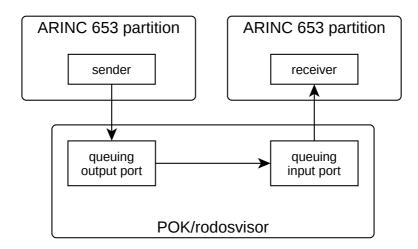

| Figure 5.11. The reference architecture used in the inter-partition communication subsystem's use       |

| case: two ARINC 653 partitions communicating through a queuing channel138                               |

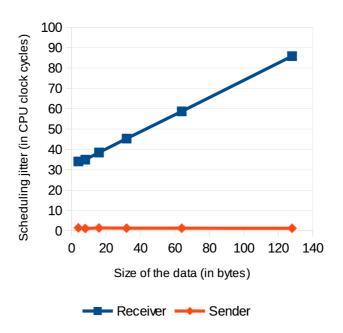

| Figure 5.12. The average scheduling jitter for the "receiver" and the "sender."                         |

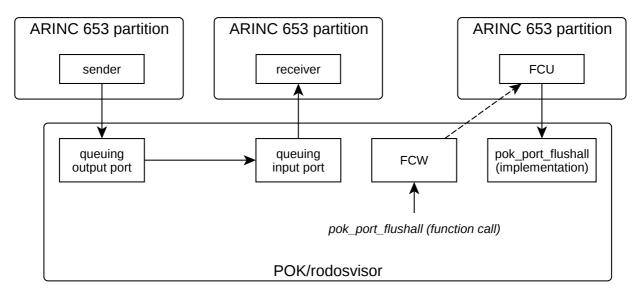

| Figure 5.13. | The resulting architecture for configuration AP on the inter-partition communication       |

|--------------|--------------------------------------------------------------------------------------------|

|              | subsystem's use case                                                                       |

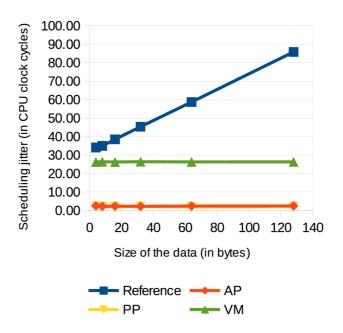

| Figure 5.14. | The average scheduling jitter for the first partition in the major frame on the reference  |

|              | and all the modified configurations. "PP" is barely seen as it is overlapped by "AP."      |

|              | 141                                                                                        |

| Figure 5.15. | The kernel's footprint for the reference and all the modified configurations in the inter- |

|              | partition communication subsystem's use case, in terms of the size of the code, read-      |

|              | only (RO) and read-write (RW) data, as well as the size of the stacks                      |

# **Tables**

| Table 2.1. Comparison of existing hypervisors in terms of low-end hardware full virtualization (LH-    |

|--------------------------------------------------------------------------------------------------------|

| FV), high-end hardware full virtualization (HH-FV), and paravirtualization (PV)1                       |

| Table 2.2. Setting of the CPU's TCR based on the VCPU state3                                           |

| Table 2.3. The bit fields in a TLB entry controlling address translation3                              |

| Table 2.4. Bit fields in a SPR controlling a real mode storage attribute and the corresponding 128     |

| MB sections of the real address space affected (big-endian notation)30                                 |

| Table 2.5. Access control and its configuration in virtual mode                                        |

| Table 2.6. Bit fields in the Zone Protection Register and their effect in user and privileged modes. 3 |

| Table 2.7. Storage attributes, and their configuration in real mode and virtual mode3                  |

| Table 2.8. Translation between the VCPU's real mode configuration and the CPU's TLB (i.e.,             |

| realTLB)4                                                                                              |

| Table 2.9. Translation between the VCPU's real mode configuration and the CPU's PID and ZPR            |

| (i.e., realPID and realZPR)4                                                                           |

| Table 2.10. Translation between the VCPU's ICCR and DCCR, and the I bit field in the CPU's TLB         |

| 4                                                                                                      |

| Table 2.11. Translation of the VCPU's TLB to the CPU's TLB (i.e., the translatedTLB)4                  |

| Table 2.12. Translation of the VCPU's PID and ZPR to the CPU's PID and ZPR4                            |

| Table 2.13. Translation of the VCPU's ZN (ZPR)                                                         |

| Table 3.1. The number of new and modified source lines of code (SLOC), and an estimation of the        |

| development effort, schedule, number of developers and cost, required in order to add                  |

| support for privileged partitions to POK                                                               |

| Table 3.2. The number of new and modified source lines of code (SLOC), and an estimation of the        |

| development effort, schedule, number of developers and cost, needed for the                            |

| integration of Rodosvisor with POK                                                                     |

| Table 3.3. Features of the Virtex-II Pro (XC2VP30)                                                     |

| Table 3.4. The results of several benchmarks, performed on top of a Linux-based operating system,      |

| running on bare metal (i.e., L1), or as a guest on POK/rodosvisor (i.e., L2). For each                 |

| benchmark, the associated virtualization overhead, in percentage, and its type are also                |

| shown8                                                                                                 |

| Table 3.5. The number of samples, the average and the total execution times per probe. Execution       |

| times are given in CPU clock cycles. In parenthesis, the ratio to the summation of all                 |

| the values in the same column is given, in percentage                                                  |

| Table 3.6. Rodosvisor's trusted computing base in terms of source lines of code (SLOC), and an   |

|--------------------------------------------------------------------------------------------------|

| estimate of the respective development effort, schedule, number of developers and                |

| total cost85                                                                                     |

| Table 3.7. POK/rodosvisor's trusted computing base in terms of source lines of code (SLOC), and  |

| an estimate of the respective development effort, schedule, number of developers and             |

| total cost86                                                                                     |

| Table 4.1. The number of new and modified source lines of code (SLOC), and an estimation of the  |

| development effort, schedule, number of developers and cost [81], required in order to           |

| add support for privileged partition to Ocarina114                                               |

| Table 4.2. The number of new and modified source lines of code (SLOC), and an estimation of the  |

| development effort, schedule, number of developers and cost [81], required in order to           |

| add support for virtual machines to Ocarina117                                                   |

| Table 4.3. For all configuration developed for this thesis: (1) the number of AADL SLOC, (2) the |

| number of generated SLOC, and (3) the ratio of the number of AADL SLOC to the                    |

| number of generated SLOC. The first and second columns represent, respectively: (1)              |

| the section where the configuration has been mentioned, and (2) the reference name of            |

| the configuration118                                                                             |

# Listings

| Listing 2.1. Pseudo-code illustration of the procedure used to update the quantum and the VCP   | U's    |

|-------------------------------------------------------------------------------------------------|--------|

| PIT                                                                                             | 27     |

| Listing 4.1. An example of an AADL model (continued in Listing 4.2)                             | 102    |

| Listing 4.2. An example of an AADL model (continuation of Listing 4.1)                          | 103    |

| Listing 4.3. Representation of a generic partition in AADL                                      | 110    |

| Listing 4.4. Code added to POK's AADL property set in order to support privileged partitions    |        |

| through the new Virtual_Processor_Type property                                                 | 110    |

| Listing 4.5. Sample usage of the Virtual_Processor_Type property: the virtual processor named   | l      |

| "partition_1" is an ARINC 653 partition and "partition_2" is a privileged partition             | ı. 111 |

| Listing 4.6. Code added to POK's AADL property set in order to support virtual machines through | ugh    |

| the new Virtual_Processor_Type property                                                         | 115    |

| Listing 4.7. Sample usage of the Virtual_Processor_Type property: the virtual processor named   | Ĺ      |

| "partition_1" is an ARINC 653 partition, and "partition_3" is a virtual machine                 | 115    |

| Listing 5.1. A functionality farming configuration file                                         | 126    |

| Listing 5.2. An incomplete AADL model                                                           | 127    |

| Listing 5.3. FFC file for farming "pok_cons_write" on a worker based on a virtual machine       | 135    |

| Listing 5.4. FFC file for farming "pok_port_flushall" on a worker based on an ARINC 653         |        |

| partition                                                                                       | 140    |

## 1. Introduction

#### 1.1. Full Virtualization on Low-End Hardware

A system is safety-critical if its failure can cause harm to people or the environment [1]. Such a failure is also known as a catastrophic failure. In a safety-critical system a missed deadline can result in a catastrophic failure, and thus, a safety-critical system is also a hard real-time system. Examples of safety-critical systems include: commercial and military aircraft, automobiles, traffic lights at an intersection, nuclear power plants, medical devices and implants, among many others. Within the domain of safety-critical systems, this thesis focuses on the sub-domain of safety-critical embedded systems. Safety-critical embedded systems can be distinguished from other computer systems by especially tight constrains along many axes, including:

- Size, volume, and weight: embedded systems, as the name suggests, are embedded in larger electrical, mechanical or hydraulic systems, and thus, are constrained to the physical characteristics of a larger system in which they are embedded.

- Power consumption: in many cases, a connection to a continuous power supply is not

possible and embedded systems must rely on batteries; therefore, it becomes critical to

reduce power consumption in order to extend battery-life, reduce maintenance, and thus,

increase availability.

- Cost: embedded systems are often mass produced and reducing their manufacturing cost is

critical for profit. In terms of the software, certification, when required, is the most costly

development activity and it is critical to reduce its impact. In terms of hardware, memory is

usually the most expensive resource, and thus, reducing the software's memory footprint is

also important.

In order to assure that a safety-critical system is unlikely to fail (it is not feasible to assure that a system will never fail), it must be certified by a third party before being deployed for its intended application. **IEC** 61508 [2], for example, is a standard "applicable all electrical/electronic/programmable electronic safety-related systems irrespective of the application." Similar standards include: DO-178 [3], specific to airborne systems, ISO 26262 [4], for road vehicles, and ISO 62304 [5], for medical devices. In IEC 61508, systems are classified according to a Safety Integrity Level (SIL) depending on the consequences of failure (i.e., "multiple loss of life" down to "minor injuries at worst") and their likelihood (i.e., "frequent" down to "improbable" and "incredible"); the higher the SIL, the more safety-critical the system is. Certification may require

specific development methods to be followed, such as extensive testing of the hardware and the software; the higher the SIL, the more rigorous the certification process. In IEC 61508, systems classified as SIL 1 (the lowest) can be developed according to quality management standards, such as ISO 9001 [6]. A system classified as SIL 4 (the highest), on the other end, needs to be verified and validated using formal methods and redundancy is mandatory. It is well known that certification of safety-critical systems is a difficult, time consuming and expensive activity, and that it can take up to seven times longer than other development activities [7].

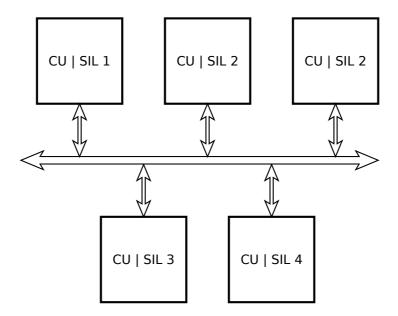

Traditional large-scale safety-critical systems follow a federated architecture [8]–[10], illustrated in Figure 1.1. In a federated architecture, a system is composed of multiple computing units ("CU" in Figure 1.1) connected to one or more buses; each computing unit is assigned with a single, independently developed function. Although providing strong fault containment and isolation between functions through physical separation, a federated architecture, however, has the following disadvantages [8]–[10]:

- a long bill of materials, which leads to large size and volume, high weight, high power consumption, and high cost;

- lack of common line replaceable units, and thus, high maintenance, repair and overhaul costs, as well as obsolescence problems;

- high hardware development and hardware certification effort, and thus, long time to market and high cost;

- high hardware fault rate, low reliability, low availability, and therefore, high maintenance cost;

- few organizations are able to support the life-time costs of the system, leading to a small market and low profit.

Figure 1.1. Illustration of a federated architecture.

A federated architecture may be well suited for small-scale safety-critical embedded systems with a small number of functions; however, a federated architecture does not scale well for large-scale systems, and it is not adequate for highly-constrained safety-critical embedded systems, especially when the demand for more functions is already high and increasing (e.g., autonomous vehicles).

To address the issues with the federated architecture, integrated architectures have been developed. Examples include: the integrated modular avionics architecture from the avionics industry [11], AUTomotive Open System ARchitecture (AUTOSAR) from the automotive industry [12], and the integrated time-triggered architecture (DECOS) from academia [13]. Similarly to a federated architecture, in an integrated architecture the system is composed by multiple computing units connected to one or more buses. However, in an integrated architecture, each computing unit may be assigned with multiple, independently developed functions with different SIL, as illustrated in Figure 1.2. In this way, an integrated architecture has the following advantages over a federated architecture [8]–[10]:

- shorter bill of materials, and thus, smaller size and volume, lower weight, lower power consumption, and lower cost;

- lower hardware development and hardware certification effort, and therefore, lower time to market and cost;

- lower hardware fault rate, higher reliability and availability, and therefore, lower maintenance costs;

- lower life-cycle costs, and thus, larger market size and higher profit.

*Figure 1.2. Illustration of an integrated architecture.*

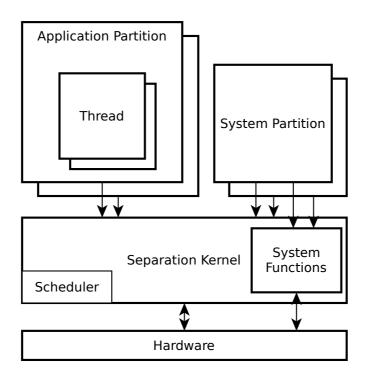

As illustrated in Figure 1.2, in an integrated architecture, computing units assigned with multiple functions rely on a separation kernel. The separation kernel is responsible for providing predictable execution environments, also called partitions, logically isolated in time (i.e., execution time) and space (i.e., memory and I/O devices) from each other. The separation kernel enforces isolation, through time and space partitioning, that is: by allocating a fixed memory and I/O space as well as a predefined execution time slot to each partition, and by allowing only predefined communication between partitions. The separation kernel guarantees fault containment and isolation by ensuring that partitions do not interfere with each other and, for example, that a failure in a partition assigned with a low-SIL function does not interfere with a partition assigned with a high-SIL function. The separation kernel, nonetheless, must be certified according to at least the highest SIL among the functions in the computing unit.

The separation kernel concept, by itself, however, does not define the actual execution environment available to functions (e.g., the available services, their interface), except that these must be time

and space partitioned. To address this shortcoming and improve the interoperability between different vendors and suppliers, a few standards, such as ARINC 653 [14] for the integrated modular avionics architecture, have been developed, defining the available services and their interface (i.e., the execution environment). Still, the execution environments defined by those standards do not provide compatibility with legacy software. However, significant investments have been made in legacy software and, in many cases, developing anew is not possible (e.g., licensing issues, closed source). To address this problem, using a hypervisor as the separation kernel is being considered [15]–[19].

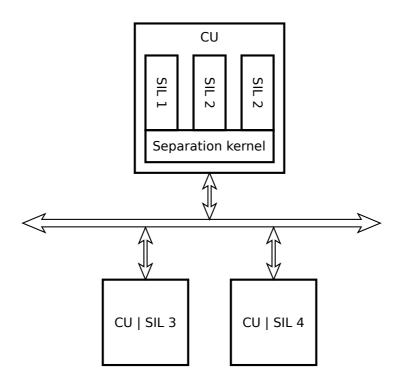

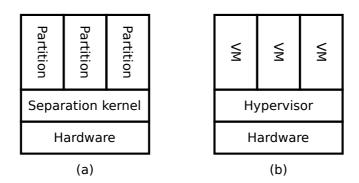

A hypervisor can be regarded as a specialization of the separation kernel. As illustrated in Figure 1.3, while a separation kernel provides partitions, a hypervisor provides virtual machines. A hypervisor is not only able to do everything that a separation kernel does, such as time and space partitioning, but it also provides compatibility with legacy software, such as real-time and general-purpose operating systems and applications. A hypervisor, therefore, enables the software developed for a legacy federated architecture, for example, to be reused with none or few modification on a newer integrated architecture. Consequently, using a hypervisor as the separation kernel enables the transition from a federated to an integrated architecture to be smoother and less costly. Nowadays, most hypervisors, however, as will be demonstrated in *Section 2.2. Virtualization and Hypervisors*, either (1) do not provide complete legacy compatibility as they rely on paravirtualization, which requires legacy software to be modified to fit a hypervisor-specific, often proprietary, interface, or (2) do provide complete legacy compatibility, but depend on high-end hardware (i.e., hardware with virtualization extensions) which leads to large size and volume, high weight, high power consumption, and high cost. Full virtualization on low-end hardware (i.e., hardware without virtualization extensions), on the other end, has none of those disadvantages.

Figure 1.3. Illustration of (a) a separation kernel vs. (b) a hypervisor.

Low-end hardware full virtualization is able to provide the same features as high-end hardware full virtualization, but on low-end hardware. Full virtualization on low-end hardware must be accomplished using mechanisms which were not originally designed for it. Therefore, full virtualization on low-end hardware is not always possible because the hardware may not fulfill the necessary requirements [20]. Furthermore, it is often claimed that it is not feasible due to an unacceptably high virtualization overhead (e.g., [21]); however, we were unable to find real-world quantitative results to support those claims..

In this thesis, performance and footprint (i.e., the size of the trusted computing base and memory footprint) measurements from a case study on low-end hardware full virtualization are presented. More specifically, a case study to evaluate to what extent low-end hardware full virtualization is an alternative to high-end hardware full virtualization and paravirtualization, and provide compatibility with unmodified legacy software with acceptable performance and footprint. At the same time, one processor architecture is evaluated in its ability for the realization of low-end hardware full virtualization, so that the limitations, if any, of this and other similar processor architectures can be addressed in the future.

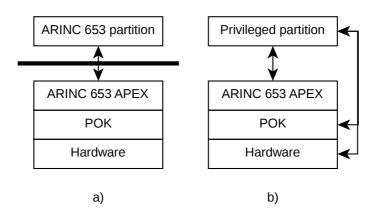

In this thesis, first, Rodosvisor, a hypervisor featuring full virtualization of the PowerPC 405 [21] (i.e., a representative of low-end hardware), is presented. Second, it is described how Rodosvisor has been integrated with POK [23], an ARINC 653 separation kernel (and real-time operating system), resulting in POK/rodosvisor. Third, an evaluation of the virtualization overhead in a Linux-based operating system is presented, by comparing several benchmarks performed on bare metal and as a guest on POK/rodosvisor. This is similar to what is presented in [24]; there, however, a hypervisor based on paravirtualization is used. Forth, a detailed look at the performance of POK/rodosvisor's internal operation is presented (i.e., POK/rodosvisor's performance profile), namely: interrupt handlers and context switching. Fifth and last, the size of POK/rodosvisor's trusted computing base and memory footprint for various configurations are presented.

# 1.2. Model-Driven Engineering

In terms of requirements analysis, software design, verification and certification, conventional development methods employ informal methods, prone to misunderstanding, and where the opportunity for automatic generation of the implementation is lost [25], [26]. Furthermore, when it comes to the implementation, conventional development methods depend on a significant amount of manual and error-prone labor, leading to long time-to-market [25], [26]. Knowing that the complexity and the number of safety-critical embedded systems is increasing, it becomes necessary

to apply methods which reduce the accidental complexity, and thus, accelerate development while still maintaining or improving quality. Accidental complexity is the complexity associated with a design or implementation not directly related to the solution space. In the literature many methods have been proposed to improve upon conventional development methods, such as:

- Computer-aided software engineering (CASE) [27], [28]: it emerged when 3<sup>rd</sup> generation programming languages started to reveal limitations to cope with complexity, and focused on general-purpose graphical programming (e.g., state machines, structure diagrams, data flow diagrams) to express design intent; at the time, however, CASE failed to become widely adopted because the technology was not mature enough, and because programming languages and platforms evolved, alleviating the need for CASE.

- Component-based software engineering (CBSE) [29], [30]: it defends that systems should be

designed by assembling software components together; CBSE, however, focuses mostly on

reuse of components and not on improving the implementation of the components

themselves.

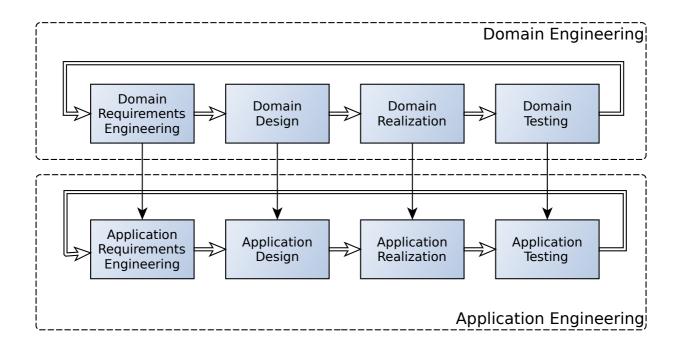

- Software product-line engineering (SPLE) [31], [32]: it enables organizations to built an array of similar software products (applications) from a common (domain specific) and a variable (application specific) pool of resources, and thus, reduce development effort and cost, when compared with conventional single system development; the downside of SPLE is that variability management is still not mature enough, and it requires a significant upfront investment.

- Model-driven engineering (MDE) [28], [33]: it advocates that development should be driven by high-level models which raise the abstraction level (when compared with 3<sup>rd</sup> generation programming languages) and reduce the distance between the problem space and the solution space, thus facilitating development. MDE technologies are still not mature enough for wide adoption and a significant upfront investment is also required.

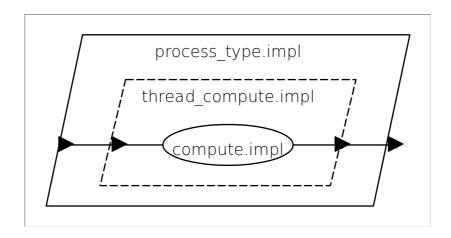

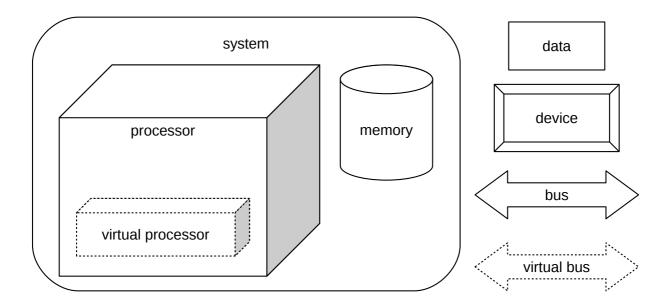

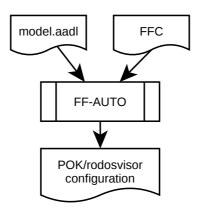

POK, mentioned earlier, through Ocarina [34]–[37], supports MDE. Ocarina is a compiler for the Analysis & Architecture Description Language (AADL) [38]. AADL enables the specification of the software and hardware architecture, and thus, the specification of the desired system configuration at a high level of abstraction, and features: processors, memories, processes, threads, subprograms, inter and intra-partition communication, etc. Ocarina is able to transform an AADL model into a POK configuration, composed by C source code and makefiles. Ocarina is also capable of generating partitions, if necessary. Ocarina, however, did not support the features that

have been added to POK, namely: virtual machines and privileged partitions.

In this thesis, it is described how Ocarina has been extended to support virtual machines and privileged partitions. In this way, it is demonstrated: (1) the ability of AADL to represent those features, (2) the ability of Ocarina to support those representations and to generate a POK configuration accordingly, and (3) their ability to replace conventional approaches. In this thesis, it is also demonstrated the ability of AADL-based MDE to reduce the engineering effort when compared to a conventional approach, by comparing the engineering effort required by an AADL-based with a manual development approach.

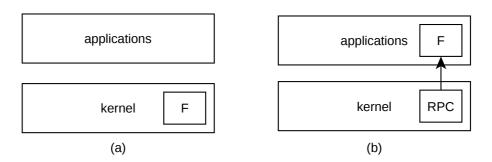

# 1.3. Functionality Farming

Nowadays, most operating systems follow a monolithic architecture [39]–[41]. In a monolithic architecture many of the services provided by the operating system (e.g., device drivers and protocol stacks) are deployed in the same address space as the kernel. For example, in the Linux kernel, version 2.6, 88% of the code is related to protocol and device drivers [42]. This, however, leads to a large kernel, which in turn, is associated with the following drawbacks:

- a large number of bugs and low reliability: a conservative estimate indicates that there are six bugs per 1,000 source lines of code, and device drivers have bug rates that are three to seven times higher than normal code [39], [43];

- a large attack surface and weak security: since the kernel is part of the trusted computing base of the entire system, if even a small function in the kernel is compromised, then, the entire system is at risk [42], [44];

- a high certification effort: a large kernel is also harder to certify than a small one [41], [45].

Furthermore, most of those services are not explicitly schedulable and "steal" other schedulable entities' execution time, leading to poor predictability and scalability as well.

To reduce the size of the trusted computing base (TCB), and thus, to improve security and reduce the certification effort, some authors propose the use of architectures based on: (1) a virtual machine monitor (or hypervisor) [42], [44], [46], or (2) a microkernel [41], or (3) a combination of the two (i.e., a microkernel with virtualization support) [47]. In these architecture, the size of the core/root kernel (and thus, of the TCB) is much smaller than the kernel found in most commodity operating systems. In these architectures, commodity operating systems are pushed onto a virtual machine (on a hypervisor-based architecture) or onto one or more user-level servers (on a microkernel-based architecture), reducing the effects that a compromised commodity operating system can have on the

system as a whole. Alongside commodity operating systems, critical services are deployed on other virtual machines (or user-level servers), which depend on a much smaller TCB than that in a commodity operating system. These architectures, however, depend on an additional level of indirection which leads to poor performance. Furthermore, on a hypervisor-based architecture in particular, virtual machines are often coarse-grained and heavyweight leading to high resource usage. On a microkernel architecture, on the other end, there is no compatibility with legacy software, and the porting effort can be very significant. An architecture based on a "microkernel with virtualization support" solves the above issues with the other two architectures, at the cost, however, of a larger size of the kernel. Still, all these architectures depend on the development of a new kernel, and thus, of a significant upfront investment; if the development of the new kernel fails, the cost is huge. In the end, these architectures do not tackle the source of the problem, i.e., the large size of the kernel in commodity operating systems, and just work around it.

In this thesis, functionality farming is proposed, which, instead of a new architecture, consists in partitioning existing kernels by (1) moving functionality out of the kernel and onto the application (or partition) level, to reduce the size of the kernel, and by (2) replacing the functionality being moved with remote procedure calls to the partition level, to bridge the gap between the kernel and the partition level. This is illustrated in Figure 1.4.

Figure 1.4. Illustration of functionality farming: (a) before functionality farming; (b) after functionality farming.

At the partition level, memory protection is enforced (space partitioning), and, previously non-schedulable entities, become explicitly schedulable (time partitioning). Through space partitioning, it is possible to reduce the size of the kernel, and thus, improve its reliability and security, as well as to reduce the certification effort. Additionally, in case of failure only the faulting partition, and not the entire kernel (and thus, not the entire system), needs to be restarted, leading to higher availability as well. On the other end, through time partitioning, it is possible to improve the

kernel's predictability and scalability by making parts of the kernel explicitly schedulable. At the partition level, moreover, it is easier to distribute the operating system's services across the cores of a multicore processor architecture, leading to improved predictability and scalability on such platforms.

Unlike other works, functionality farming tackles the source of the problem (i.e., the size of the kernel in commodity operating systems). It requires a lower upfront investment, since it enables a progressive reduction of the size of the kernel, instead of an all-or-nothing approach, and thus, it is a more agile approach as it enables some decisions to be postponed closer to delivery time when information about the system's requirements is more precise.

Time and space partitioning an existing kernel, nevertheless, is not an easy task. In some cases, because of a functionality's level of coupling with kernel or its functional requirements (e.g., compatibility with hardware-dependent, kernel-level software), ensuring that time and space partitioning is possible, and at the same time, fulfilling the functionality's functional requirements may depend on a significant engineering effort. To address this issue, functionality farming relies on various partition types. Each partition type provides distinct levels of partitioning (e.g., from timeonly partitioning to both time and space partitioning), as well as they fulfill different functional requirements (e.g., from compatibility with hardware-dependent, kernel-level software to compatibility with only hardware-independent software). These different partition types, not only increase the extent to which functionality farming is more easily accomplished, but also enable an even more progressive reduction of the size of the kernel. Thus, these different partition types enable fast design space exploration, and reduce the associated risk. As an example, consider the following. In the beginning, when a functionality is tightly coupled with the kernel, achieving space partitioning may require a significant engineering effort, while achieving time partitioning may not be as hard, then, a partition which provides time-only partitioning can be used. At this stage, it cannot be expected that the size of the kernel will be reduced; nevertheless, as will be shown later, time-only partitioning can reveal interesting design alternatives, as well as it enables bad design alternatives to be ruled out early on. After modifying the functionality to enable space partitioning, it may still depend on compatibility with kernel-level software, then, a partition providing time and space partitioning as well as compatibility with kernel-level software can be used. Lastly, after the functionality is made hardware-independent, then, a lightweight, hardware-independent partition can be used.

Functionality farming alone, however, despite the benefits, still depends on a significant engineering effort, as will be shown later, and its effects are often very hard to predict, meaning that

the associated risk is still high.

This thesis also presents FF-AUTO, a tool which performs functionality farming semi-automatically in POK/rodosvisor. With FF-AUTO, the engineering effort, and thus, the risk associated with functionality farming is significantly reduced, making it also an ideal tool for design space exploration. As explained earlier, POK/rodosvisor supports three partition types:

- ARINC 653 partitions: support only hardware-independent software but enforce both time and space partitioning;

- privileged partitions: support all kinds of software (i.e., hardware-dependent and hardware-independent software), enforce time partitioning but not space partitioning;

- and virtual machines: support all kinds of software, and enforce both time and space partitioning (at the cost, however, of a virtualization overhead).

This thesis also demonstrates how functionality farming is able to improve the design and the performance of POK/rodosvisor, as well as how FF-AUTO enables a significant reduction of the required engineering effort. It was not possible to demonstrate a reduction of the size of the kernel since POK/rodosvisor is already a very small kernel (very close to microkernel). Finally, even though functionality farming and FF-AUTO, currently, target only POK/rodosvisor, its underlying methodology can be applied to any other operating system.

#### 1.4. Thesis Structure

This rest of this thesis is organized as follows.

In the next chapter, *Chapter 2. Rodosvisor*, a hypervisor featuring full virtualization of the PowerPC 405 (i.e., a representative of low-end hardware), is described.

The following chapter, *Chapter 3. POK/rodosvisor*, describes how POK has been extended with support for privileged partitions, and how POK and Rodosvisor have been integrated, becoming POK/rodosvisor. Moreover, the virtualization overhead and the performance profile of POK/rodosvisor are presented. POK/rodosvisor's size of the trusted computing base and memory footprint for various configurations are also presented.

Chapter 4. *Model-Driven Engineering using Ocarina* explains how support for privileged partitions and virtual machines has been added to AADL and Ocarina; an evaluation of the reduction of the engineering effort enabled by AADL and Ocarina is presented as well.

In Chapter 5. Functionality Farming, FF-AUTO and its underlying methodology are presented; two

use cases are also presented, demonstrating that functionality farming is able to improve the design and the performance of POK/rodosvisor, and that FF-AUTO contributes to a significant reduction of the required engineering effort, and thus, of the associated risk.

Finally, *Chapter 6. Conclusion*, ends this thesis with a summary of the major findings and contributions.

#### 1.5. Publications

The following publications were performed in the course of this work:

- A. Carvalho, F. Afonso, P. Cardoso, J. Cabral, M. Ekpanyapong, S. Montenegro, and A. Tavares, "Functionality Farming in POK/rodosvisor," in the International Journal of Computer Science and Software Engineering 5, no. 8 (2016): 161-174.

- A. Carvalho, V. Silva, F. Afonso, P. Cardoso, J. Cabral, M. Ekpanyapong, S. Montenegro, and A. Tavares, "Full Virtualization on Low-End Hardware: a Case Study," in the 42nd Annual Conference of IEEE Industrial Electronics Society, Florence, Italy, 2016.

- A. Carvalho, F. Afonso, P. Cardoso, J. Cabral, M. Ekpanyapong, S. Montenegro, and A. Tavares, "Cache full-virtualization for the PowerPC 405-S," in the 11th IEEE International Conference on Industrial Informatics, Bochum, Germany, 2013.

- A. Tavares, A. Carvalho, P. Rodrigues, P. Garcia, T. Gomes, J. Cabral, P. Cardoso, S. Montenegro, and M. Ekpanyapong, "A customizable and ARINC 653 quasi-compliant hypervisor," in the 2012 IEEE International Conference on Industrial Technology, Athens, Greece, 2012.

- A. Tavares, A. Didimo, S. Montenegro, T. Gomes, J. Cabral, P. Cardoso, and M. Ekpanyapong, "RodosVisor an Object-Oriented and Customizable Hypervisor: The CPU Virtualization," in the Conference on Embedded Systems, Computational Intelligence and Telematics in Control, Würzburg, Germany, 2012.

# 2. Rodosvisor

#### 2.1. Introduction

As explained in the previous chapter, *Section 1.1. Full Virtualization on Low-End Hardware*, the use of a hypervisor as a separation kernel in integrated architectures is being considered, as it not only provides time and space partitioning, but also provides compatibility with legacy software [15]–[19]. However, the hypervisors found in the literature, as will be demonstrated in *Section 2.2*. *Virtualization and Hypervisors*, either (1) do not provide complete legacy compatibility as they rely on paravirtualization, which requires legacy software to be modified to fit a hypervisor-specific, often proprietary interface, or (2) do provide complete legacy compatibility but depend on high-end hardware (i.e., hardware with virtualization extensions) which leads to large system size and volume, high weight, high power consumption, and high cost. Full virtualization on low-end hardware (i.e., hardware without virtualization extensions), on the other end, has none of those advantages.

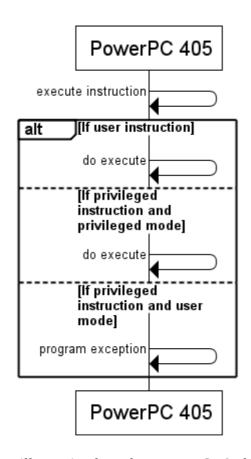

In this thesis, Rodosvisor, a hypervisor featuring full virtualization of the IBM PowerPC 405 [22], is presented. The PowerPC 405 has been chosen because (1) it is a simple, low power, low cost processor, especially dedicated to embedded system and thus, a good representative of low-end hardware; and because (2) Xilinx [48], [49] provides good development support, enabling the construction and evaluation of various hardware configurations, such as single-core and dual-core processor configurations. Alternatively, ARM could have been chosen as the processor architecture; however, a PowerPC-405-equivalent ARM processor is much more complex, and thus, too risky for this case study. Consider, for example, that an ARMv7, application profile, virtual memory system architecture implementation, features more than 20 privileged instructions and more than 100 privileged registers; the PowerPC 405, on the other end, features 19 privileged instructions and around 40 privileged registers.

Rodosvisor, similarly to [50] provides "cycle-accurate" virtual processors (VCPU) (i.e., their execution time does not effect the execution time of co-existing virtual processors) compatible with the PowerPC 405 (the CPU). Rodosvisor has not an explicit representation of a virtual machine; instead, a VCPU is configured to enforce the boundaries of the virtual machine, such as its dedicated and shared memory address space, and I/O devices. Moreover, Rodosvisor, by itself, cannot support a running system (e.g., it does not provide a scheduler); it needs to be integrated into a host which provides the services required for a running system. As will be explained in *Section* 2.3. *Interface with the Host*, the host is responsible for:

- initialization and scheduling of VCPUs;

- loading, resuming, pausing and saving VCPUs;

- and, whenever a VCPU is running, for redirecting interrupts to the current VCPU.

In the next chapter, *Chapter 3. POK/rodosvisor*, among other things, the integration of Rodosvisor with POK [23], an ARINC 653 separation kernel, becoming POK/rodosvisor, is described. An evaluation of the virtualization overhead, POK/rodosvisor's performance profile, as well as POK/rodosvisor's size of the trusted computing base and memory footprint for various configurations are also presented.

Some publications have been made based on a prior version of the Rodosvisor [51]–[53]. In those publications a bare metal version of Rodosvisor is described. In this thesis, unless otherwise noted, when Rodosvisor is referred, it means the newer, host-assisted (a.k.a., hosted) version of Rodosvisor.

## 2.1.1. Chapter Organization

This chapter is organized as follows.

In the next section, *Section 2.2. Virtualization and Hypervisors*, background on virtualization and hypervisors is given.

In *Section 2.3. Interface with the Host*, the interface with the host and its responsibilities are described.

The methodologies used for full virtualization of the PowerPC 405 are explained in *Section 2.4*. *Full Virtualization*; this includes virtualization of:

- the instruction set, Section 2.4.1. Instruction Set;

- the timers, Section 2.4.2. Timers;

- the memory management unit, Section 2.4.3. Memory Management Unit;

- and interrupts, *Section 2.4.4*. *Interrupts*.

In *Section 2.5. I/O virtualization* and *Section 2.6. Paravirtualization*, the various mechanisms available for I/O virtualization and paravirtualization, respectively, are described.

In *Section 2.7. Future Work*, future work is proposed and finally, in *Section 2.8. Summary*, a summary of this chapter is given.

# 2.2. Virtualization and Hypervisors

In the same way as a separation kernel enforces time and space partitioning between partitions, a hypervisor enforces time and space partitioning between virtual machines, as illustrated in Figure 2.1. The software running "inside" a partition or virtual machine is called "the guest." As in [20], "a virtual machine is taken to be an efficient, isolated duplicate of the real machine," and, a hypervisor: "first, [...] provides an environment for programs which is essentially identical with the original machine; second, programs run in this environment show at worst only minor decreases in speed; and last, [it] is in complete control of system resources." Furthermore [20] adds:

- "Any program run under the [hypervisor] should exhibit an effect identical with that

demonstrated if the program had been run on the original machine directly, with the possible

exception of differences caused by the availability of system resources and differences

caused by timing dependencies."

- "It demands that a statistically dominant subset of the virtual processor's instructions be executed directly by the real processor, with no software intervention by the [hypervisor]." (This in particular, distinguishes software virtualization from software emulation.)

- "The [hypervisor] is said to have complete control of ... resources if (1) it is not possible for a program running under it in the created environment to access any resource not explicitly allocated to it, and (2) it is possible under certain circumstances for the [hypervisor] to regain control of resources already allocated."

Figure 2.1. Illustration of (a) a separation kernel vs. (b) a hypervisor.

Through time and space partitioning a hypervisor enforces workload isolation, and thus, enables workload consolidation. Workload isolation guarantees that the behavior of a virtual machine, such as a failure, will not affect the rest of the system (i.e., other partitions and the hypervisor).

Furthermore, with workload isolation, the guests can be developed independently of each other, leading to lower development and certification effort. On top of workload isolation, workload consolidation enables a single computing unit to perform the same functions as multiple physically independent computing units, leading to: shorter bill of materials, lower size/volume and weight, lower power consumption, lower hardware development effort and cost, lower life-cycle costs, etc. [9], [54]. For example, a hypervisor enables a single computing unit to hold different operating system with different API (e.g., ARINC 653, OSEK, AUTOSAR, POSIX), leading to improved compatibility with legacy software, improved reuse and higher variability. The distinctive feature of a hypervisor is compatibility with legacy software, from simple applications with no operating system up to full fledged operating systems (e.g., Linux, Windows). As result, a hypervisor can improve reuse and reduce development and certification effort.

There are two types of virtualization, namely: full virtualization and paravirtualization. With full virtualization, the virtual machines established by the hypervisor provide an interface identical to that of the underlying hardware platform (i.e., the physical/real machine); therefore, such a virtual machine is capable of hosting legacy software with no modifications. There are, however, two approaches for the realization of full virtualization: (1) low-end hardware full virtualization, and (2) high-end hardware full virtualization. Low-end hardware full virtualization relies on the mechanisms provided by the underlying hardware platform, which, however, were not originally thought for the realization of full virtualization, and therefore, not all hardware platforms fulfill the necessary requirements [20]. Moreover, it is often claimed that it is not feasible due to an unacceptably high virtualization overhead; (e.g., [21]); however, we were unable to find real-world quantitative results to support those claims. High-end hardware full virtualization, on the other end, depends on hardware with virtualization support [55]-[59], which lead to a large system size, weight, power consumption, and cost. With paravirtualization, an alternative to full virtualization, the (para) virtual machines established by the hypervisor do not provide an interface identical to the underlying hardware platform, and instead, provide a different, more efficient interface. Paravirtualization should provide better performance than low-end hardware full virtualization, and it is the only option on hardware platforms which do not fulfill the requirements for full virtualization. When paravirtualization is used, however, the guests need to be modified to fit a hypervisor-specific, often proprietary interface. In Table 2.1, it can be seen that most hypervisors provide high-end hardware full virtualization and or paravirtualization; only Proteus [60], [61], and Rodosvisor, presented in this thesis, do support low-end hardware full virtualization. The authors of Proteus, however, failed to back their claims by demonstrating compatibility with legacy software,

such as a general-purpose operating system like Linux.

Table 2.1. Comparison of existing hypervisors in terms of low-end hardware full virtualization (LH-FV), high-end hardware full virtualization (HH-FV), and paravirtualization (PV).

| Hypervisor                                        | LH-FV | HH-FV | PV |

|---------------------------------------------------|-------|-------|----|

| AIR [136], [137]                                  |       |       | X  |

| ARLX [19], [135]                                  |       | X     | X  |

| Bruns, 2013 [138]                                 |       |       | X  |

| Codezero [140]                                    |       |       | X  |

| Denali [121]–[123]                                |       |       | X  |

| Green Hills Integrity Multivisor [18]             |       | X     | X  |

| Joe, 2012 [64]                                    |       | X     |    |

| KVM [62], [63]                                    |       | X     |    |

| LynxSecure Separation Kernel Hypervisor [16]      |       | X     | X  |

| NOVA [139]                                        |       | X     |    |

| OKL4 [47]                                         |       | X     | X  |

| PikeOS [17]                                       |       | X     | X  |

| Proteus [60], [61]                                | X     |       | X  |

| QNX Hypervisor [141]                              |       | X     |    |

| Real Time Systems GbmH Hypervisor [125]           |       | X     | X  |

| SierraVisor [134]                                 |       | X     | X  |

| Spumone [126]                                     |       |       | X  |

| Wind River VxWorks (Virtualization Profile) [127] |       | X     | X  |

| X-Hyp [128]                                       |       |       | X  |

| Xen [129]                                         |       | X     | X  |

| XtratuM [15], [130]–[132]                         |       |       | X  |

| Zampiva, 2015 [133]                               |       | X     | X  |

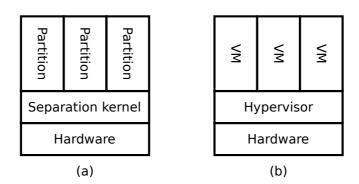

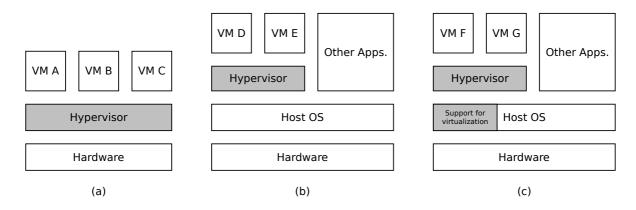

Independently of the type of virtualization, a hypervisor can be classified as bare metal (or type 1), or as hosted (or type 2). Figure 2.2 illustrates the difference between bare metal and hosted hypervisors. A bare metal hypervisor, Figure 2.2(a), sits directly on top of the hardware platform and has full control over it. A hosted hypervisor, Figure 2.2(b), sits on top of an existing operating system, i.e., the host operating system (e.g., Linux, Windows), with which it cooperates. A hosted hypervisor usually requires special support from the host operating system (e.g., kernel modules), usually provided by the same vendor as the hypervisor application. Some authors refer to the

combination of operating system support for virtualization and the hypervisor application as a type 1.5 hypervisor, illustrated in Figure 2.2(c). With complete control over the hardware platform, a bare metal hypervisor is able to provide higher performance than a hosted hypervisor. On the other end, a hosted hypervisor can use the services provided by the host operating system to simplify its design and implementation. Moreover, a hosted hypervisor enables the host operating system to support workloads other than virtual machines. Of all the hypervisors shown in Table 2.1, only KVM [62], [63] and Joe, 2012 [64], are hosted hypervisors; all the others are bare metal hypervisors. Rodosvisor, developed during this work, by itself, can be considered as a hosted hypervisor; POK/rodosvisor, i.e., the result of the integration of Rodosvisor and POK, on the other end, can be considered as a bare metal hypervisor.

Figure 2.2. Hypervisor types: (a) bare metal, (b) hosted, and (c) type 1.5.

Historically, virtualization was first introduced in the 1960s by IBM with CP/CMS [65]. First, to solve the problem of hardware scarcity, enabling the same hardware to be shared among multiple users, and shortly thereafter to enable reuse of legacy software [66]. It became "meaningless" with the explosion of the personal computer but reappeared on the server side of the Internet to improve resource utilization and reduce power consumption [66], and it is now finding its way to highly-constrained embedded systems.

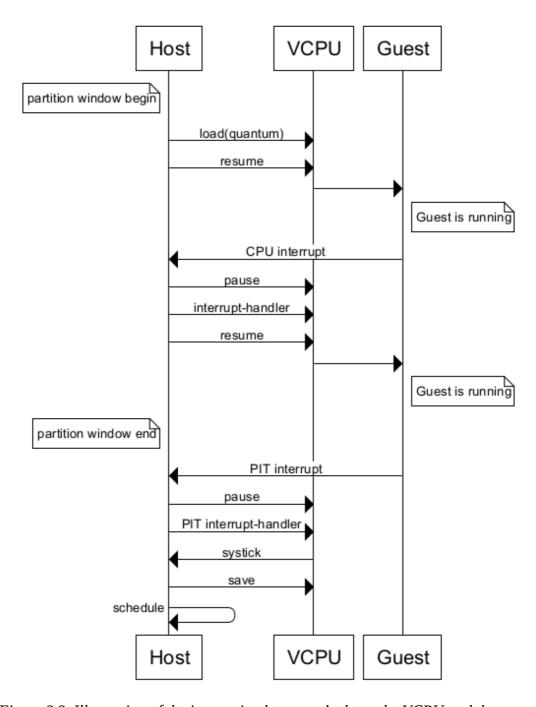

## 2.3. Interface with the Host

The expected interface between the host and a VCPU is illustrated in Figure 2.3. When a VCPU is scheduled, its partition window begins, and the host must "load" the VCPU through the corresponding "load" method in the VCPU's interface. The "load" method requires as a parameter the duration of the partition window (a.k.a., quantum). After a VCPU has been loaded, it assumes full control over the CPU and, when the partition window is over, the VCPU is responsible for

returning control back to the host. The VCPU, when requested to load, updates its internal state for the time since it was last unloaded/saved, and sets part of the CPU state to reflect the current state of the VCPU. The part of the CPU state that is set is such that it does not interfere with the operation of the VCPU (e.g., configure the memory management unit but do not enable it); this decreases the effort required for resuming and pausing the VCPU, described below, which need to be performed far more often.

Figure 2.3. Illustration of the interaction between the host, the VCPU and the guest.

After loading the VCPU, or after calling one of the VCPU interrupt-handlers described below, the host must "resume" the VCPU. The VCPU, when requested to resume, updates the remaining state of the CPU (i.e., not updated by "load") to reflect the current state of the VCPU and resumes the execution of the guest.

After the execution of the guest has been resumed, any CPU interrupt will be first handled by the host. The host is then responsible for:

- 1. saving the guest's user mode state in the VCPU's register file;

- 2. pausing the VCPU by calling the corresponding method in the VCPU's interface ("pause" is the inverse of "resume," i.e., it saves and updates the part of the CPU state which may interfere with the operation of the VCPU);

- 3. calling the corresponding VCPU interrupt-handler.

A special interrupt is the one that signals the end of the VCPU partition window; in the PowerPC 405 this is the programmable-interval timer (PIT) interrupt, described in more detail in *Section 2.4.2. Timers*. Like any other interrupt, the host is responsible for pausing the VCPU and calling the respective VCPU interrupt-handler. However, upon finding that a particular PIT interrupt is signaling the end of the partition window, the VCPU calls the host's "systick" method. (In *Section 2.4.2 Timers*, it is described how the VCPU finds that a particular PIT interrupt is signaling the end of the partition window.) The host, in turn, is responsible for saving the VCPU and calling the scheduler, effectively returning control back to the host. When a VCPU is requested to "save," it saves and updates the remaining part of the CPU state to reflect the host's expected state of the CPU.

### 2.4. Full Virtualization