#### **University of Minho**

**Engineering School**

Nelson Pinheiro Duarte Naia

# **Real-Time Linux and Hardware Accelerated Systems on QEMU**

Master's Thesis Master's Degree in Industrial Electronics Engineering and Computers

Carried out under guidance of

PhD Adriano José da Conceição Tavares

# Declaração

| Nome:                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nelson Pinheiro Duarte Naia                                                                                                                            |

| Endereço Eletrónico: npnaia@gmail.com                                                                                                                  |

| Telefone/Telemóvel: 91 057 96 72                                                                                                                       |

| Número do Bilhete de Identidade: 13783902                                                                                                              |

|                                                                                                                                                        |

| <b>Título da Dissertação:</b> Real-Time Linux and Hardware Accelerated Systems on QEMU                                                                 |

| Orientador: Professor Doutor Adriano José da Conceição Tavares                                                                                         |

| Designação do Mestrado:  Mestrado Integrado em Engenharia Eletrónica Industrial e Computadores                                                         |

| É AUTORIZADA A REPRODUÇÃO INTEGRAL DESTA TESE APENAS PARA EFEITOS DE INVESTIGAÇÃO, MEDIANTE DECLARAÇÃO ESCRITA DO INTERESSADO, QUE A TAL SE COMPROMETE |

| Universidade do Minho,/                                                                                                                                |

| Assinatura:                                                                                                                                            |

# Acknowledgments

"I would like to thank my supervisor, PhD Adriano Tavares, for all the knowledge insight throughout the project. I would especially like to thank engineer Vítor Silva, for his friendship and all the help and time spent providing guidance and sharing his knowledge and brilliant vision in engineering. I would also like to thank all professors and members of the Embedded Systems Research Group, for all the support and resources made available throughout this dissertation. A special thanks should also go to Embedded Systems Research Group students Marcelo Sousa, César Monteiro and João Gonçalves, that such as myself are graduating, and accompanied me through this journey, being workspace companions, providing peer reviews and above all tight friendships. Finally I would like to thank my parents and close family, for all the moral, emotional and financial support throughout all this engineering course. Without them, I wouldn't be able to do it at all. To everyone, my sincerest gratitude."

### Abstract

Software application acceleration, using parallelization techniques and dedicated hardware components, is often an optimization compromise in a cost-benefit relationship during the migration of software processes to hardware Intellectual Property (IP) dedicated cores or accelerators. In real-time applications extra care is needed when dealing with these issues, so that the real-time requirements of the application are not compromised. An isolated validation, as far as application domains are concerned, does not guarantee integral system functionality. Using an integrated co-simulation environment, chances of early system problem detection before moving to the physical implementation phase are improved. By adopting a design flow aided by co-simulation, not only is the development process sped up, but also resource independent, since the system can be developed in its entirety in a host platform without being bound to a physical target platform.

This dissertation aims to adopt a methodology of hardware-software co-design aided by co-simulation and extend embedded system simulation techniques to hardware IP co-simulation and integral validation, improving the design process of hardware accelerated embedded systems in their various development phases. Using Quick EMUlator (QEMU) as a tool for emulating embedded software platforms in a Linux-based environment, modifications were idealized and developed to enable QEMU to extend its embedded software platform emulating capabilities for custom hardware co-processor development purposes. Two QEMU extensions were developed, enabling easy integration of behavioral devices and co-simulation with external Register-Transfer Level (RTL) models in QEMU's target platforms. A Verilog PLI library was also developed to allow Verilog simulators that support PLI to perform co-simulation with QEMU. To demonstrate the capabilities of following a hardware-software embedded co-design using the developed simulation environment, a demonstration application scenario was developed following a design flow that takes advantage of said simulation environment possibilities.

### Resumo

A aceleração de aplicações de software, utilizando técnicas de paralelização e componentes de hardware dedicados, é frequentemente um compromisso de optimização numa relação de custo-benefício durante a migração de processos de software para aceleradores ou cores hardware IP dedicados. Em aplicações real-time, cuidados extra são necessários ao lidar com estas problemáticas, de forma a que os requisitos real-time da aplicação não sejam comprometidos. Uma validação isolada, no que respeitam os vários domínios de aplicação, não garante uma funcionalidade integral do sistema. Utilizando um ambiente de co-simulação integrado, falhas no sistema podem ser detectadas numa fase inicial do projecto, antes de ser atingida uma fase de implementação física. Ao adoptar um design flow auxiliado por cosimulação, não só é o processo de desenvolvimento agilizado, mas também isento de dependências a nível da plataforma target, uma vez que o sistema pode ser desenvolvido inteiramente na plataforma host sem estar dependente dos recursos físicos associados uma plataforma target. Esta dissertação surge no âmbito da validação de uma metodologia de hardware-software co-design auxiliada por co-simulação, no extender de técnicas de simulação de sistemas embebidos, com ou sem aceleração de processos em hardware RTL, e na validação integral, aperfeiçoando o processo de design dos mesmos ao longo das várias fases de desenvolvimento. Utilizando o QEMU como ferramenta para emulação de ambientes baseados em Linux para plataformas de CPU+FPGA, alterações foram idealizadas e desenvolvidas para permitir extender as capacidades de emulação das mesmas no QEMU, para propósitos de desenvolvimento de aceleradores em hardware customizados, possibilitando a integração de devices comportamentais e co-simulação com modelos RTL externos nas plataformas target do QEMU. Para demonstrar as capacidades de seguir um co-design de hardware-software embebido utilizando o ambiente de simulação desenvolvido, um cenário de aplicação demonstrador foi desenvolvido seguindo um design flow que toma partido das possibilidades do referido ambiente de simulação.

# Contents

| 1 | Intr | oduct   | ion                            | 1  |

|---|------|---------|--------------------------------|----|

|   | 1.1  | Conte   | extualization                  | 1  |

|   | 1.2  | Motiv   | ration and Objectives          | 4  |

|   | 1.3  | Contr   | ibutions                       | 4  |

|   | 1.4  | Disser  | rtation Structure              | 5  |

| 2 | Sta  | te of t | he Art                         | 7  |

|   | 2.1  | Embe    | dded Systems                   | 7  |

|   |      | 2.1.1   | Definition                     | 8  |

|   |      | 2.1.2   | Embedded Processors            | 9  |

|   |      | 2.1.3   | Embedded Development           | 11 |

|   |      | 2.1.4   | Real-Time Embedded Systems     | 13 |

|   | 2.2  | Opera   | ating Systems                  | 15 |

|   |      | 2.2.1   | Concurrency                    | 15 |

|   |      | 2.2.2   | Kernel and User Spaces         | 17 |

|   |      | 2.2.3   | Real-time Operating Systems    | 21 |

|   |      | 2.2.4   | Linux                          | 21 |

|   |      | 2.2.5   | Device Tree                    | 23 |

|   |      | 2.2.6   | Buildroot                      | 23 |

|   | 2.3  | Hardv   | vare Acceleration              | 24 |

|   |      | 2.3.1   | Hardware Description Languages | 25 |

|   |      | 2.3.2   | FPGA                           | 27 |

|   |      | 2.3.3   | FPGA SoC                       | 29 |

|   | 2.4  | Hardv   | vare-Software Co-Design        | 30 |

|   |      | 2.4.1   | System Modeling                | 31 |

|   |      | 2.4.2   | Software Parallelization       | 32 |

|   |      | 2.4.3   | Profiling                      | 32 |

|   |      | 2 4 4   | Hardware Design                | 32 |

|   |     | 2.4.5   | Validation                                  | 33 |

|---|-----|---------|---------------------------------------------|----|

|   |     | 2.4.6   | Metrics Confirmation/Implementation         | 33 |

|   | 2.5 | Hardw   | vare Accelerated Embedded System Simulation | 33 |

|   |     | 2.5.1   | Full System RTL Simulation                  | 34 |

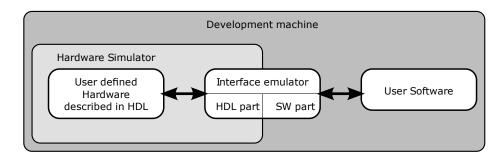

|   |     | 2.5.2   | RTL Simulation with Host Software           | 35 |

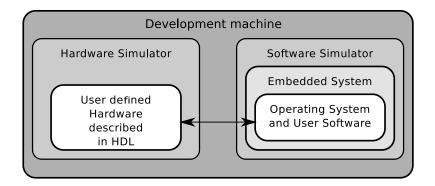

|   |     | 2.5.3   | RTL-Software Co-Simulation                  | 36 |

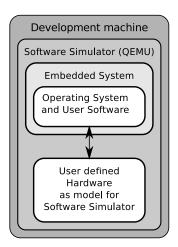

|   |     | 2.5.4   | Full System Software Simulation             | 37 |

|   | 2.6 | QEMU    | IJ;                                         | 38 |

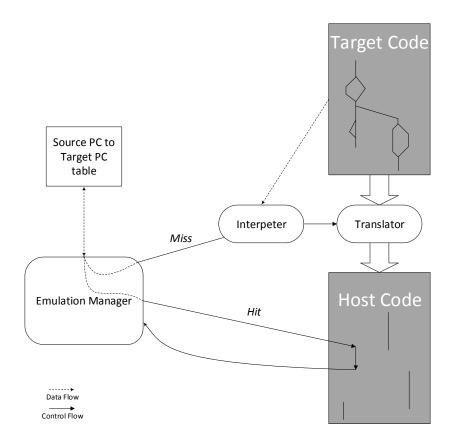

|   |     | 2.6.1   | Dynamic Binary Translation                  | 39 |

|   |     | 2.6.2   | QEMU Monitor                                | 41 |

|   |     | 2.6.3   | QEMU Platforms                              | 42 |

|   |     | 2.6.4   | QEMU Device Model                           | 45 |

|   |     | 2.6.5   | Time in QEMU                                | 48 |

|   | 2.7 | Verilog | g Programming Language Interface            | 49 |

|   |     | 2.7.1   | PLI Overview                                | 50 |

|   |     | 2.7.2   | PLI Routines                                | 52 |

|   |     | 2.7.3   | Calltf Routines                             | 52 |

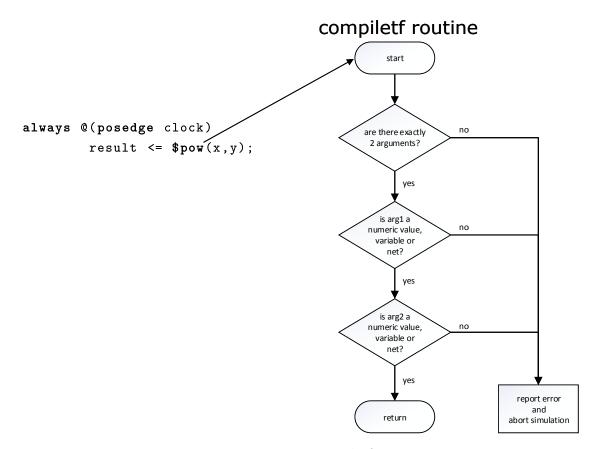

|   |     | 2.7.4   | Compiletf Routines                          | 53 |

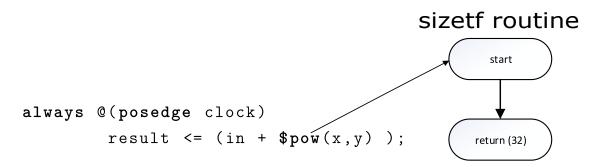

|   |     | 2.7.5   | Sizetf Routines                             | 55 |

|   |     | 2.7.6   | Simulation Callback Routines                | 55 |

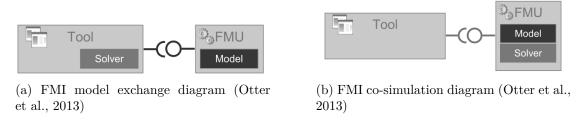

|   | 2.8 | Functi  | ional Mock-up Interface                     | 56 |

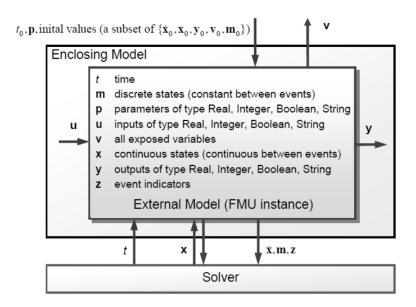

|   |     | 2.8.1   | FMI for Model Exchange                      | 57 |

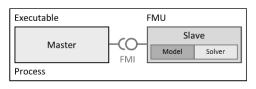

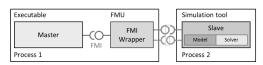

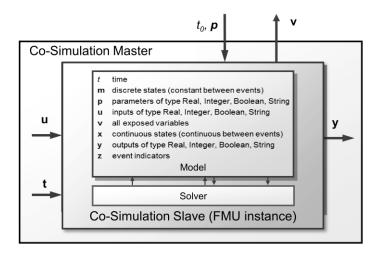

|   |     | 2.8.2   | FMI for Co-simulation                       | 59 |

|   |     | 2.8.3   | FMI in the Industry                         | 60 |

| 3 | Sys | tem D   | esign 6                                     | 35 |

|   | 3.1 | QEMU    | U Plugin Extension                          | 67 |

|   |     | 3.1.1   | Extension Overview                          | 68 |

|   |     | 3.1.2   | Device API                                  | 72 |

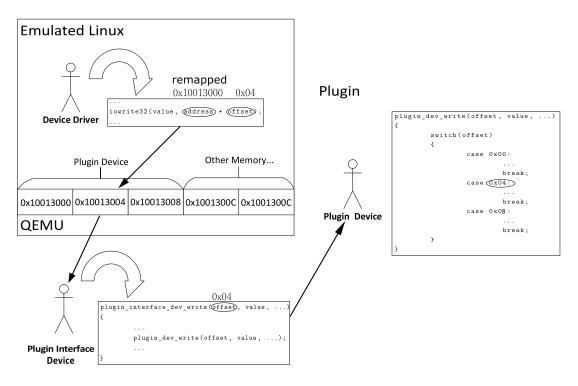

|   |     | 3.1.3   | I/O Mapping                                 | 74 |

|   |     | 3.1.4   | Interrupt API                               | 75 |

|   |     | 3.1.5   | Timing API                                  | 78 |

|   |     | 3.1.6   | Bus Master API                              | 80 |

|   | 3.2 | QEMU    |                                             | 81 |

|   |     | 3.2.1   |                                             | 82 |

|   |     | 3.2.2   |                                             | 85 |

|   |     | 3.2.3   | I/O mapping                                 | 90 |

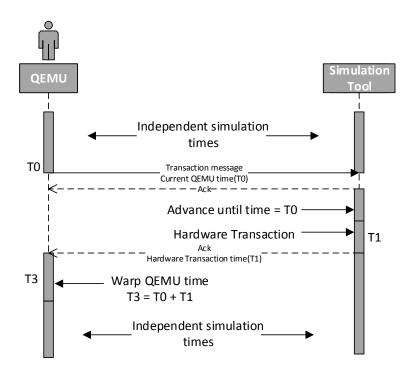

|    |                        | 3.2.4   | Timing                                                      | 91  |

|----|------------------------|---------|-------------------------------------------------------------|-----|

|    |                        | 3.2.5   | Interrupts and Bus Master Transactions                      | 93  |

|    |                        | 3.2.6   | QEMU External Tool Library                                  | 95  |

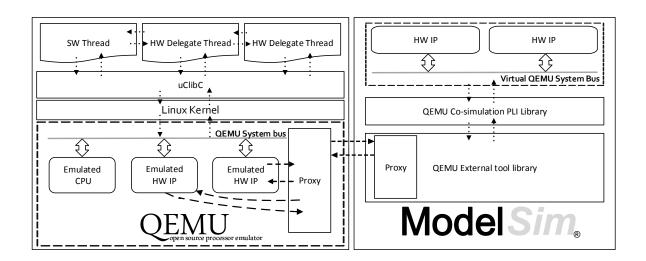

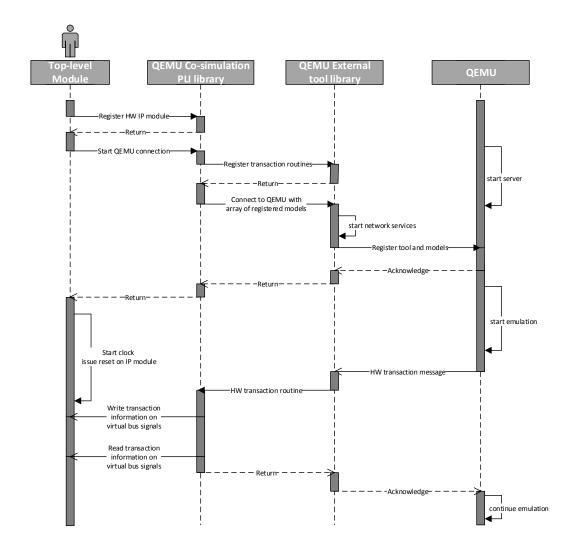

|    | 3.3                    | QEMU    | J Co-simulation PLI Library                                 | 96  |

|    |                        | 3.3.1   | Library Overview                                            | 97  |

|    |                        | 3.3.2   | Virtual QEMU System Bus Model                               | 99  |

|    |                        | 3.3.3   | PLI API                                                     | 103 |

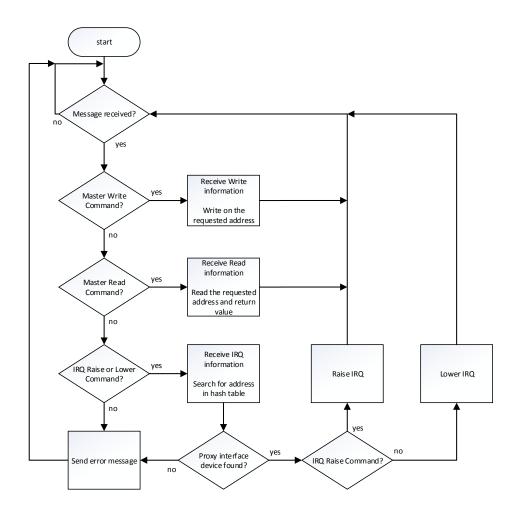

|    |                        | 3.3.4   | Transaction Handling                                        | 106 |

|    |                        | 3.3.5   | Bus Master API                                              | 106 |

|    |                        | 3.3.6   | Interrupt API                                               | 108 |

| 4  | Cas                    | e of St | udy                                                         | 111 |

|    | 4.1                    | Instan  | taneous Active and Reactive Powers Monitoring Application . | 111 |

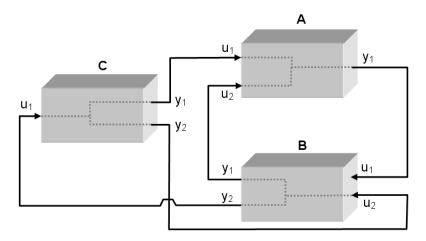

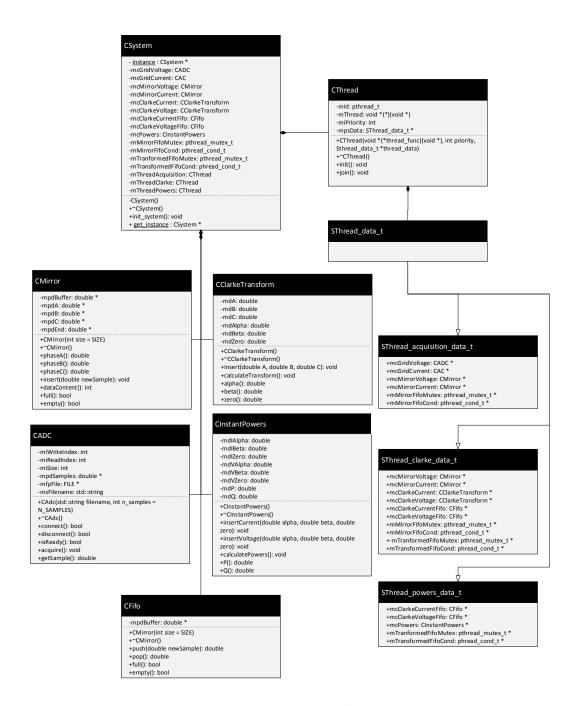

|    | 4.2                    | Systen  | n Modeling                                                  | 114 |

|    | 4.3                    | Result  | s                                                           | 116 |

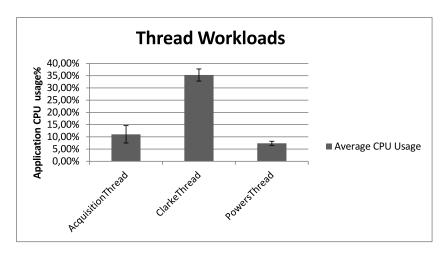

|    |                        | 4.3.1   | Profiling                                                   | 116 |

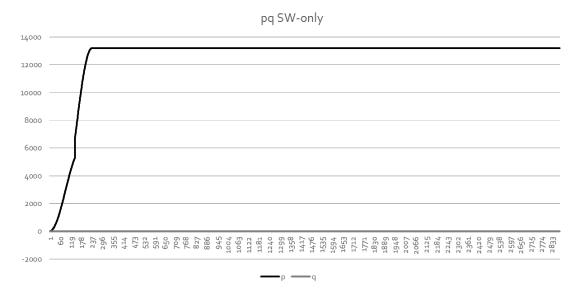

|    |                        | 4.3.2   | Software-only and Hardware-Software                         | 117 |

| 5  | Con                    | clusio  | n                                                           | 119 |

|    | 5.1                    | Develo  | oped Work                                                   | 119 |

|    | 5.2                    | Future  | e Work                                                      | 120 |

|    |                        |         |                                                             |     |

| Bi | bliog                  | graphy  |                                                             | 123 |

| A  | Lin                    | ux Sup  | port Material                                               | 125 |

|    | A.1                    | Real-ti | ime Linux Patching, Compilation and QEMU Boot with Buil-    |     |

|    |                        | droot   |                                                             | 125 |

|    |                        | A.1.1   | Buildroot Installation                                      | 125 |

|    |                        | A.1.2   | Real-time Linux Compilation                                 | 126 |

|    |                        | A.1.3   | Cross-compiling a Hello World Application with Buildroot .  | 133 |

|    |                        | A.1.4   | Booting a Cross-compiled Application with Linux in QEMU     | 135 |

|    | A.2                    | Device  | e Tree Versatile Express A-9 .dts File Example              | 140 |

| В  | $\mathbf{Q}\mathbf{E}$ | MU Su   | apport Material                                             | 151 |

|    | B.1                    | QEMU    | J Machines                                                  | 151 |

|    |                        | B.1.1   | Aarch64 Architecture                                        | 151 |

|    |                        | B.1.2   | Alpha Architecture                                          | 152 |

|    |                        | B.1.3   | ARM Architecture                                            | 153 |

|              |     | B.1.4   | CRIS Architecture                                                                                                                                                                                                      |

|--------------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |     | B.1.5   | i<br>386 Architecture                                                                                                                                                                                                  |

|              |     | B.1.6   | $Lattice Micro 32\ Architecture\ \dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$ |

|              |     | B.1.7   | Motorolla 68000 Architecture $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ 155$                                                                                                                                      |

|              |     | B.1.8   | Microblaze Softcore Architecture $\ \ldots \ \ldots \ \ldots \ \ldots \ 156$                                                                                                                                           |

|              |     | B.1.9   | Microblaze Softcore Little Endian Architecture                                                                                                                                                                         |

|              |     | B.1.10  | MIPS Architecture                                                                                                                                                                                                      |

|              |     | B.1.11  | MIPS Little Endian Architecture $\ \ldots \ \ldots \ \ldots \ \ldots \ 156$                                                                                                                                            |

|              |     | B.1.12  | MIPS64 Architecture                                                                                                                                                                                                    |

|              |     | B.1.13  | MIPS64 Little Endian Architecture                                                                                                                                                                                      |

|              |     | B.1.14  | Moxie Softcore Architecture                                                                                                                                                                                            |

|              |     | B.1.15  | OpenRisc32 Architecture                                                                                                                                                                                                |

|              |     | B.1.16  | PowerPC Architecture                                                                                                                                                                                                   |

|              |     | B.1.17  | PowerPC64 Architecture                                                                                                                                                                                                 |

|              |     | B.1.18  | PowerPC Embedded Architecture                                                                                                                                                                                          |

|              |     | B.1.19  | ESA/390 Architecture $\dots \dots \dots$                                                                               |

|              |     | B.1.20  | SuperH4 Architecture                                                                                                                                                                                                   |

|              |     | B.1.21  | SuperH4 Big Endian Architecture                                                                                                                                                                                        |

|              |     | B.1.22  | SPARC Architecture                                                                                                                                                                                                     |

|              |     | B.1.23  | SPARC64 Architecture                                                                                                                                                                                                   |

|              |     | B.1.24  | Tricore Architecture $\dots \dots \dots$                                                                               |

|              |     | B.1.25  | Unicore32 Architecture                                                                                                                                                                                                 |

|              |     | B.1.26  | x86_64 Architecture                                                                                                                                                                                                    |

|              |     | B.1.27  | Xtensa Architecture                                                                                                                                                                                                    |

|              |     | B.1.28  | Xtensa Big Endian Architecture                                                                                                                                                                                         |

|              | B.2 | QEMU    | Tricore Testboard Machine Example                                                                                                                                                                                      |

|              | В.3 | QEMU    | Memory-Mapped I/O LED Device Example 166                                                                                                                                                                               |

| $\mathbf{C}$ | VPI | Exam    | ple Routines 169                                                                                                                                                                                                       |

|              |     |         | ystem Function                                                                                                                                                                                                         |

|              |     | C.1.1   | Calltf Routine                                                                                                                                                                                                         |

|              |     | C.1.2   | Compiletf Routine                                                                                                                                                                                                      |

|              |     | C.1.3   | Sizetf Routine                                                                                                                                                                                                         |

|              |     | C.1.4   | System Function Register                                                                                                                                                                                               |

|              | C.2 | Start o | of Simulation Callback                                                                                                                                                                                                 |

|              |     | C.2.1   | Callback Routine                                                                                                                                                                                                       |

|              |     | C.2.2   | Callback Register                                                                                                                                                                                                      |

|              |     |         | -                                                                                                                                                                                                                      |

| D            | FM                                    | I Simulators                                                   | 175  |

|--------------|---------------------------------------|----------------------------------------------------------------|------|

| $\mathbf{E}$ | Plu                                   | gin Extension Additional Material                              | 185  |

|              | E.1                                   | QEMU Monitor LED Plugin Device Property Output                 | 185  |

|              | E.2                                   | Plugin Device Structure                                        | 185  |

|              | E.3                                   | Plugin Device Makefile                                         | 186  |

|              | E.4                                   | LED Plugin Device                                              | 186  |

|              | E.5                                   | LED Plugin Device with IRQ                                     | 188  |

|              | E.6                                   | Adding IRQ Support in a Target QEMU Machine                    | 190  |

|              | E.7                                   | Blinking LED Plugin Device                                     | 191  |

|              | E.8                                   | Master LED Proxy Plugin Device                                 | 192  |

| $\mathbf{F}$ | Co-simulation Additional Material 195 |                                                                |      |

|              | F.1                                   | QEMU Monitor LED HW IP Proxy Interface Device Property Output  | t195 |

|              | F.2                                   | Virtual QEMU System Bus Slave Logic Example                    | 195  |

|              | F.3                                   | Verilog QEMU Virtual System Bus Slave IP Wrapper Example       | 197  |

|              | F.4                                   | Verilog QEMU virtual System bus Slave IP wrapper with IRQ Map- |      |

|              |                                       | ping Example                                                   | 201  |

|              | F.5                                   | Sequence diagrams                                              | 205  |

|              | F.6                                   | QEMU Co-simulation PLI library                                 | 208  |

| $\mathbf{G}$ | pq t                                  | theory                                                         | 219  |

# List of Figures

| 1.1  | Embedded development setup                                        | 2  |

|------|-------------------------------------------------------------------|----|

| 1.2  | Co-simulation overview                                            | 3  |

| 2.1  | Processor types                                                   | 9  |

| 2.2  | System on chip block diagram (Oliveira, 2013)                     | 11 |

| 2.3  | Embedded development platform block diagram (Oliveira, 2013)      | 12 |

| 2.4  | Virtual parallelization of two tasks                              | 16 |

| 2.5  | Operating system layers diagram                                   | 17 |

| 2.6  | Processes and threads block diagram                               | 18 |

| 2.7  | Virtual memory diagram                                            | 19 |

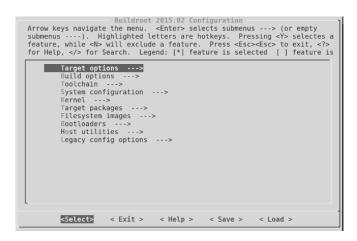

| 2.8  | Buildroot make menuconfig prompt                                  | 24 |

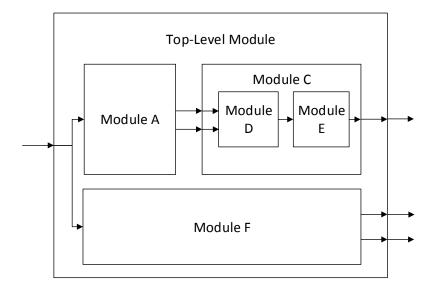

| 2.9  | HDL design diagram                                                | 26 |

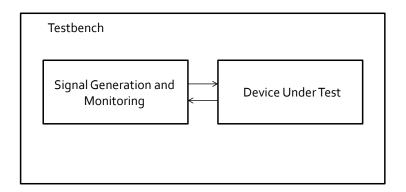

| 2.10 | HDL testbench diagram                                             | 26 |

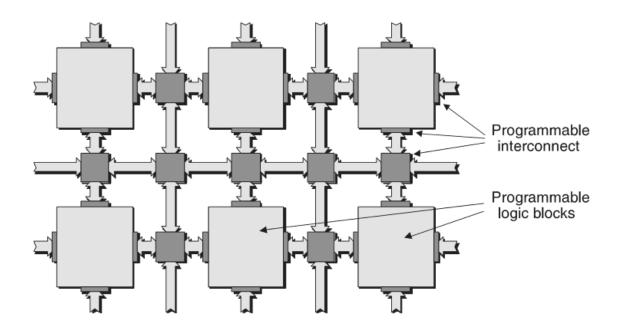

| 2.11 | FPGA internal architecture (Maxfield, 2009)                       | 28 |

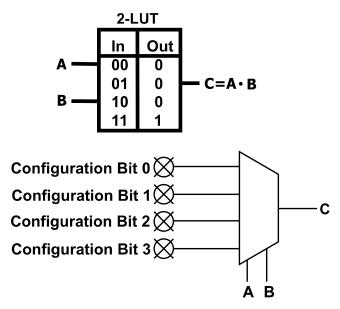

| 2.12 | FPGA LUT (Huffmire et al., 2010)                                  | 29 |

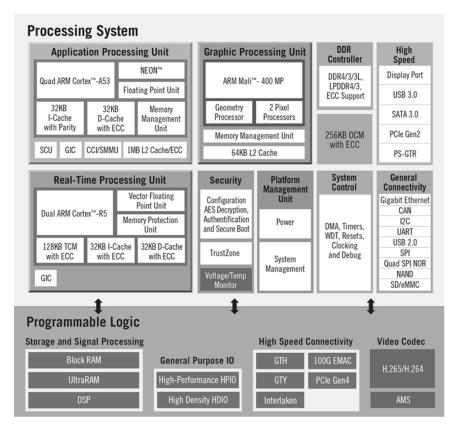

| 2.13 | Zynq® UltraScale+ $^{\rm TM}$ MPSoC architecture diagram (Xilinx) | 31 |

| 2.14 | Full system RTL simulation diagram (Zabołotny, 2012)              | 35 |

| 2.15 | RTL simulation with host software diagram(Zabołotny, 2012)        | 35 |

| 2.16 | RTL-Software co-simulation diagram(Zabołotny, 2012)               | 36 |

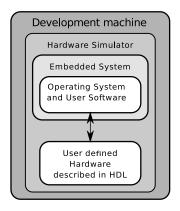

| 2.17 | Full system software simulation diagram(Zabołotny, 2012)          | 37 |

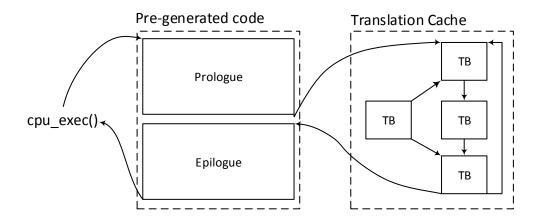

| 2.18 | Dynamic translation and caching diagram                           | 40 |

| 2.19 | Block chaining diagram                                            | 41 |

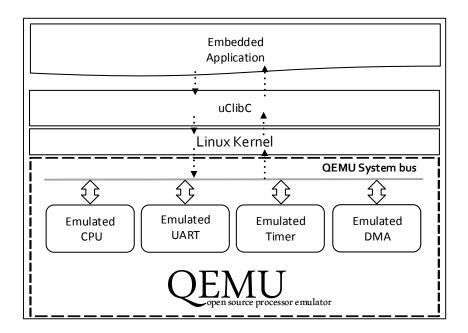

| 2.20 | QEMU emulation overview Diagram                                   | 45 |

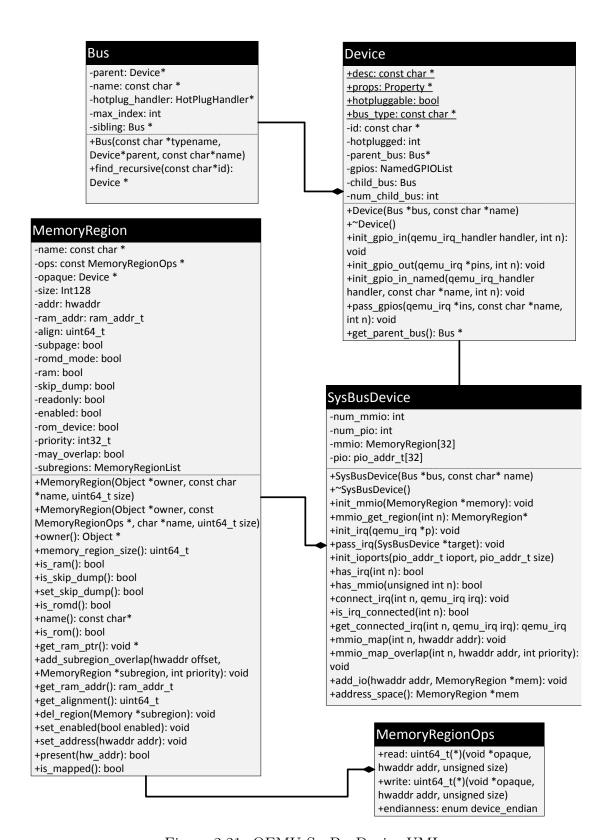

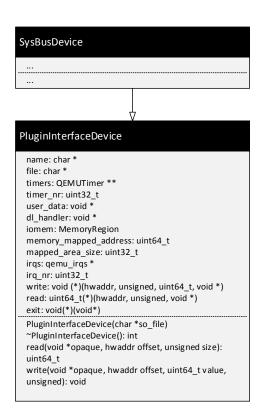

| 2.21 | QEMU SysBusDevice UML                                             | 47 |

| 2.22 | User-defined system function                                      | 51 |

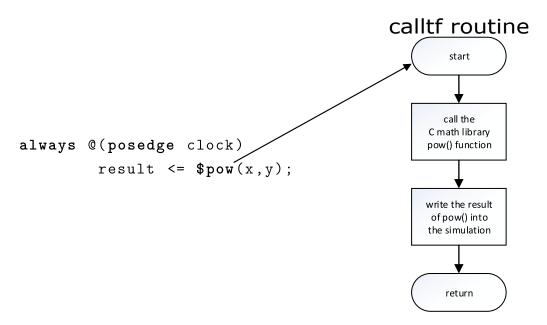

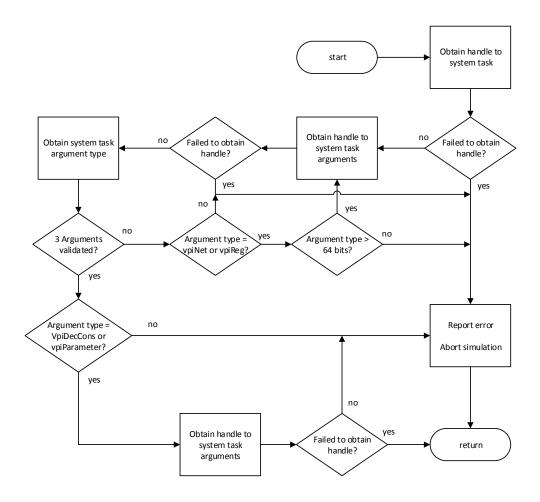

| 2.23 | Power calltf routine                                              | 53 |

| 2.24 | Power compiletf routine                                           | 54 |

| 2.25 | Power sizetf routine                                              | 55 |

| 2 26 | Simulation callback routine                                       | 56 |

| 2.27 | FMI simulation standards                                               |

|------|------------------------------------------------------------------------|

| 2.28 | Model exchange FMU interconnection (Otter et al., 2013) 58             |

| 2.29 | Model exchange FMU interface signals (Otter et al., 2013) 58           |

| 2.30 | FMI co-simulation                                                      |

| 2.31 | Co-Simulation FMU with slave interface signals (Otter et al., 2013) 60 |

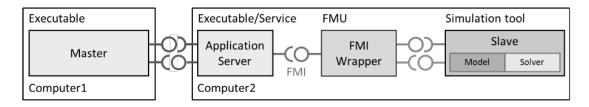

| 2.32 | FMI distributed co-simulation (Otter et al., 2013) 60                  |

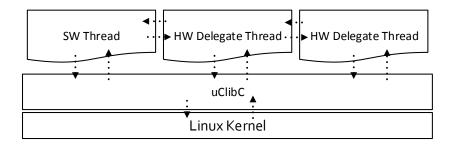

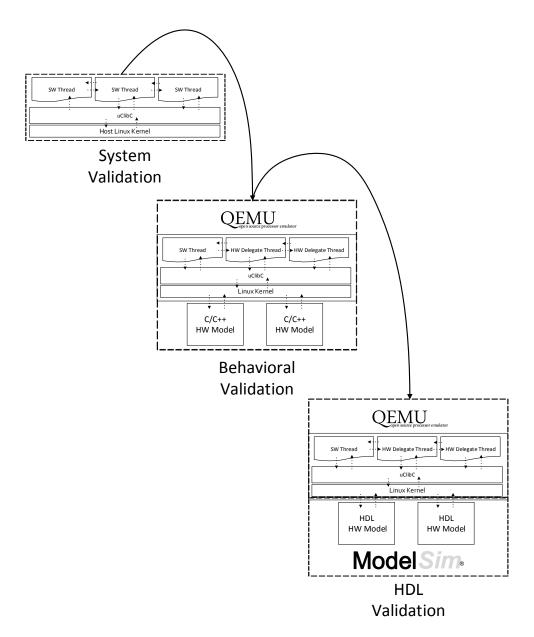

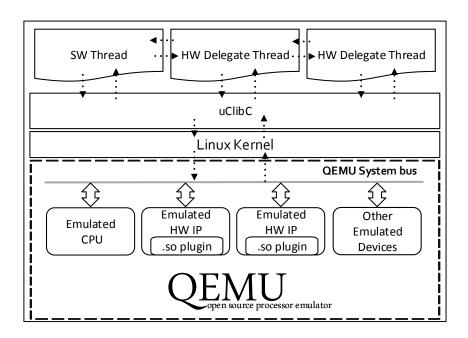

| 3.1  | Case of study overview                                                 |

| 3.2  | Hardware-software validation phases                                    |

| 3.3  | Plugin extension overview                                              |

| 3.4  | Plugin interface device UML                                            |

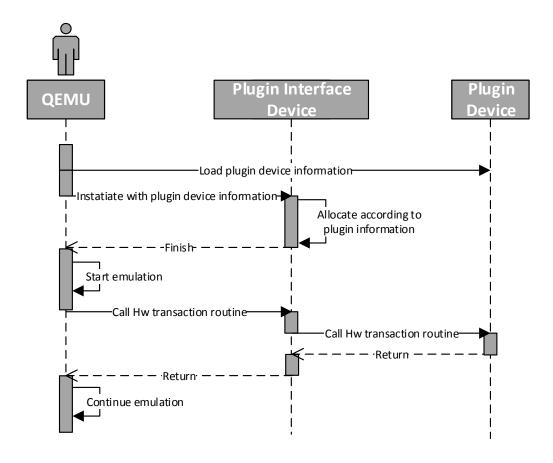

| 3.5  | Plugin device loading sequence diagram                                 |

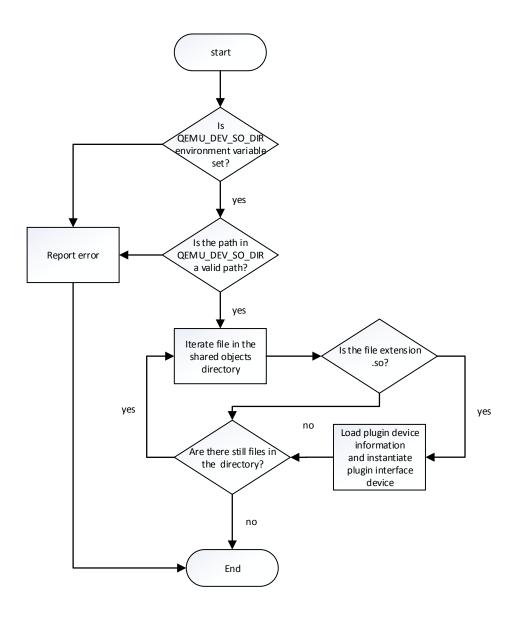

| 3.6  | Plugin extension initialization flowchart                              |

| 3.7  | Plugin transactions task graph                                         |

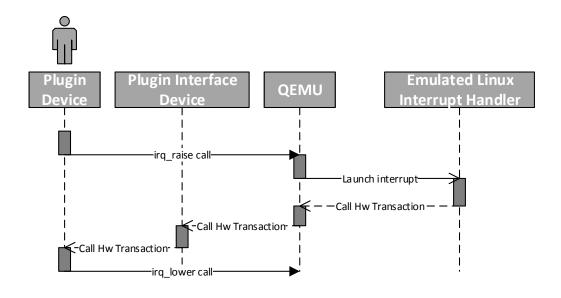

| 3.8  | Interrupt API sequence diagram                                         |

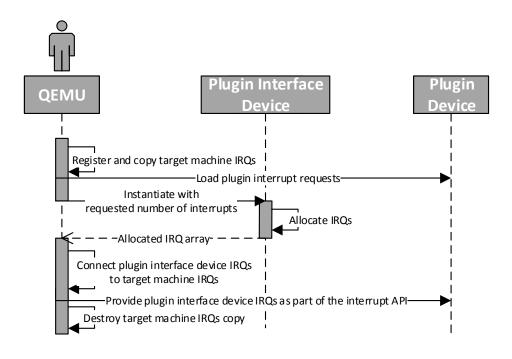

| 3.9  | Plugin extension IRQ allocation sequence diagram                       |

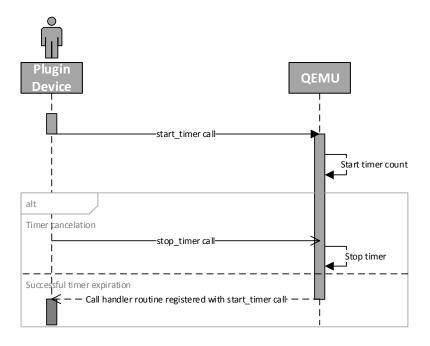

| 3.10 | Timing API sequence diagram                                            |

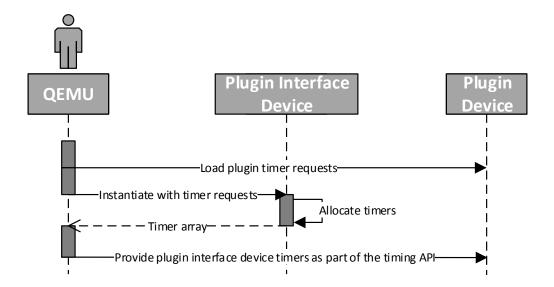

|      | Plugin extension timer allocation sequence diagram                     |

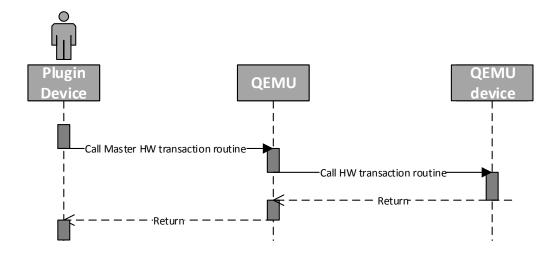

|      | Bus master API sequence diagram                                        |

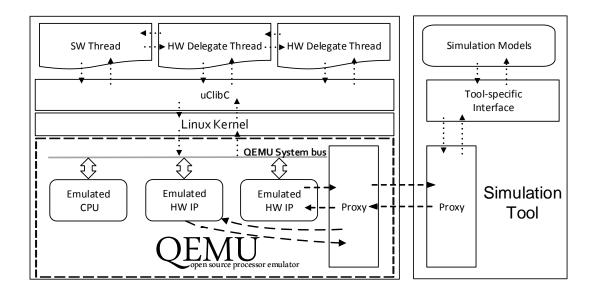

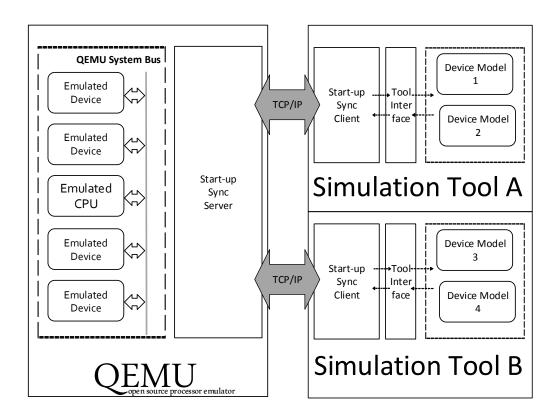

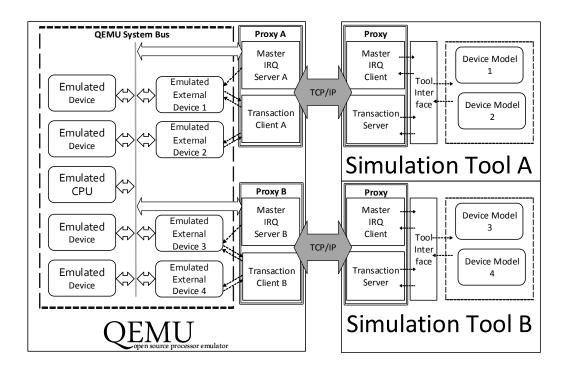

|      | External model extension overview                                      |

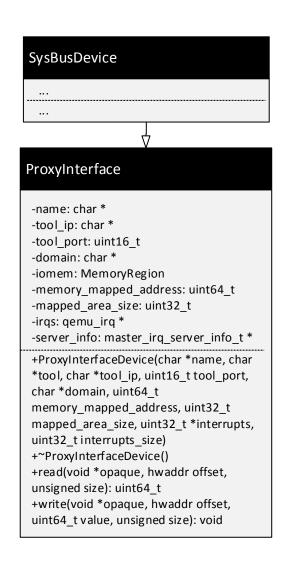

|      | Proxy interface device UML                                             |

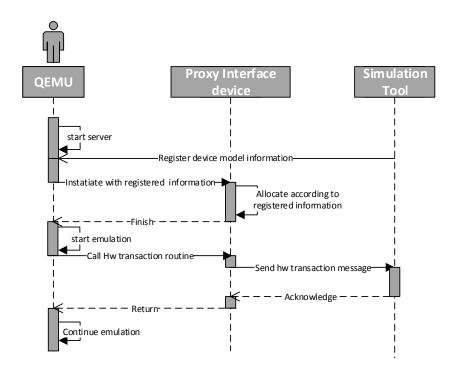

|      | External model loading and use sequence diagram                        |

|      | External model extension start-up synchronization overview 85          |

| 3.17 | External model extension runtime overview                              |

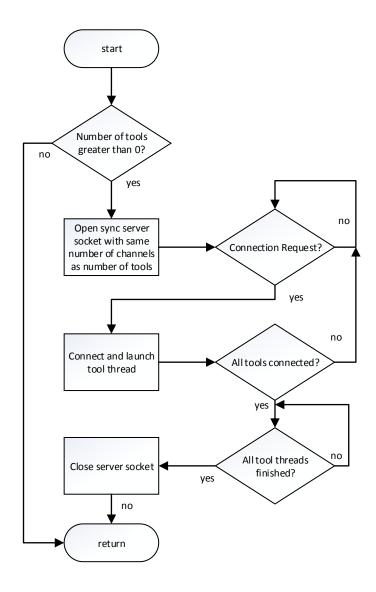

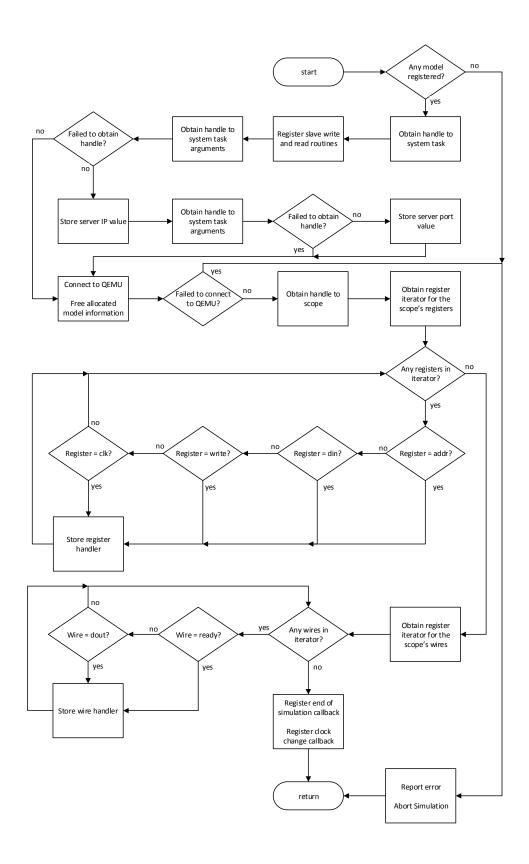

| 3.18 | Start-up sync server flowchart                                         |

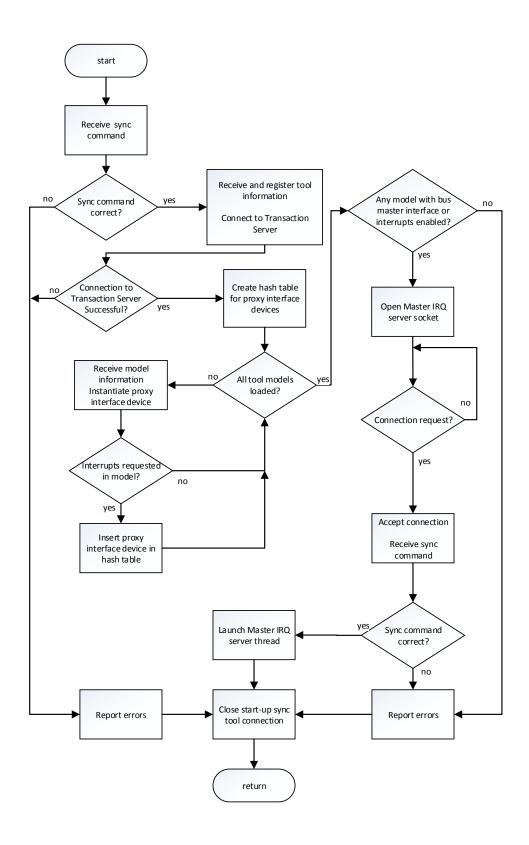

|      | Start-up sync server flowchart                                         |

| 3.20 | External model transaction timing sequence diagram 92                  |

|      | Master IRQ server thread                                               |

|      | External tool Interface                                                |

| 3.23 | QEMU co-simulation PLI library overview                                |

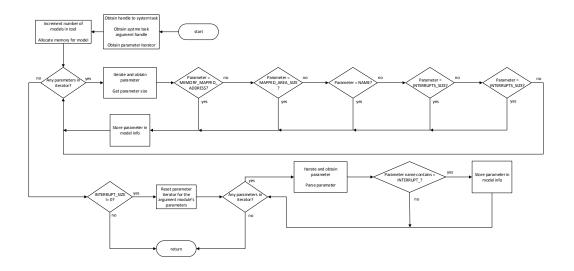

| 3.24 | PLI library initialization and transaction sequence diagram 98         |

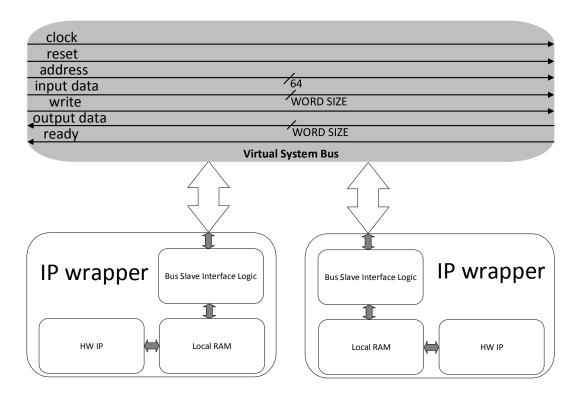

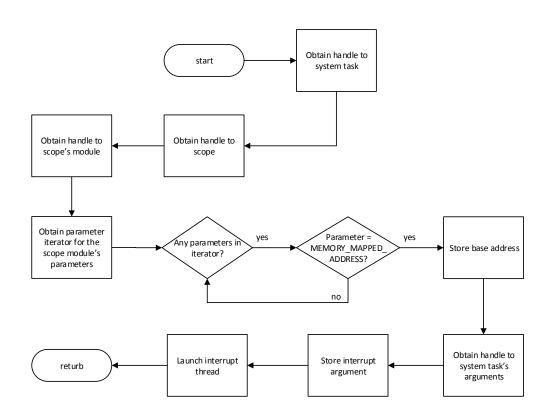

| 3.25 | Virtual QEMU system bus overview diagram                               |

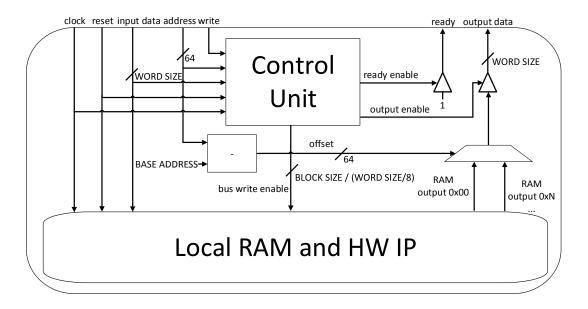

| 3.26 | Virtual QEMU system bus slave logic diagram                            |

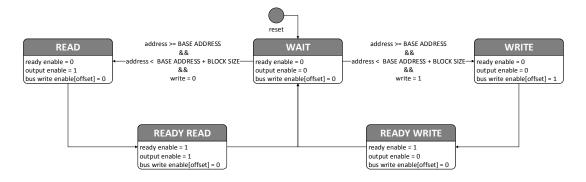

| 3.27 | Slave control unit state chart                                         |

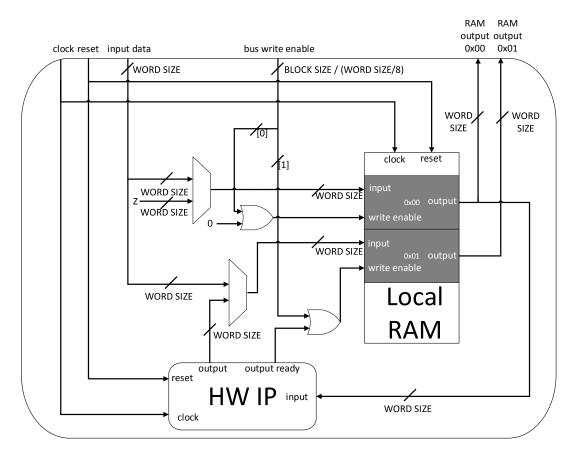

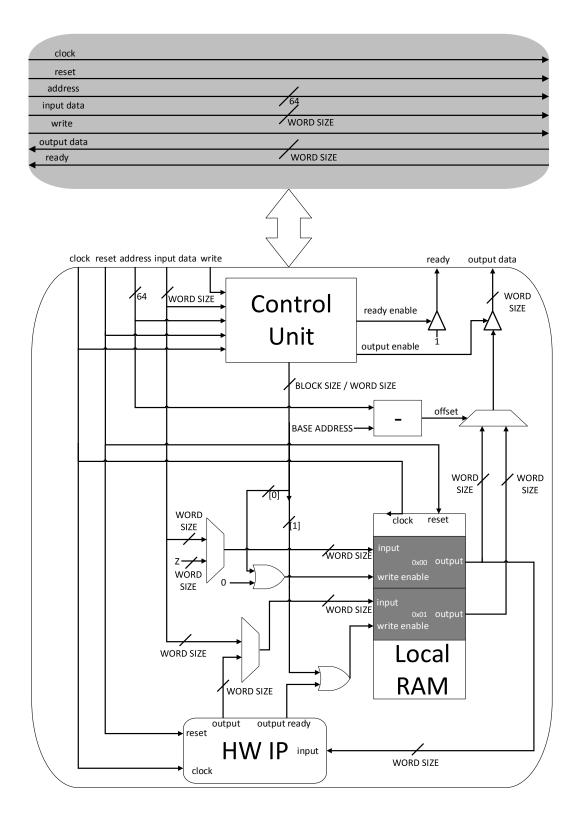

| 3.28 | Slave local RAM and HW IP diagram                                      |

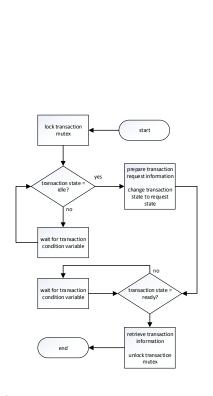

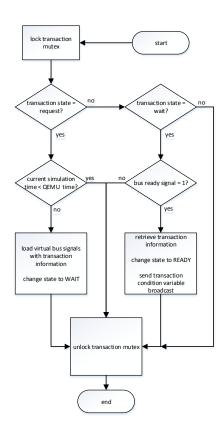

|      | PLI library transaction flowcharts                                     |

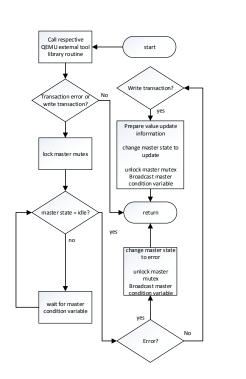

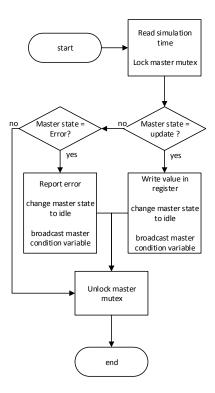

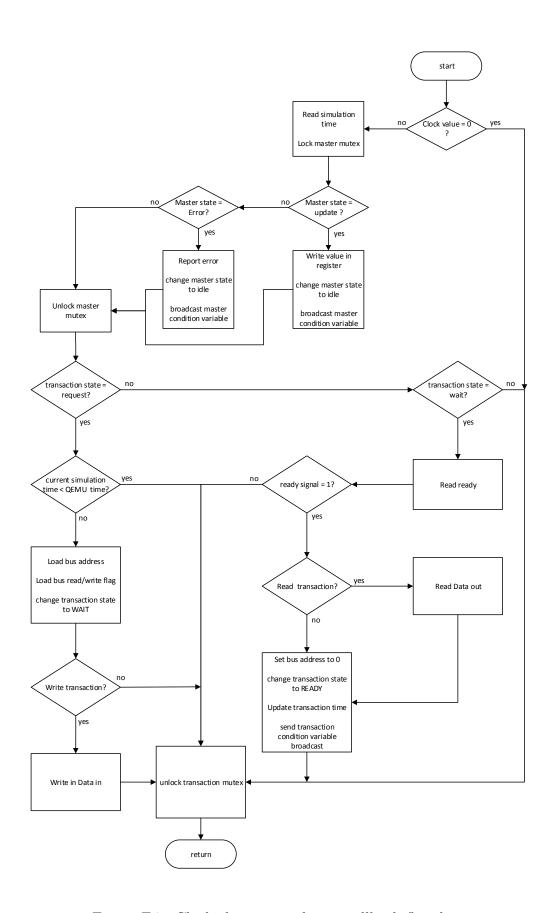

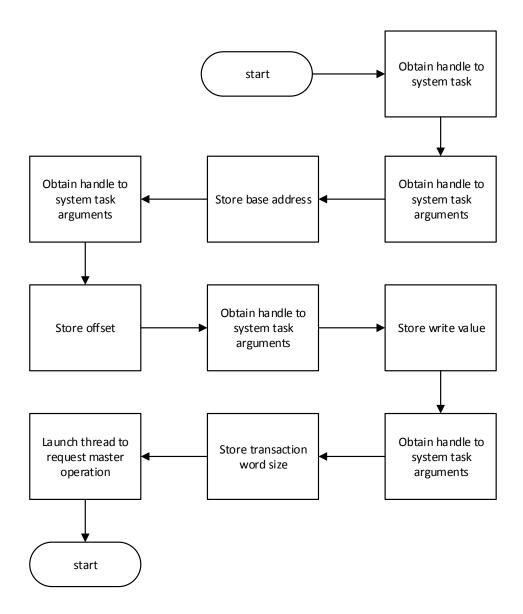

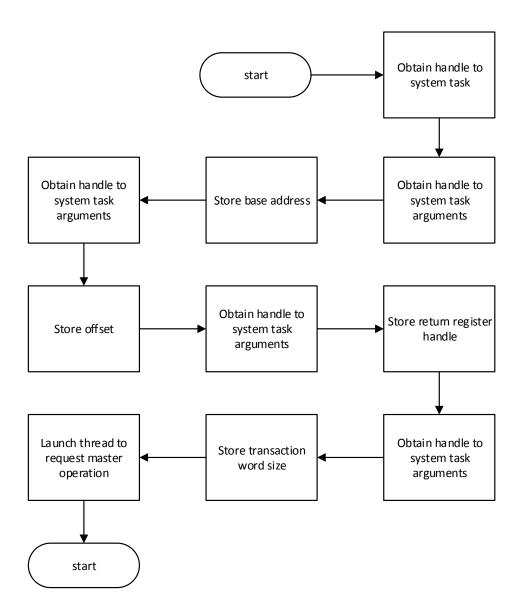

| 3.30 | PLI library bus master flowcharts                                      |

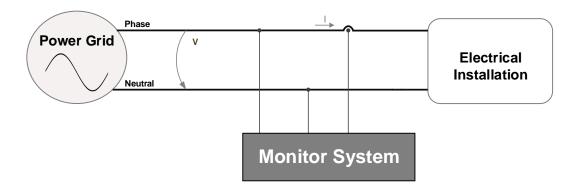

| 4.1  | Monitoring system overview diagram                                              |

|------|---------------------------------------------------------------------------------|

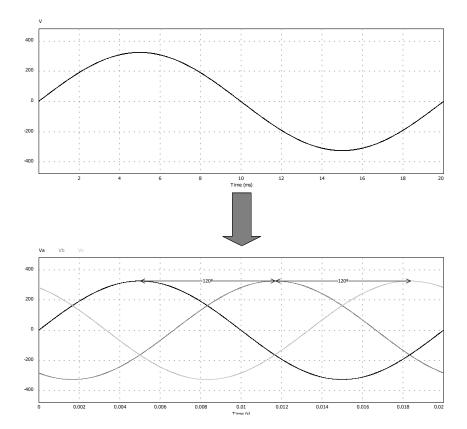

| 4.2  | 3-phase virtualization                                                          |

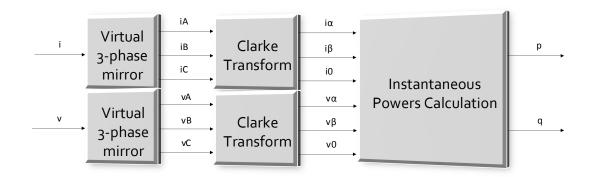

| 4.3  | Single-phase pq theory instantaneous powers blocks                              |

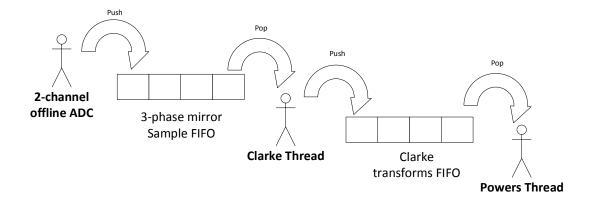

| 4.4  | Monitoring application task graph                                               |

| 4.5  | Monitoring application UML                                                      |

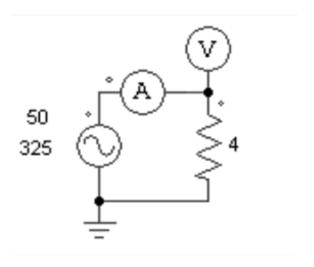

| 4.6  | PSIM single-phase grid with 4 Ohm resistive load                                |

| 4.7  | Monitoring application profile                                                  |

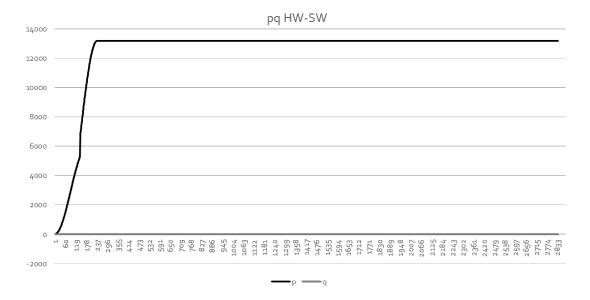

| 4.8  | p and q values outputs of the software-only application $\dots \dots \dots 117$ |

| 4.9  | p and q values outputs of the hardware-software application $\dots$ 118         |

| A.1  | Linux menuconfig kernel configuration                                           |

| A.2  | Linux menuconfig kernel features                                                |

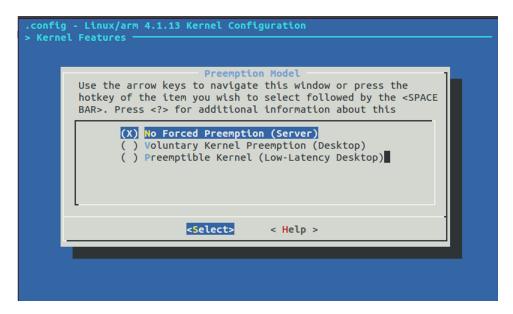

| A.3  | Linux menuconfig preemption                                                     |

| A.4  | Menuconfig Kernel                                                               |

| A.5  | Menuconfig kernel patch                                                         |

| A.6  | Linux menuconfig real-time preemption                                           |

| A.7  | Menuconfig kernel                                                               |

| A.8  | Menuconfig kernel extensions                                                    |

| A.9  | Menuconfig Xenomai/RTAI                                                         |

| A.10 | Menuconfig target packages                                                      |

| A.11 | Menuconfig real-time                                                            |

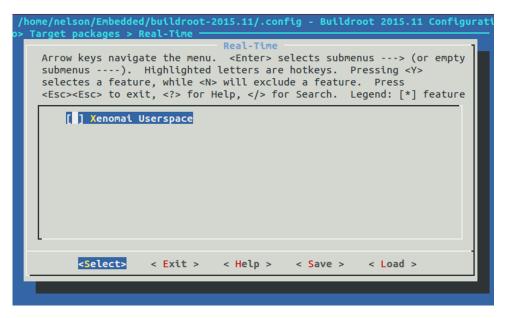

| A.12 | Menuconfig Xenomai Userspace                                                    |

| A.13 | Menuconfig toolchain                                                            |

| A.14 | Menuconfig enable C++ support                                                   |

| A.15 | Menuconfig target packages                                                      |

| A.16 | Menuconfig networking applications                                              |

| A.17 | Menuconfig DHCP daemon                                                          |

| A.18 | Menuconfig dropbear                                                             |

| A.19 | Menuconfig openSSH                                                              |

| A.20 | Menuconfig system configuration                                                 |

| A.21 | Menuconfig DHCP for eth0                                                        |

| F.1  | Virtual QEMU system bus slave logic example diagram 196                         |

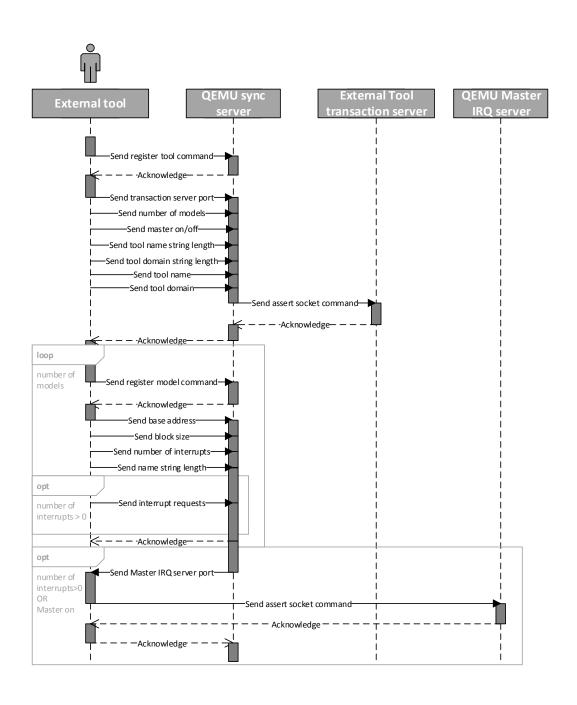

| F.2  | Start-up server synchronization sequence diagram 206                            |

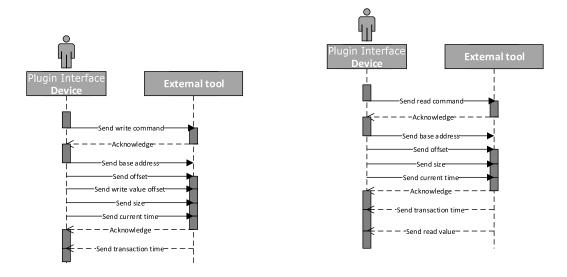

| F.3  | Proxy transactions sequence diagram                                             |

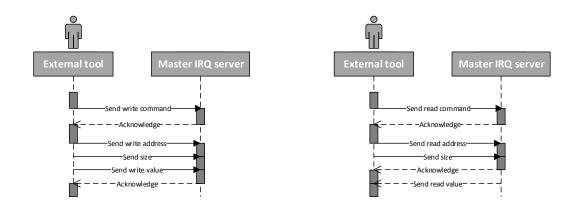

| F.4  | Master transactions sequence diagram                                            |

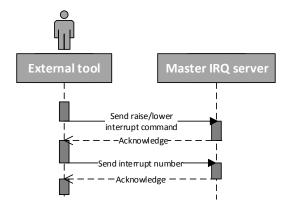

| F.5  | Interrupt sequence diagram                                                      |

| F 6  | End of simulation simulation callback flowchart 208                             |

| F.7  | Clock change simulation callback flowchart                                                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|

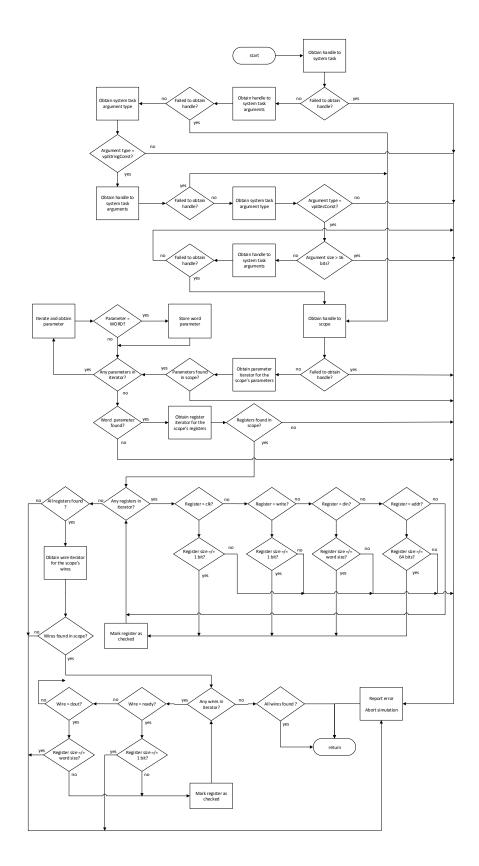

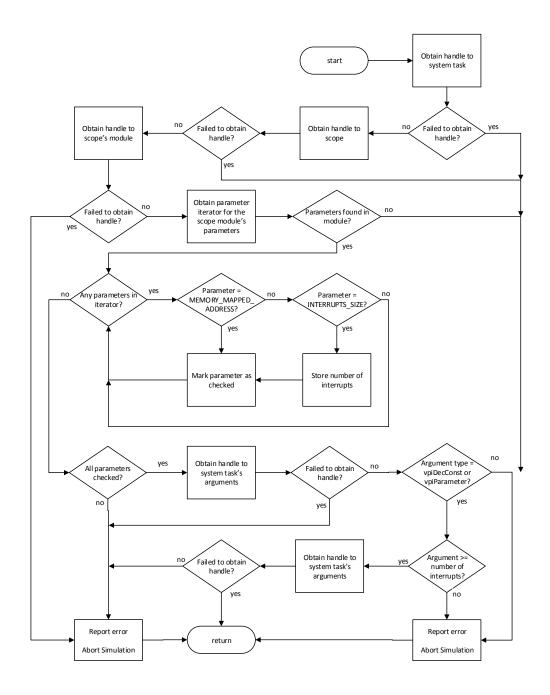

| F.8  | $qemu\_connect\ compiletf\ flowchart\ .$                                                                                                |

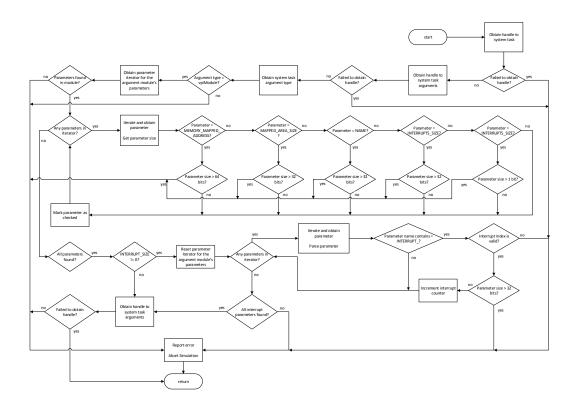

| F.9  | $\qquad \qquad $ |

| F.10 | $qemu_raise/lower_interrupt compilet flowchart$                                                                                         |

| F.11 | $\qquad \$ qemu_read_from_bus/write_to_bus compilet flowchart 213                                                                       |

| F.12 | $\qquad \qquad $ |

| F.13 | $\qquad \qquad $ |

| F.14 | $\qquad \qquad $ |

| F.15 | $\qquad \qquad $ |

| F.16 | \$qemu_read_from_bus calltf flowchart                                                                                                   |

# List of Tables

| 3.1 | Plugin device API                  |

|-----|------------------------------------|

| 3.2 | Interrupt API                      |

| 3.3 | Timing API                         |

| 3.4 | Bus master API                     |

| 3.5 | QEMU external tool library API     |

| 3.6 | QEMU co-simulation PLI library API |

| 3.7 | Bus master API                     |

| 3.8 | Interrupt API                      |

| D.1 | Simulators with FMI support        |

# Acronyms List

ACC ACCess

API Application Program Interface

ARM Advanced RISC Machine

ASIC Application-Specific Integrated Circuit

ASIP Application-Specific Instruction set Processor

AXI Advanced eXtensible Interface

BSP Board Support Package

CLB Configurable Logic Block

CPU Central Processing Unit

DCR Device Control Register

DMA Direct Memory Access

**DPI** Direct Programming Interface

DSP Digital Signal Processor

DTB Device Tree Blob

DTC Device Tree Compiler

DTS Device Tree Source

ESRG Embedded Systems Research Group

FDT Flat Device Tree

FMI Functional Mock-up Interface

FMU Functional Mock-up Unit

FPGA Field Programmable Gate Array

FSL Fast Simplex Link

GPIO General Purpose Input/Output

GCC GNU Compiler Collection

GPL General Public License

GUI Graphical User Interface

HDL Hardware Description Language

HLS High Level Synthesis

IDE Integrated Development Environment

I/O Input/Output

IP Intellectual Property

IRQ Interrupt ReQuest

JTAG Joint Test Action Group

LAB Logic Array Block

LCD Liquid-Crystal Display

LED Light Emitting Diode

LUT LookUp Tables

$\mathbf{MMC}$   $\mathbf{MultiMediaCard}$

MPI Message Passing Interface

OEM Original Equipment Manufacturer

OS Operating System

PC Program Counter

PCIe Peripheral Component Interconnect express

PLB Processor Local Bus

PLI Programming Language Interface

POSIX Portable Operating System Interface

QDEV QEMU DEVice

**QEMU** Quick **EMU**lator

QOM QEMU Object Model

RAM Random Access Memory

RC Release Candidate

RISC Reduced Instruction Set Computer

RTL Register-Transfer Level

RTOS Real-Time Operating System

SD Secure Digital

SDK Software Development Kit

SoC System-on-Chip

TCG Tiny Code Generator

TCP/IP Transmission Control Protocol/Internet Protocol

TF Task/Function

UART Universal Asynchronous Receiver Transmitter

UML Unified Modeling Language

VFS Virtual File System

VPI Verilog Procedural Interface

XML eXtensible Markup Languague

# Chapter 1

### Introduction

This chapter has an introductory purpose, presenting a brief contextualization of this dissertation's scope, as well as defining its motivation and main objectives. The main contributions of this project to the scientific community are also presented, with a clarification of the document's structure closing the chapter.

#### 1.1 Contextualization

We live in a world with technology growing and evolving day by day, with a high tendency for digital systems to take over everyday common tasks. With the rapid growth and intrusion of technology in human life, there is a also a growing need for better digital system solutions. Most digital systems in our every day lives are embedded systems.

An embedded system is a computational system that was designed for a specific purpose, being tailored for a particular set of tasks. Embedded systems are usually integrant part of a larger system, performing lower-level tasks, often interfacing with the physical world through control or monitoring systems, performing analogue data acquisition and driving circuitry that acts on the physical world, such as switches or motors. Embedded systems are everywhere, and can be thought of every digital system that's expected to hide a computational system inside, from MP3 players to printers to most domestic electric appliances. In fact, almost everything that is not a desktop computational system may be thought of as an embedded system.

Embedded development is usually made on available embedded development boards, that are frequently shipped with a development toolchain, comprising such tools as compilers, linkers, debuggers and even other tools that enable software development for the embedded platforms. Embedded software is most commonly developed in a host desktop platform, and later debugged and deployed in the target embedded platform. Figure 1.1 represents a traditional embedded development setup.

Figure 1.1: Embedded development setup

Unfortunately, many of the performance enhancing features in personal computer architecture, such as instruction pipelining and the use of caches in the memory system, which make them so fast also make it difficult to predict their performance at all times accurately. This is a problem in real-time embedded systems, which require applications with deterministic behavior.

Real-time embedded systems are systems with critical tasks that must meet deadlines, as far as execution is concerned. Some systems, such as anti-lock brakes in a car, have such real-time requirements that when not met may fail utterly and completely, and even be harmful to the user or its environment. For this reason, embedded software development is radically different from desktop software development, requiring different designs and a completely different set of skills from the developer. A modern technique to enhance real-time requirements satisfaction is the computational offload through dedicated hardware co-processors. This technique makes use of the inherent parallel nature of hardware, with custom hardware co-processor integration and the use of System-on-Chip (SoC)-based architectures made possible with recent advances in Field Programmable Gate Array (FPGA) technology.

Software application acceleration, using parallelization techniques and dedicated

hardware components, is often an optimization compromise in a cost-benefit relationship, during the migration of software processes to hardware IP dedicated cores or accelerators. In real-time applications extra care is needed in dealing with these issues, so that the real-time requirements of the application are not compromised. Through linear programming mathematical tools, it is possible to establish a good compromise, minimizing the desired system metric, like power consumption, temporal latency or silicon area.

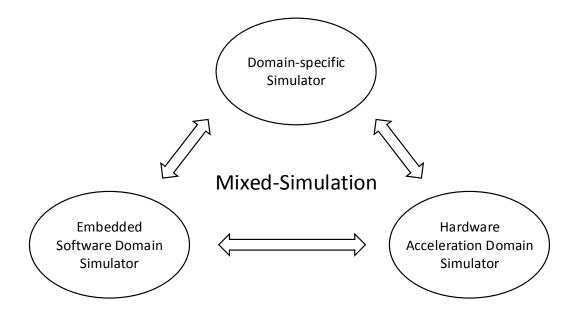

In order to characterize the temporal evolution on a system level, an integrated co-simulation environment where all metric costs are contemplated would be ideal. Such an environment would not only be useful by providing measurements of the system metrics, so the linear mathematical tools can aid in design optimizations, but also in system modeling. Figure 1.2 presents a diagram of a co-simulation environment overview.

Figure 1.2: Co-simulation overview

Usually, hardware-software co-design is a long process of iterative nature. If the system is modeled and simulated on separate application domains and later implemented and debugged physically, the development time can grow exponentially. An isolated validation, as far as application domains are concerned, does not guarantee integral system functionality, and with an integrated co-simulation environment, system problems can be detected early before moving to the physical implementation phase.

By adopting a design flow aided by co-simulation, the the development process is sped up, and also resource independent, since the system can be developed in its entirety in a host platform without being bound to a physical target platform. This kind of development has some obvious benefits, as the system can be modeled first, profiled and analyzed later according to certain metrics, and only afterwards is a target platform selected. Also, design teams with limited available prototypes are not slowed down by limited platform resources.

### 1.2 Motivation and Objectives

Power electronic devices often need fast-responding and deterministic controllers, requiring systems with hard to meet real-time constraints. A modern technique to mitigate latencies and non-determinism intrinsic to operating systems in the context of real-time embedded systems is to use hardware acceleration for computational offloading. Hardware accelerated embedded systems development is usually a long iterative process with conventional design flows being slow and with difficult system integration on the various application domains. Local caches are commonly used to stimulate and validate each application domain in controllers of this nature, which implies lengthy development cycles in most cases.

Currently, there is no tool available on the market that allows to simulate domain crossing interactions, and support a design flow based on co-simulation. As such, one of the main objectives of this project is to develop a simulation environment that supports domain crossing validation. With the concept of co-simulation being tackled in the Embedded Systems Research Group (ESRG) of *Universidade do Minho*, an idealization on how a simulation framework for hardware accelerated embedded systems could greatly improve future project development processes began to surface. This dissertation is a product of that vision, aiming to be the first pragmatic step towards such a framework.

#### 1.3 Contributions

This focus of this dissertation is placed on embedded platform development with the help QEMU. QEMU, as an open-source project, is subject to any kind of modifications and changes by anyone, with development being made by a large community, including such contributions as Xilinx itself, a major company of FPGA chips and SoC-based solutions. As such, this document tries to emphasize what advances could be made in this regard, and tries to introduce new concepts that hopefully improve development of hardware accelerated embedded applications in the long run.

As such, a scientific article is also planned for publication to complement this dissertation and reach the scientific community.

#### 1.4 Dissertation Structure

This document presents the development of simulation tools extensions and libraries that allow QEMU to be used as a full-system emulator in a real-time hardware accelerated application context. Its content was divided in six chapters that are going to be briefly presented.

The second chapter introduces the reader in the most common tools and methodologies of hardware accelerated application development for embedded systems. It presents what technologies and tools are available for this kind of development, as well as the commonly followed design flows, focusing on what choices can be made to adopt a simulation based environment, backing up eventual development choices made in this project. Special attention is given to QEMU, exposing its features and possibilities, namely in embedded platform emulation. Verilog simulation interface standards are also approached, specifically Verilog PLI. Finally, co-simulation extension standards are mentioned, bringing up their relevance in the context of this dissertation.

The third chapter presents development work that was done in terms of extending simulation environments capabilities, presenting the developed extensions. Developed content presentation is functionality oriented, providing an insight on how development was made, as well as on how to make use of these mechanisms. Examples are given whenever possible, being mentioned as work is presented to help the reader in understanding how to use the provided interfaces as a developer.

The fourth chapter presents a case of study, providing a practical example on how the extended simulation environment's features work, highlighting what advantages does this kind of development bring in embedded hardware accelerated application development. The chosen case of study was in the power electronics domain, being an instantaneous power monitor based on the pq theory.

The document's closing chapter discusses results and conclusions concerning developed work. Future work is also mentioned, clarifying what can be further done in terms of giving this work continuity and further improve it to provide a full hardware accelerated embedded system validation framework.

# Chapter 2

### State of the Art

In this chapter, background is provided regarding the technologies and methodologies within the scope of this dissertation. Embedded systems are briefly contextualized, with a strong focus on topics like embedded systems with Operating Systems (OSs) and real-time embedded constraints. Hardware acceleration and its common design flows and simulation approaches to embedded design are also discussed, with deep details of two important domains in the developed work, the QEMU and the Verilog Programming Language Interface. Finally, the Functional Mock-up Interface is an important standard for co-simulation and model interchange widely adopted in the industry's most commonly used simulators, and as an important reference for this project's system design, it is also covered.

### 2.1 Embedded Systems

Currently, embedded systems can be found everywhere in our every day lives, ranging from consumer electronics and electrical appliances to office automation, industrial automation, military defense systems, transportation systems, aerospace systems, medical systems and so forth. Out of more than six billion microprocessors produced in 2002, more than 98% were microprocessors for embedded purposes, rather than personal computer purposes (Turley, 2002). These numbers may very well have even increased with the smartphone and tablet business boom of recent years, and subsequent rise of popularity of the ARM architecture, resulting in ever greater demand in the embedded market.

#### 2.1.1 Definition

An embedded system is an applied computer system, as distinguished from other types of computer systems such as personal computers or supercomputers. However, the definition of "embedded system" is fluid and difficult to pin down, as it constantly evolves with advances in technology and dramatic decreases in the cost of implementing various hardware and software components. In recent years, the field has outgrown many of its traditional descriptions (Noergaard, 2013). Some of its traditional descriptions may include:

- Embedded systems are computational systems with limited hardware resources, such as memory or processing performance;

- Embedded systems are simpler computational systems, with less software abstraction, with no operative system, or a limited one;

- Embedded systems are computational systems where software and hardware are designed designed for a specific task, often running applications with limited or no user interface at all.

- Embedded systems are computational systems that are embedded as part of a complete device often including hardware and mechanical parts;

- Embedded systems are systems which hide computational systems inside, but are not thought of as computers;

While most of these rather outdated definitions are not necessarily false, some of them do not cover all of the modern embedded systems. For instance, a modern smartphone, generally classified as an embedded system, does have a complex OS, fairly acceptable hardware resources and is not designed for a single specific task. Summarily, a good way of defining an embedded system is considering as an embedded system any system that includes a computer, but is not designed to be a general purpose desktop personal computer.

Generally, modern day embedded systems can be thought of as low-end, middle-end and high-end embedded systems regarding their complexity, with processing units ranging from simple 4-bit processors to complex multi-core 32 and 64 bit architectures, and software ranging from bare-metal applications to complex OSs running multiple applications. Some examples of embedded systems are:

• Low-end:

Digital thermostats, automatic vending machines, electrical toothbrushes, traffic lights, generic remote controls, washing machines.

#### • Middle-end:

MP3 players, DVD players, TVs, cellphones, routers, printers, digital cameras.

#### • High-end:

Smartphones, smart TVs, tablets, cars, trains, airplanes.

#### 2.1.2 Embedded Processors

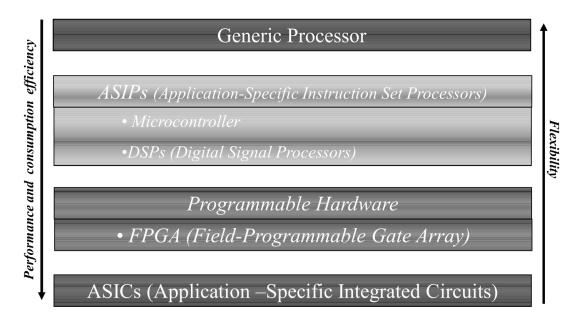

The main component of an embedded system is the computational processing unit. Without it, it wouldn't even qualify as an embedded system, since an embedded system must be a computational system. This does not mean, however that this processing unit must me a programmable processor. There are several types of processors, and unlike desktop computers, a processor with lots of instructions and capabilities does not mean that it is best suited for an embedded purpose. Figure 2.1 presents the different kinds of processors, in relation to their flexibility and performance and consumption efficiency.

Figure 2.1: Processor types

At the top, general purpose processors, also known as microprocessors, are the most flexible type of all processing units. These are the Central Processing Unit (CPU) used in personal computers, and are the least efficient of them all, as far as energy consumption-computation performance ratio is concerned. The flexibility they provide instruction-wise is greatly suited for personal computers, but unnecessary in most embedded scenarios. For this reason, and due to their high power consumption they are not a very well suited to embedded systems, being often overlooked and quite rightly so.

At the other end of the spectrum are Application-Specific Integrated Circuit (ASIC). These processors are the least flexible of all, and are hardwired to carry out a specific task, not being programmable in any way. With very high time-to-market and development costs, it is only used if maximum efficiency and performance is necessary and a large number of system copies can be sold, relying on an economy of scale.

FPGA provide a low-cost solution to ASIC, albeit a more power hungry one. These processors are more flexible than ASIC, as their internal hardware connections may be reprogrammed. As a low-cost alternative, these are frequently used to prototype and debug ASIC designs during the development process, as the manufacturing costs of creating a new ASIC mask design are what make the technology expensive.

Lastly, Application-Specific Instruction set Processor (ASIP) are flexible processors which are capable of running software instructions, but are not as generic as microprocessors, being a compromise between single-purpose processors such as FPGA or ASIC and microprocessors. These processors are particularly optimized for a particular class of applications and often have hardwired components additional to the actual processing unit, such as memory blocks or other peripherals. For these reasons, they are often the ideal choice for embedded systems, and comprise the most frequent choice in embedded system design. Some examples of ASIP are:

#### • Microcontrollers;

Microcontrollers are chips that integrate microprocessors, usually 8 to 16 bits or 32 bits, and memory blocks in the same package. They are generally aimed towards low-end control-oriented embedded systems, being packed with little memory and sometimes even additional peripherals, to provide a complete single chip control solution.

#### • Digital Signal Processors (DSPs);

#### Digital Signal Processors (DSP);

DSP are a particular set of ASIP which are optimized for data streamoriented applications, often including dedicated instructions and peripherals that are suited for digital signal processing, such as floating-point units.

#### • SoC;

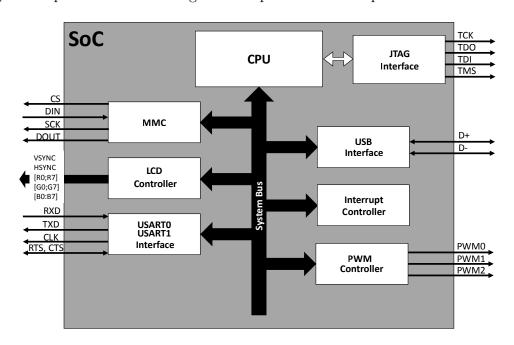

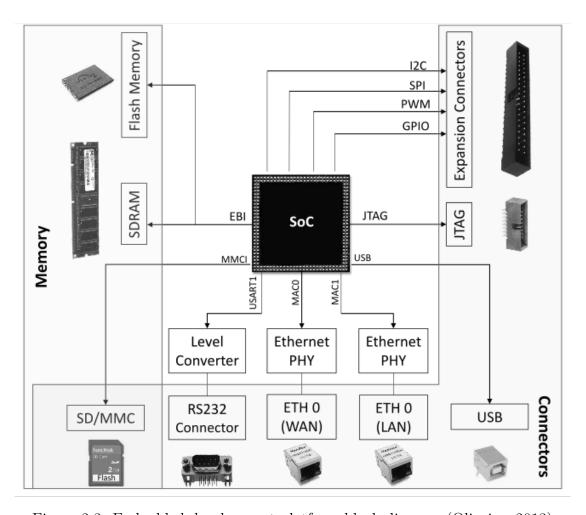

An SoC integrates all components of a computer system in a single chip, and is best suited for middle-end/high-end embedded purposes, being one of the most popular choices in embedded system design nowadays. SoC may be comprised of one or more microprocessors, usually 32 or 64 bits, DSPs, microcontrollers, memory blocks, peripherals such as timers and external interfaces, such as USB or Ethernet, also found in some microcontrollers.

Figure 2.2 presents a block diagram of a possible SoC chip.

Figure 2.2: System on chip block diagram (Oliveira, 2013)

#### 2.1.3 Embedded Development

Embedded system physical hardware and respective boards are often designed and developed along with software, being tailored and designed specifically for the target scenario. However, it is not practical to wait until the hardware prototype is finished to develop software, and not a very good idea to mix software with board development, as it may be hard to trace system faults and identify them as a software bug or a board malfunction.

To develop and debug software more easily, development platforms are used as a more practical way of prototyping embedded systems. Embedded development platforms are boards that are designed often by the processing chip's own manufacturers, containing a general set of components and interfaces that complement the chip's functionality, such as memories, Ethernet connectors, MultiMediaCard (MMC) card connectors and General Purpose Input/Output (GPIO) expansion connectors, which combined will produce a platform that can be used to easily prototype embedded systems. Figure 2.3 presents a block diagram of a possible development board designed around an SoC.

Figure 2.3: Embedded development platform block diagram (Oliveira, 2013)

Software development for these platforms is usually done on a host desktop system, where software is coded and later transferred to the target embedded platform. To be able to do all of this, a toolchain is usually provided for the target architecture. A toolchain comprises programming tools needed to effectively use the target platform, such as compilers, linkers, debuggers, loaders and other utilities. The act of compiling software for an architecture that is different from the one where compilation is being done is called cross-compiling, with embedded toolchains generally comprising cross-compilers and other such utilities.

After a prototype is developed and ready for production, the system may be integrated in a final board or boards which are tailored for the application's purpose, and possibly leaving out elements present in the development platform that are not used. Consider, for instance a router. If the development board included an LCD, it should be left out of the final product board, as it is not used by the router.

## 2.1.4 Real-Time Embedded Systems

Real-time embedded systems are a special kind of systems which are designed to perform certain critical tasks and satisfy specific time constraints, being referred to as deadlines. This means that these constraints drive the design, and if system responsiveness is limited, the whole system could be compromised.

Sometimes, real-time requirements are mistaken with high performance, which is not true. For instance, consider two chess software application scenarios are considered, one for a tournament with timed moves and one for personal recreational purposes with indefinite time to compute a move. In both applications, high performance is desired. However, in the tournament application, if a decision is not made in the given time and the deadline is not met, the computer loses the game. Thus, the correctness of a real-time embedded system depends not only on the results produced, but also when they are produced.

Real-time embedded systems may be classified in three categories: hard real-time, firm real-time and soft real-time systems.

Hard real-time systems, are systems in which missing a deadline results in total system failure. Examples of hard-real time systems are a nuclear reactor control system, or anti-lock brakes on a vehicle. In both these cases, if the system does

not meet its required deadlines, total system failure occurs with very harmful consequences. Other examples of hard real-time systems include pacemakers and avionic applications.

Firm and soft real-time systems, are systems that do not fail if a deadline is not met, but their services degrade considerably with missing deadlines. Further distinction is made between firm and soft real-time systems, regarding a result's validity after the given deadline. If a system's computed result is completely invalidated by not being produced in its given time window, it is considered firm real-time. If the a system's computed result is still valid, although with reduced value after failing to meet a deadline, it is considered soft real-time. An example of a firm real-time system could be a weather forecast system. If a deadline is missed, no system failure will occur and the system may continue making predictions. However, if the system makes a late prediction, like predicting a storm that has already happened, it is totally invalidated and has absolutely no use. An example of a soft real-time system can be a nuclear reactor user interface. Although the nuclear reactor control system itself is a hard real-time system, providing an interactive man-machine interface is not as critical, and delayed results, although degrading the system's value, are still valid.

A real-time embedded system should be dependable, and although not exclusive to real-time embedded systems, some of these characteristics are particularly desirable when designing such a system:

## • Reliability;

Continuity of service delivery while in use, that is, the probability of the system working properly since it started working after start-up. If a system is reliable, it won't need to be checked often, that is, if it it's down and needs a reset.

## • Maintainability;

Probability of the system working properly a few moments after an error occurrence, that is the impact a system error has on the system, and how quickly it can be properly running again.

#### • Availability;

Readiness for use when needed, that is, probability of the system working at a given time instant.

## • Safety;

Does not cause catastrophic effects on the environment or user as a consequence of failure.

### • Security.

Provides communication confidentiality and authentication.

Real-time embedded system development is an especially difficult area, requiring varied skill sets from engineers, from knowledge on compiler technology and debugging techniques to hardware devices and knowledge on programming techniques that enhance system responsiveness, all the while keeping in mind timings and not compromising its real-time requirements. Real-time system design often deals with concurrency, with multiple tasks being executed with different priority levels.

# 2.2 Operating Systems

Operating systems are software that manage machine resources, and provide several abstractions and commonly shared application services that create execution environments that aim to facilitate application development. As embedded technology grew to meet ever growing system demands, the adoption of OS for system development became very common, being an integral part for several embedded systems.

# 2.2.1 Concurrency

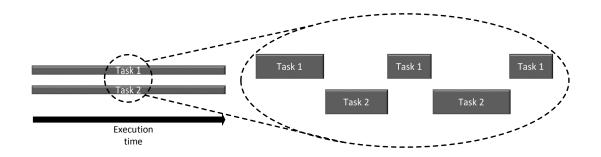

Responsiveness and concurrency are often important aspects of an embedded system. This may prove to be a paradox, since responsiveness means that the system should respond quickly to external events, and concurrency means that several tasks must be carried out simultaneously. Microprocessors are capable of executing only one instruction at a time, and if an external event triggers a processing task, it should mean that the processor would be unavailable for any other external events. However, there are techniques to overcome this limitation. Virtual parallelization is a concurrent programming technique that shares multiple task execution code to achieve an illusion of concurrent execution. Figure 2.4 presents an example diagram of two tasks being executed concurrently.

Figure 2.4: Virtual parallelization of two tasks

Two tasks are executed by the processor once at a time, with CPU execution jumping from one task to the other, with each task being executed in little bits. By not being confined to executing a task all the way to the end exclusively, the system is not held until the task finishes and its responsiveness is not compromised. Task switches can be implemented using timer interrupts, with scheduling code being ran in the interrupt to decide which task code should the interrupt return to. If the task switches are frequent enough, it may seem as though the system is running two tasks in parallel. This is the basis of the multi-tasking paradigm used in most computational systems nowadays, and it is one of the most important aspects of an operating system.

At its absolute most basic form, an OS can be a software program that allows for task code implementation, running a scheduler that decides which task should be in execution. There is a plethora of scheduling algorithms and techniques, with the two main groups being cooperative scheduling and preemptive scheduling.

In cooperative scheduling, it is up to the tasks to make system calls that give up execution to other tasks. In this scheduling model, there is no need for timer interrupts and OS intervention, as it is up to the tasks to yield execution and cooperate among them to maintain a balanced system execution. The downside of this model is that a badly implemented task may compromise the system and hold up the processor. Although now rarely used in large OS it was once a widely popular scheduling scheme.

In contrast, preemptive scheduling is a scheduling scheme that implements OS intervention, usually through a timer interrupt that runs scheduling algorithms and decides which task should run next. This strategy provides some abstraction to the user, as tasks can be implemented without having in mind system management,

also ensuring better guaranties that a task will not hold up the processor. Nowadays most large OS have scheduling algorithms and techniques that fall under the preemptive category, from Windows and Mac-OS to Linux.

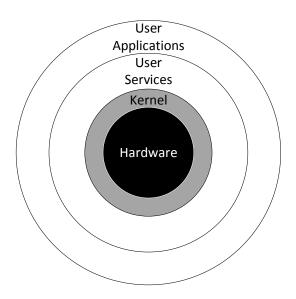

## 2.2.2 Kernel and User Spaces

An OS is a software program that allows for concurrent task execution, through scheduling algorithms that implement virtual parallelization. However, most OS are much more complex, managing software and hardware resources and providing a set of services that are common to most applications. In modern OS, the kernel is the core of the OS and has privileged access to the hardware resources, managing memory access, scheduling application execution in the CPU, and other hardware related responsibilities. Most modern large OS implement at least two execution spaces in them: kernel space and user space. Figure 2.5 presents a diagram of the common software layers of an OS.

Figure 2.5: Operating system layers diagram

Kernel space runs code that accesses hardware like memory and I/O, providing an interface through system calls to upper layers. User space runs OS services that do not require direct hardware access, like network services and user interface services like Graphical User Interfaces and command line shells. User applications are also ran in user space, often being thought of as another layer, given that these applications frequently run on top of user space OS services.

This architecture of kernel and user space is not set in stone though, with existing several approaches and architectures that run some services in user space, and others that run the same services in kernel space. The two main type of kernels are microkernels and monolithic kernels.

Microkernels contain the minimum amount of services running in kernel space, with most services being ran in user space, whereas monolithic kernels run most of their services in kernel space. Regardless of being implemented in user space or kernel space, most OS provide a set of basic services, using a set of concepts that make possible the modern computing systems that we see today.

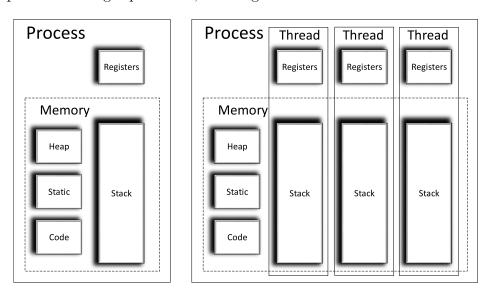

#### • Processes and multi-tasking

Perhaps the most important feature of an OS as was previously covered, is the implementation of schedulers and multi-tasking, which is essential to system responsiveness and concurrent application execution. Besides of what was previously covered, most modern OS also implement the concept of processes and threads. A process is a program in execution, often with its own memory space. Threads are also a common concept, with a process being composed of one or more threads. Figure 2.6 presents a diagram of a common architectural approach of processes and threads in an OS, with two processes being represented, one single-threaded and one multi-threaded.

Figure 2.6: Processes and threads block diagram

Processes are programs in execution, with separate memory spaces and and execution contexts. Execution context is illustrated with a combination of registers and stack, representing the CPU state for each task. OS processes

often implement a hierarchy within the multi-tasking model, implementing internal sub-tasks, called threads. Threads are tasks within processes which share the same memory belonging to their respective process, but have their own execution context, enabling for concurrent execution and virtual parallelism within a single process.

## • Virtual Memory and Memory Management

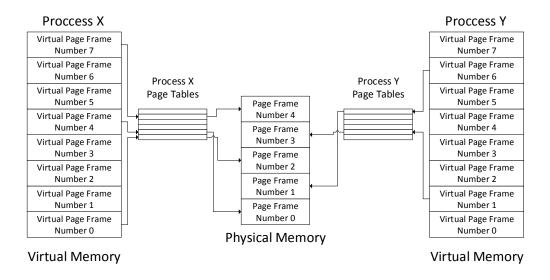

Virtual memory is a technique that greatly improves system performance, usually tightly coupled with the concept of processes, although it is also used in single address space OS. With this technique a process assumes that the whole system's memory is free, liberating processes from the responsibility of managing memory addresses. Processes' memory addresses are interpreted by the OS as virtual addresses and then translated to actual physical addresses. Figure 2.7 presents a diagram of two processes with their respective memory addresses being mapped into physical memory.

Figure 2.7: Virtual memory diagram

Usually, memory is divided into unitary blocks commonly referred to as page frames. In OS that employ separate memory address spaces for each process, such as the one illustrated, page tables must be associated with processes. This is done so, because page tables must supply different virtual memory mappings for different processes, as they may use identical virtual addresses.

Virtual memory may be augmented with secondary storage such as hard disks, MMC and Secure Digital (SD) cards, with the two latter being the

most common choices in embedded systems. Memory page frames can be swapped between the system's main memory and secondary storage, being moved in and out of the main memory according to the needs of the process that is in execution.

In this case, the page tables must keep additional information for each page, often in the form of bits like the present bit and the dirty bit, that represent their states in the secondary storage memory space. The present bit indicates what pages are currently present in physical memory or secondary storage devices, allowing the OS to know how to treat these different pages, like whether to load a page frame from secondary storage devices and page another page frame in physical memory out. The dirty bit allows for performance optimization, and is used to signal if a page frame that's loaded onto the main memory has been changed since loaded from the secondary storage device. If not, when the page frame is paged out, there is no need to update the page frame on the secondary storage device.

#### • File system

A file system is an abstraction that is provided to manipulate data in storage devices. It provides a way of organizing data, usually in a hierarchy of directories or folders arranged in a directory tree. Each group of data is called a file, and follows a given structure and logic rules so data can be recognized and organized. Often, file systems are complemented with a Virtual File System (VFS), that allows applications to access concrete file systems in a uniform way.

#### • Device Drivers

Device drivers are software entities that contain implementation of software that is related to the specificness of the underlying hardware. System calls are usually provided, so applications can invoke device drivers to interact with devices, releasing the user applications from specific hardware implementation responsibilities. Some kernel architectures, usually monolithic kernel ones, implement device drivers in kernel space to prevent user applications from crashing the whole system with ease.

## 2.2.3 Real-time Operating Systems

Although OS have greatly improved computing systems as a whole, not everything is an upside about them. In fact, in the embedded systems field, namely real-time systems, common OS overhead and uncertainty is not acceptable. A general purpose OS has lots of overhead sources, from boundary crossing memory copies to task switching. Boundary crossing memory copies occur when user space and kernel space transfer data, usually in device drivers. Frequent buffer copies are a heavy toll on the system, providing a great deal of unnecessary overhead for some embedded systems. Also, task switching introduces latency, as one task's context must be saved, and another restored.

Finally, most general purpose scheduling algorithms are not greatly suited for realtime scenarios as task's deadlines are not taken into account, and uncertainty on when a context switch is going to occur, and thus when a task gets processor time and executes is a dooming factor.

For all of the above reasons, real-time embedded systems often deploy Real-Time Operating Systems (RTOS). Real-Time Operating System (RTOS) are operating systems that are specifically designed for real-time application purposes, implemented to schedule real-time tasks with deadlines, usually under a system of priorities, with high priority tasks guaranteed to run under a certain amount of time. Often RTOS do not implement many common general purpose OS services, with common microkernel architectures, for instance implementing device drivers in user-space to avoid boundary crossing overhead. Examples of real time operating systems include FreeRTOS, MontaVista Linux and RTEMS.

## 2.2.4 Linux

Linux is an open-source OS, initially developed by Linus Torvalds as a hobby. Its kernel, which is monolithic, was first released on the 5th of October, 1991. Since its first inception, Linux has evolved rapidly, being widely adapted to most modern systems and becoming one of the most successful OS, on par with famous commercial OS such as Windows and MacOS.

The Linux kernel is licensed under General Public License (GPL) which is a license that grants free access to the original software code, as well as the possibility to change it and redistribute at will. Several OS make use of the Linux kernel, being

referred to as Linux distributions. Although there are not that many desktop Linux users compared to other popular OSs, it is the preferred OS of choice in supercomputers, servers and most embedded devices, such as MP3 players, DVD players and HD TVs.

Although Linux was initially developed for Intel x86 compatible machines, no other OS has been more ported to other architectures (Silva, 2011). With a large selection of device drivers for several common hardware devices, it is obviously a hugely popular platform for embedded development, as rapid deployment of an OS with wide hardware support for a multitude of architectures and devices reduces time-to-market significantly. Some of the following characteristics may explain Linux's popularity, namely in the embedded system field:

- Available on a big selection of architectures;

- Supports a large selection of hardware devices;

- Product distribution free of royalties;