**Universidade do Minho** Escola de Engenharia

João Carlos Ferreira Alves

Ontology-Driven Metamodeling

Towards Hypervisor Design Automation:

Secure Inter-Partition

Communication (IPC)

**Universidade do Minho** Escola de Engenharia

João Carlos Ferreira Alves

Ontology-Driven Metamodeling

Towards Hypervisor Design Automation:

Secure Inter-Partition

Communication (IPC)

Dissertação de Mestrado em Engenharia Eletrónica Industrial e Computadores

Trabalho efetuado sob a orientação do Professor Doutor Adriano Tavares Professor Doutor Sandro Pinto

## Declaração do Autor

Nome: João Carlos Ferreira Alves

Correio Eletrónico: a68515@alunos.uminho.pt

Cartão de Cidadão: 14614957

Titulo da dissertação: Ontology-Driven Metamodeling towards Hypervisor De-

sign Automation: Secure Inter-Partition Communication

Ano de conclusão: 2018

Orientador: Professor Doutor Adriano Tavares

Designação do Mestrado: Ciclo de Estudos Integrados Conducentes ao Grau

de Mestre em Engenharia Eletrónica Industrial e Computadores

Área de Especialização: Sistemas Embebidos

Escola de Engenharia

Departamento de Eletrónica Industrial

De acordo com a legislação em vigor, não é permitida a reprodução de qualquer parte desta dissertação.

Universidade do Minho, 23/01/2018

Assinatura: João Carlos Ferreira Alves

## Acknowledgements

Firstly, I would to thank my advisor Dr. Adriano Tavares, for proposing me a project for my thesis and for enlightening me throughout its development, with his vast knowledge and expertise. Following, I would to thank Dr. Sandro Pinto that also having made its contribution, by making me feel motivated when things looked more complicated, by providing me the opportunity to make one of my firsts scientific contribution, by being always available and by promoting companionship within the research group.

To the embedded systems class of 2015/16, a huge "Thank You!" for being a great group of work and for the great collaborative environment. Special note to the "German Gang" for being with me on my first experience abroad. Also, a special "Thank you!" To the irreverent Dr. Tiago Gomes, for helping me in achieving my first of all scientific contribution, and by being a great lab companion. To my friend and peer of 4th year projects, David Cerdeira, with whom I've shared moments of difficulty and despair, however always overcoming those things; for the long hours of work, conversation and knowledge sharing, one massive "Thank You!". Last, but certainly not the least, I would to massively thank my companion José Martins, for sharing with me long hours of work throughout the development of this dissertation, helping to overcome adversities that appeared, helping me feel motivated and for always pushing me further.

I kindly thank my friends and family, for the patience and support, for the time of companionship and relaxation, and for never ever giving up on me. I can not name all of them, as would I need a lot more pages. However, there are a few to whom I should leave the most dearest "Obrigado!", for having such a special place in my heart. This goes to:  $Tin\hat{o}cos$  (Rita, Isa, Moreira, Teresa, Helena e Bruno), Nuno, Octávio and Chuck.

Finally, the biggest "Obrigado!" goes to my parents and little brother, for providing all that I needed, for being the highest reference of hard-work, for dealing with me on the hardest moments, and for never letting me down. My biggest goal is to make you feel proud! So for all this, and for what is yet to come "Obrigado, gosto muito de vocês!!".

#### Abstract

Embedded systems, which were by definition single-purpose, have evolved rapidly and nowadays are capable of supporting applications that, priorly, would be distributed between different hardware platforms. Virtualization proved its value in other fields, providing a way to safely collocate different applications on the same platform, enforcing security through isolation. Typical virtualization solutions follow a monolithic architecture, which usually contain large Trust Computing Base (TCB). Inherently, these are difficult to maintain, and could likely hide buggy software. Microkernels advocate a minimal TCB, that is restricted to an Inter-Partition Communication (IPC) infrastructure, a scheduler and memory management. Other functionalities are implemented in user-space, isolated from the system's critical functionalities. Service provision is achieved by leveraging Inter-Partition Communication (IPC) infrastructure, with well defined communication channels, and establishing trustworthy communication relations.

The inherent complexity of properly configuring such systems requires the use of dedicated tools, aiming at easing the configuration process. Model-Driven Engineering (MDE) advocates the conception of models towards software development, which would provide a more abstract, simplified view of the final system. Model description is often paired with Domain-Specific Languages (DSLs), that are featured with generative capacities. Thus, it becomes possible to transform a more abstract system into implementation artifacts (e.g. C/C++ code). Semantic technology has also been combined to modeling technologies, providing an alternative system representation, while enhancing modeling tools with: higher consistency, interoperability, automated validation and reasoning support.

Under the light of the above, a collaborative effort was conducted towards the enhancement of the in-house developed RTZVisor with microkernel-like principles, that resulted on the  $\mu$ RTZVisor. This thesis focus on the implementation of a secure IPC infrastructure, featured with a capability-based access-control facility, to improve its overall reliability by imposing Information Control Flow (ICF). Aiming at easing system's configuration, a modeling infrastructure was conceived that enabled the description of systems to be deployed on top of  $\mu$ RTZVisor. The infrastructure also converts the model representation into final source code with  $\mu$ RTZVisor resources configuration.

#### Resumo

Os Sistemas embebidos, que eram por definição de propósito único, têm evoluído rapidamente, sendo hoje em dia são capazes de suportar aplicações que, anteriormente, estariam distribuídas por diferentes plataformas. A virtualização provou o seu valor em diferentes áreas, possibilitando a consolidação segura de diferentes aplicações numa só plataforma, impondo segurança por isolamento. Tipicamente, a virtualização é implementada numa arquitetura monolítica, que requer muitas linhas de código. Consequentemente, estas são difíceis de manter e de validar, e podem conter erros "escondidos". As arquiteturas *Microkernel* advogam o principio da minimalidade, com o objetivo de minimizar o tamanho da sua implementação. Tipicamente, estas restringem-se a serviços de comunicação entre partições, escalonamento e isolamento espacial. Outras funcionalidades devem ser implementadas como aplicações, isolando-as assim, dos serviços críticos do sistema. Devem-se, por isso, estabelecer canais de comunicação seguros para se providenciarem serviços entre partições.

A configuração de tais sistemas pode ser complexa e morosa. Assim, requer-se a utilização de ferramentas dedicadas à automação deste mesmo processo.  $Model-Driven\ Engineering\ (MDE)$  coloca a conceção de modelos como objetivo primário do desenvolvimento de software. Este paradigma é usalmente combinado com linguagens de domínio específico, que possuem capacidades generativas, tornando-se possível converter a representação de um modelo em artefactos de implementação (nomeadamente código C/C++). A tecnologia semântica tem sido utilizada para conceção de modelos, melhorando as ferramentas de modelação com: verificação de consistência do modelo, interoperabilidade e validação automatizada.

No seguimento do que foi dito anteriormente, foi efetuado o melhoramento da implementação do hipervisor RTZVisor, conferindo-lhe príncipios de arquiteturas Microkernel, concevendo-se o  $\mu RTZVisor$ . Esta tese focou-se na implementação de mecanismos seguros para comunicação entre partições, complementados com funcionalidades para controlo de acessos. De forma a facilitar o processo de configuração, foi desenvolvida uma ferramenta de modelação, que converte a representação de um modelo em código fonte para configuração do  $\mu RTZVisor$ .

## Contents

| $\mathbf{A}$     | bstra | $\operatorname{ct}$ |                                                                                                                                    |   | ix   |

|------------------|-------|---------------------|------------------------------------------------------------------------------------------------------------------------------------|---|------|

| $\mathbf{R}$     | esum  | 10                  |                                                                                                                                    |   | xi   |

| $\mathbf{C}_{0}$ | onter | nts                 |                                                                                                                                    |   | xiii |

| Li               | st of | Figure              | es ·                                                                                                                               | 3 | xvii |

| Li               | st of | Tables              |                                                                                                                                    |   | xix  |

| $\mathbf{G}$     | lossa | ry                  |                                                                                                                                    | x | xiii |

| Li               | sting | çs.                 |                                                                                                                                    | X | xvi  |

| 1                | Intr  | oductio             | on                                                                                                                                 |   | 1    |

|                  | 1.1   | Contex              | st                                                                                                                                 |   | 4    |

|                  | 1.2   | Goals .             |                                                                                                                                    |   | 5    |

|                  | 1.3   | Docum               | nent's Structure                                                                                                                   |   | 6    |

| 2                | The   | eoretica            | d Foundation and Background                                                                                                        |   | 7    |

|                  | 2.1   | Virtual             | lization                                                                                                                           |   | 7    |

|                  | 2.2   | Microk              | ternels vs Monolitic                                                                                                               |   | 9    |

|                  | 2.3   | Inter-P             | Partition Communication                                                                                                            |   | 11   |

|                  |       | 2.3.1               | Policies and Mechanisms                                                                                                            |   | 12   |

|                  |       | 2.3.2               | Review Of IPC security                                                                                                             |   | 15   |

|                  | 2.4   | Access-             | -Control                                                                                                                           |   | 16   |

|                  |       | 2.4.1               | Capability-based Access-Control                                                                                                    |   | 17   |

|                  | 2.5   | Microk              | ternels Related Work                                                                                                               |   | 18   |

|                  | 2.6   | ARM                 | $\Gamma ustzone \dots \dots$ |   | 20   |

|                  | 2.7   | RTZVi               | sor                                                                                                                                |   | 22   |

|                  |       | 2.7.1               | Identified Limitations                                                                                                             |   | 24   |

|                  | 2.8   | Model-              | Driven Engineering                                                                                                                 |   | 25   |

|                  |       | 2.8.1               | Domain-Specific Language                                                                                                           |   | 26   |

|                  |       | 2.8.2               | Component-based Software Engineering                                                                                               |   | 28   |

|   |                             |                       | 2.8.2.1 Component-based Modeling Solutions | 29 |

|---|-----------------------------|-----------------------|--------------------------------------------|----|

|   | 2.9                         | Ontolo                | ogy-Driven Software Development            | 31 |

|   |                             | 2.9.1                 | Example of an Ontology                     | 33 |

|   | 2.10                        | $\operatorname{SeML}$ | Infrastructure                             | 34 |

|   |                             | 2.10.1                | Upper Ontology                             | 36 |

|   |                             | 2.10.2                | Simple Example                             | 37 |

| 3 | $\mu \mathbf{R} \mathbf{I}$ | ZViso                 | r Architecture                             | 39 |

|   | 3.1                         | System                | n Overview                                 | 39 |

|   |                             | 3.1.1                 | Partition Manager                          | 44 |

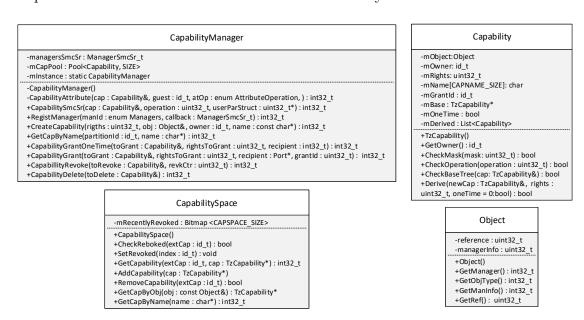

|   |                             | 3.1.2                 | Capability Manager                         | 45 |

|   |                             | 3.1.3                 | Memory Manager                             | 47 |

|   |                             | 3.1.4                 | Device Manager                             | 49 |

|   |                             | 3.1.5                 | Interrupt Manager                          | 50 |

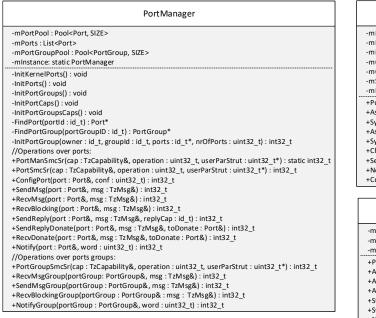

|   |                             | 3.1.6                 | Port Manager                               | 51 |

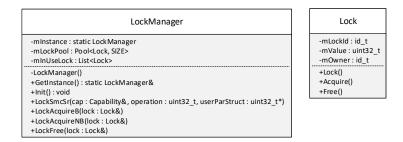

|   |                             | 3.1.7                 | Lock Manager                               | 54 |

|   |                             | 3.1.8                 | Event Manager                              | 55 |

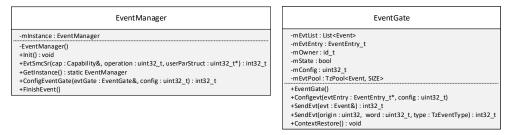

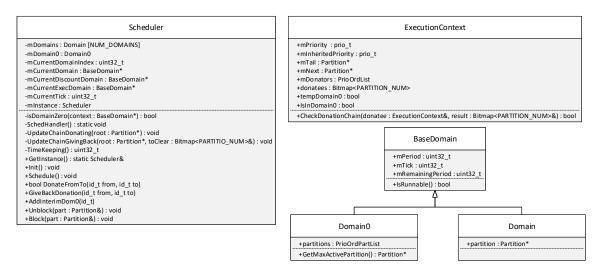

|   |                             | 3.1.9                 | Scheduler                                  | 55 |

|   | 3.2                         | Imple                 | mentation                                  | 59 |

|   |                             | 3.2.1                 | Access-Control                             | 61 |

|   |                             |                       | 3.2.1.1 SMC Handler                        | 62 |

|   |                             |                       | 3.2.1.2 Grant and Revoke                   | 63 |

|   |                             | 3.2.2                 | IPC                                        | 65 |

|   |                             |                       | 3.2.2.1 Message Passing                    | 65 |

|   |                             |                       | 3.2.2.2 Synchronization                    | 69 |

|   |                             | 3.2.3                 | Events                                     | 70 |

|   |                             | 3.2.4                 | Scheduler                                  | 72 |

|   |                             | 3.2.5                 | Code Verification                          | 76 |

|   | 3.3                         | Evalua                | ation                                      | 77 |

|   |                             | 3.3.1                 | IPC performance                            | 77 |

|   |                             | 3.3.2                 | Security Analysis                          | 80 |

| 4 | Нур                         | erviso                | or's Design Automation                     | 83 |

|   | 4.1                         | Metho                 | dology and Context                         | 83 |

|   | 4.2                         |                       | escription Language                        | 84 |

|   |                             | 4.2.1                 | Domain Ontology                            | 87 |

|   |                             | 4.2.2                 | Grammar                                    | 91 |

|   |                             | 123                   | Code Ceneration                            | 03 |

|    |       | 4.2.3.1 TZDL's code generation | 94  |

|----|-------|--------------------------------|-----|

|    |       | 4.2.3.2 TZDL Tool              | 96  |

|    | 4.3   | Simple Use-Case                | 97  |

|    |       | 4.3.1 TZDL Program             | 98  |

|    |       | 4.3.2 Code Generation          | 101 |

|    | 4.4   | Discussion                     | 103 |

| 5  | Con   | nclusion                       | 107 |

|    | 5.1   | Future Work                    | 109 |

| Bi | bliog | graphy                         | 120 |

# List of Figures

| 2.1  | Common example of Security achieved by isolation [1]                               | 7  |

|------|------------------------------------------------------------------------------------|----|

| 2.2  | Type of hypervisors architectures                                                  | Ĝ  |

| 2.3  | Monolitic vs Microkernel architectures                                             | 10 |

| 2.4  | Representation of the asymmetric trust model                                       | 13 |

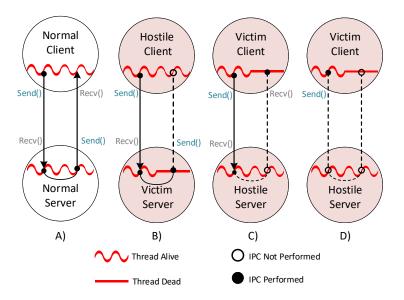

| 2.5  | Representation of the asymmetric trust model                                       | 14 |

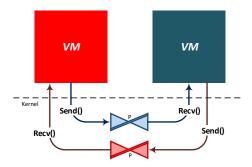

| 2.6  | Representation of the asymmetric trust model                                       | 17 |

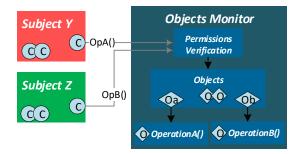

| 2.7  | RTZVisor system architecture                                                       | 21 |

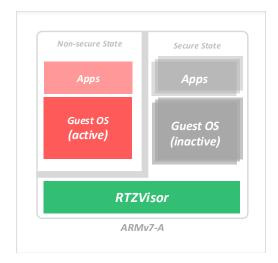

| 2.8  | RTZVisor system architecture                                                       | 23 |

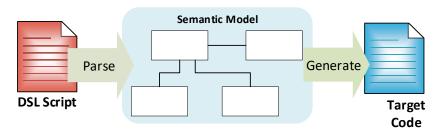

| 2.9  | Overall DSL workflow [2]                                                           | 27 |

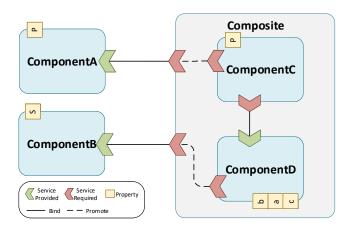

| 2.10 | Dummy example of a component-based architecture                                    | 28 |

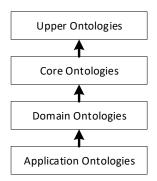

| 2.11 | A simplified ontologies classification scheme [3]                                  | 32 |

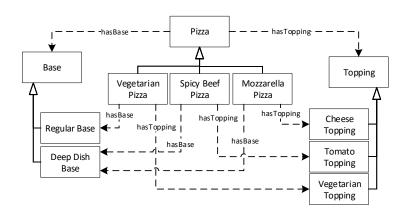

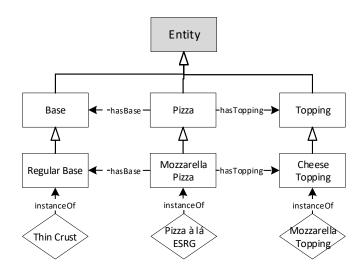

| 2.12 | Simple example with a Pizza ontology                                               | 33 |

| 2.13 | Individuals from Pizza ontology                                                    | 34 |

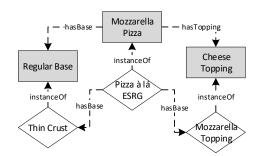

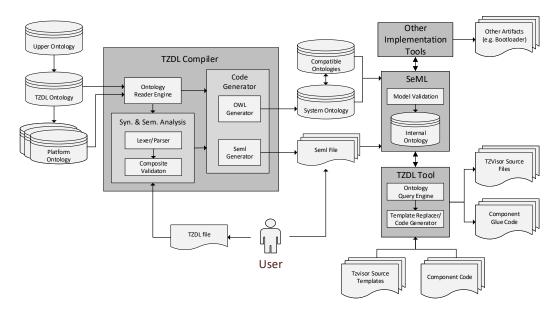

| 2.14 | SeML infrastructure overall architecture                                           | 35 |

| 2.15 | SeML upper Ontology                                                                | 36 |

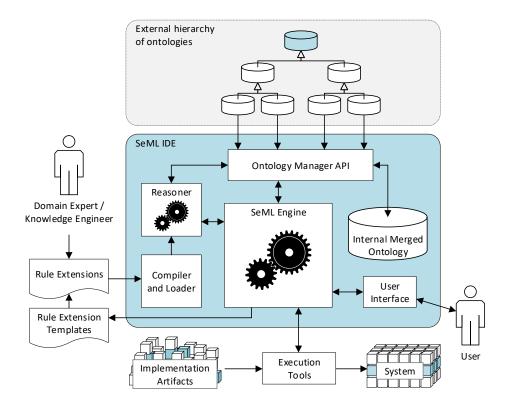

| 2.16 | Using SeML with pizza ontology                                                     | 37 |

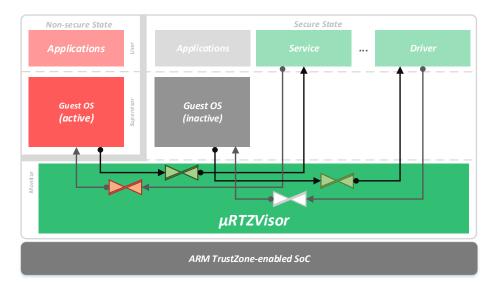

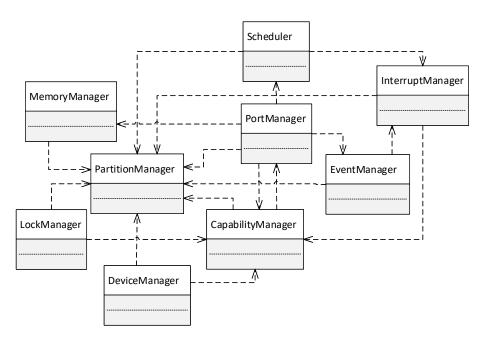

| 3.1  | $\mu$ RTZVisor architectural overview                                              | 40 |

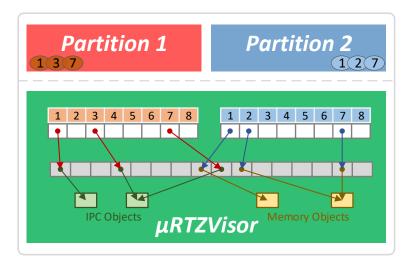

| 3.2  | Capability-based access control system overview                                    | 46 |

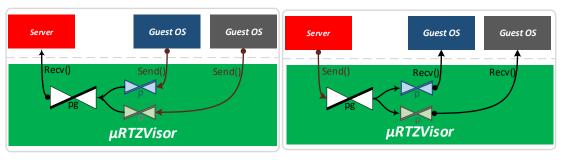

| 3.3  | Operations using a <i>port group</i> as endpoint                                   | 54 |

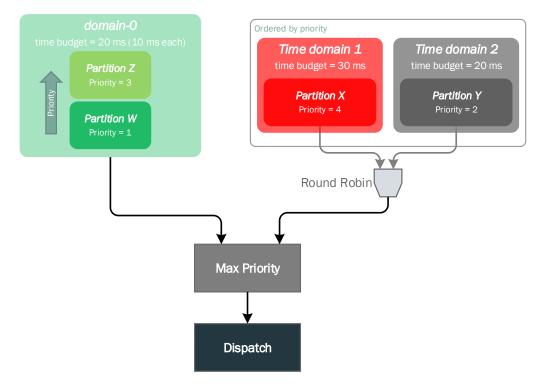

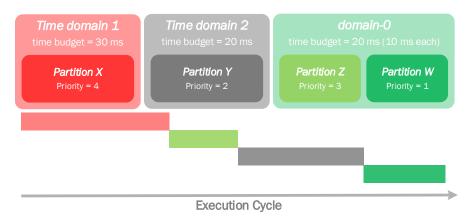

| 3.4  | Overview of the scheduling algorithm                                               | 56 |

| 3.5  | Example of an execution cycle, given a set of time domains with                    |    |

|      | their own partitions and respective configuration                                  | 57 |

| 3.6  | $\mu \mathrm{RTZV}\mathrm{isor}$ UML diagram: overview of implemented architecture | 59 |

| 3.7  | Classes that encapsulate access control functionality                              | 61 |

| 3.8  | Classes that encapsulate message-passing functionality                             | 65 |

| 3.9  | Classes that encapsulate synchronization functionality                             | 69 |

| 3.10 | Classes that encapsulate events functionality                                      | 71 |

| 3.11 | Classes that encapsulate scheduling functionality                                  | 72 |

| 4.1  | Overview of TZDL workflow                                                          | 85 |

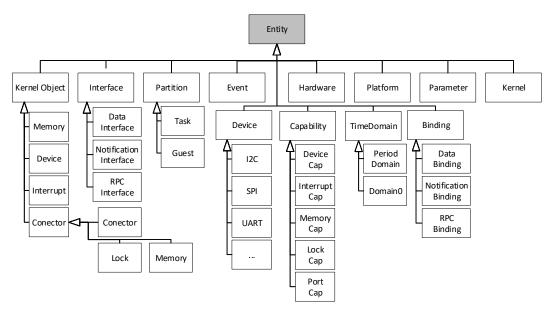

| 4.2  | Taxonomy for domain ontology, namely <i>Entity</i> derived classes                 | 88 |

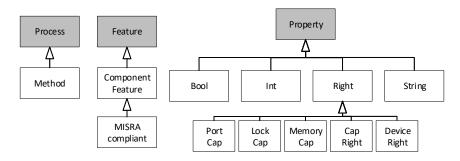

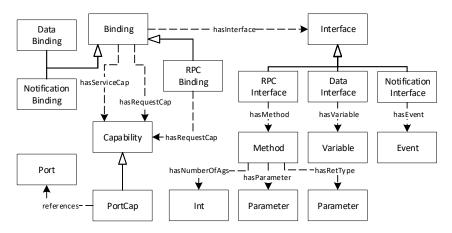

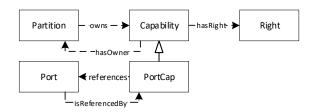

| 4.3 | Other taxonomies derived from other upper ontology's concepts                      | 89 |

|-----|------------------------------------------------------------------------------------|----|

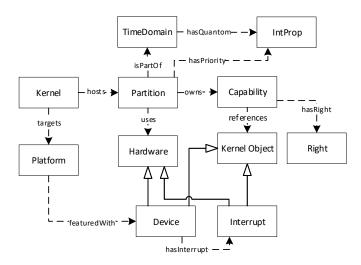

| 4.4 | Excerpt of kernel's domain ontology                                                | 89 |

| 4.5 | Excerpt of kernel's domain ontology, focusing on communication                     |    |

|     | related objects                                                                    | 90 |

| 4.6 | Excerpt of kernel's domain ontology, focusing on communication                     |    |

|     | related objects                                                                    | 97 |

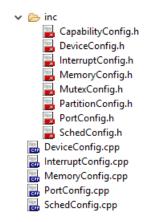

| 4.7 | Source code organization/hierarchy of all generated configuration                  |    |

|     | files                                                                              | 97 |

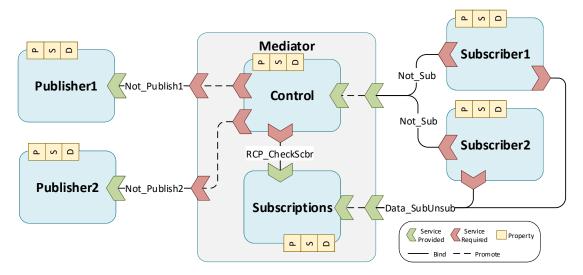

| 4.8 | Component-based architecture for a Publisher-Subscriber scenario. $\boldsymbol{.}$ | 98 |

|     |                                                                                    |    |

## List of Tables

| 3.1 | Port operations characterization, i.e., if it is synchronous or asyn- |    |

|-----|-----------------------------------------------------------------------|----|

|     | chronous and either blocking or non-blocking                          | 52 |

| 3.2 | Asynchronous IPC primitives latency $(\mu s)$                         | 77 |

| 3.3 | Synchronous IPC communication latency (us), in a guest-guest sce-     |    |

|     | nario                                                                 | 78 |

| 3.4 | Synchronous IPC communication latency (us), in a task-task scenario.  | 79 |

| 3.5 | Synchronous IPC communication latency (us), in a guest-task sce-      |    |

|     | nario                                                                 | 79 |

| 4.1 | Summary of all TZDL's constructs                                      | 92 |

| 4.2 | Generation summary for each type of <i>Interface</i>                  | 94 |

| 4.3 | Generation summary for each type of <i>Binding</i>                    | 95 |

# Listings

| 2.1  | Code for binding pizza properties                                   | 37  |

|------|---------------------------------------------------------------------|-----|

| 3.1  | Main function with initialization of all managers                   | 60  |

| 3.2  | Algorithm of the $smc\_handler$                                     | 63  |

| 3.3  | Algorithm of the <i>Grant</i> operation                             | 64  |

| 3.4  | Algorithm of the <i>revoke</i> operation                            | 64  |

| 3.5  | Algorithm of the recursive function from the $\it revoke$ operation | 65  |

| 3.6  | $\mu$ RTZVisor's message structure                                  | 66  |

| 3.7  | Algorithm of the <i>Send</i> operation                              | 67  |

| 3.8  | Algorithm of the recursive function from the $\it revoke$ operation | 68  |

| 3.9  | Algorithm of the recursive function from the $\it revoke$ operation | 69  |

| 3.10 | Algorithm of the $Lock$ operation                                   | 70  |

| 3.11 | Algorithm of the <i>Free</i> operation                              | 70  |

| 3.12 | $\mu$ RTZVisor's events and events entry structures                 | 72  |

| 3.13 | Algorithm of the donation procedure                                 | 74  |

| 3.14 | Algorithm for undoing a donation                                    | 75  |

| 3.15 | Algorithm for updating donations chain upon a new donation          | 75  |

| 3.16 | Algorithm for updating donations chain upon giving back a donation. | 75  |

| 4.1  | Ports and Capabilities' configuration structures                    | 96  |

| 4.2  | Elemental components code example in TZDL                           | 99  |

| 4.3  | Interfaces code example in TZDL                                     | 99  |

| 4.4  | Composite code example in TZDL                                      | .00 |

| 4.5  | Composite code example in TZDL                                      | .01 |

| 4.6  | Composite code example in TZDL                                      | .01 |

| 4.7  | Generated configuration files for the depicted example              | .02 |

## Glossary

$\mu$ RTZVisor micro Real-Time TrustZone-assisted Hypervisor.

**ABI** Application Binary Interface.

**ADL** Architectural Description Language.

**API** Application Programmable Interface.

**CBSE** Component-based Software Engineering.

**CC** Common-Criteria.

CPU Central Processing Unit.

**DAC** Descritionary Access Control.

**DMA** Direct Memory Access.

**DoS** Denial-Of-Service.

**DRAM** Dynamic Random-Access Memory.

**DSL** Domain-Specific Language.

**EAL** Evaluated Assurance Level.

FIQ Fast Interrupt Request.

**GIC** Generic Interrupt Controller.

**GPL** General-Purpose Language.

**GPOS** General-Purpose Operating Sytem.

**GUI** Graphical User Interface.

**ICF** Information Control Flow.

**IDL** Interface Description Language.

**IPC** Inter-Partition Communication.

IRQ Interrupt Request.

MAC Mandatory Access Control.

MDA Model-Driven Architecture.

**MDE** Model-Driven Engineering.

MDSD Model-Driven Software Development.

MILS Multiple Independent Levels of Security.

MMU Memory Management Unit.

**OCM** On-Chip Memory.

**ODSD** Ontology-Driven Software Development.

**OMG** Object Management Group.

**OS** operating system.

**OS** Operating Sytem.

**OWL** The Web Ontology Language.

**PCB** Partition Control Block.

**PP** Protection Profile.

**ROM** Read-Only Memory.

**RPC** Remote Procedure Calls.

RTOS Real-Time Operating Sytem.

**RTTI** Run-Time Type Information.

RTZVisor Real-Time TrustZone-assisted Hypervisor.

**SeML** Semantically-enriched Modeling Language.

SoC System on Chip.

**SRAM** Static Random-Access Memory.

**TCB** Trust Computing Base.

**TLB** Translation Lookaside Buffer.

**TOE** Target Of Evaluation.

TZASC TrustZone Address Space Controller.

**TZDL** TrustZone Description Language.

TZMA TrustZone Memory Adapter.

TZPC TrustZone Protection Controller.

UML Unified Modeling Language.

VM Virtual Machine.

VMCB Virtual Machine Control Block.

VMM Virtual Machine Monitor.

W3C World Wide Web Consortium.

## Chapter 1

#### Introduction

Embedded systems are widespread in modern society, due to their presence at the technological base for different systems in a broad range of application areas, including automotive, robotics, aerospace, IoT, and so on. Moreover, the whopping evolution of silicon technologies is pushing embedded systems further, making them suitable to integrate complex and powerful modern systems.

Nowadays, embedded devices are becoming increasingly complex, ranging from strict real-time control applications, to rich GUIs on a single embedded computer. Priorly, complex systems could encompass multiple embedded control units, which can now be supported within one single embedded computer [4]. This performance increase is favorable to systems cost reduction, by lowering the amount of hardware required, however, this incurs into an increased software complexity. The evolution of cellphones towards smartphones is another great example of the embedded systems evolution, as they used to be devices with extremely limited resources, supporting only a few set of functionalities, but nowadays, such devices are extremely powerful and can support several tasks on a multitude of scenarios and applications. A device that was provided with a single processor and limited in terms of storage capacity, whose purpose was mainly to make audio calls and send text messages, evolved into a mobile platform that completely surpassed its predecessor. It now includes, on a single device, a set of functionalties that formerly were separately available, such as audio player, high definition cameras, displays, internet, localization capabilities, along with a generous storage capacity [5, 1].

However, consolidating a multitude of systems in one single platform raises several security and safety concerns [1]. Virtualization urged key-enabling technology for addressing this problematic, since it enables the collocation of different Operating Sytem (OS), while ensuring that they run separately, confined to their physical space. This is achieved by providing an abstraction layer to those OSes, that manages hardware resources [6]. This helps to enforce the system's security, as an existent vulnerability in one OS does not affect the others. This approach

has been widely used in servers, as a way to not only provide security but also to achieve energy efficiency [5, 7].

The software that provides the desired abstraction and manages the isolation complexity is called a Virtual Machine Monitor (VMM), or Hypervisor. Monolithic hypervisors are usually software blocks whose implementations encompass a large Trust Computing Base (TCB), which often leads to hidden software bugs that may jeopardize system's functioning, and that are usually hard to maintain [8]. Microkernel architectural approach appeared as a solution to mitigate monolithic implementation problems. Their design aimed at reducing the complexity of kernel infrastructures by providing the bare minimum required functionalities to support process concurrency [9, 4], complying with the principle of minimality [10]. Microkernel implementations solely encompass a scheduler, memory management and Inter-Partition Communication (IPC). Moreover, the provided system calls should not impose any kind of policy. Also, according to the principle of minimality, the remaining functionalities must be implemented in user space, with well established IPC interfaces for service provisioning. This kind of implementation drastically reduces the kernel's size, and reduces the probability to have buggy software in the system's root of trust [8, 11]. Although these principles sound appealing, microkernel performance is poor compared to monolithic approaches due to high dependence on IPC infrastructure. This mindset was broken by Liedtke [12, 13] when he introduced a high-performance IPC in a microkernel implementation. Nowadays, microkernels are being widely used, and a few of them are even aiming virtualiation [14, 15].

In microkernel-based systems, servers and applications are usually of mixed criticality [16], and among them may be executing untrustworthy partitions. As a result, IPC interactions may occur between critical servers and untrusted parties. In these scenarios, the security provided by isolation is not enough. Communication relations are a concern, given that the IPC infrastructure constitute a means for attacking sibling partitions [17, 16]. One major concern whenever implementing IPC mechanisms is how to mitigate the chance of a Denial-Of-Service (DoS) attack [18]. Also, if a component is entrusted with confidential data, leakage of this data to the outside world should not be a possibility. Thus, isolation must be complemented with confinement, usually achieved by providing access-control facilities, in which access to system resources and interfaces must be explicitly granted instead of being available by default [19, 20]. This is often referred to as Information Control Flow (ICF).

One drawback of microkernel-based systems is that they required a high-level of

functionality segregation, which often pairs with a high-level of systems configuration, namely for establishing communication relations and resource multiplexing. In addition, most of such embedded systems are also characterized as real-time systems, which means that the real-time properties, such as response time, time quantum, among others, are also important design concerns. This increased complexity of embedded real-time systems leads to increasing demands with respect to requirements [21]. The use of model representation raises the level of abstraction on systems architecture, enables seeing the system at lower granularity, which is often useful for design validation and requirements verification [22]. Componentbased architectures promote model representation by splitting the system into functional units, dubbed components, that interact through well defined interfaces. This kind of system design pairs well with functional segregation and IPC reliance inherent to microkernel-based systems. Also, it provides great control over granularity of representation, by advocating a componentised representations [9]. Pairing these concepts with a Domain-Specific Language (DSL) featuring code generation, not only enables design validation, but also incurs into higher productivity, reliability, portability, and eases software testing [2].

Microkernel implementations provide a greater fit for certification, toward security critical systems, due to its compact implementation [23, 9]. This could be achieved following the Common-Criteria (CC) standard and the Multiple Independent Levels of Security (MILS) architecture. The CC [24, 25, 26] is an international standard that targets computer security. It advocates the specification of a set of requirements that must be fulfilled within a class of products, constituting a Protection Profile (PP). In a PP assurance, requirements are tagged with a representative security level, dubbed Evaluated Assurance Level (EAL). The use of formal methods, mathematical models and proofs at the design stage is usually required for high security levels. Lower levels simply impose functional or structural testing in addition to methodical development processes. The MILS [27, 28, 26] architecture defines a conceptual framework towards system security, by using a divide-and-conquer approach. This is achieved using separation, composition, and layered assurance and it is implemented using four layers, namely: trusted hardware, separation kernel, middleware, and applications. This reduces the amount of code to be verified and, consequently, increases its scrutiny. According to the layered assurance principle, the security level increases when going down the stack [27], e.g. the applications can not be more secure than the separation kernel. The separation kernel is built on fundamental security policy:

- *Information Flow* Regards to the permitted communication channels between partitions;

- **Data Isolation** This ensures that a partition cannot access resources in other partitions;

- *Temporal Isolation* This ensures that applications within partitions are executed for the specified duration in the system schedule;

- *Fault Isolation* This postulates that failure is confined within a partition's domain;

- Sanitization To ensure the information flow requirement, the separation kernel should clean any shared resources (microprocessor registers, system buffers, etc.) before being used by another partition.

The exposed principles can constitute a PP based on MILS architecture, that could be applied in the implementation of an embedded hypervisor. Thus, contributing to the certification of, or at least part of, the Target Of Evaluation (TOE).

#### 1.1 Context

This thesis was conceived within a collaborative effort from students working at Embedded Systems Research Group, the University of Minho. The ultimate goal of the group's work is to provide an embedded secure hypervisor, with great focus on security, integrated with a design automation tool that allows the faster development and configuration on the previous platform, while following a secure software development approach. As such, some of the working members focus on developing a meta-modeling infrastructure, while others will focus on developing and modeling hypervisor artifacts. As the development of a embedded hypervisor from scratch is an extensive task, the developed work will have on its roots the in-house developed Real-Time TrustZone-assisted Hypervisor (RTZVisor), that constitutes a monolithic implementation aimed at real-time applications. As such, concurrently to this thesis, there will be elements focusing on the enhancement of the aforementioned architecture with microkernel-like principles, with great focus on device sharing, spacial and temporal isolation. Other dissertations will be focused on achieving a secure boot process, data and control flow integrity, an ontology-driven DSL, dubbed Semantically-enriched Modeling Language (SeML).

This thesis focus on enhancing the hypervisor kernel with a secure IPC infrastructure, as well as the modeling of developed artifacts. The IPC infrastructure should conceived aiming at security, and should be complemented with access-control to provide a way of achieving ICF.

#### 1.2 Goals

This thesis focus on the enhancement of RTZVisor with microkernel-like principles, in addition to providing a means for easily configure the developed artifacts. RTZVisor is a monolithic hypervisor, implemented using the C language, that leverages ARM TrustZone technology towards virtualization, providing a close to full-virtualized environment. However, as it is going to be discussed in further sections, this comes with a set of limitations, namely the absence of IPC and synchronization mechanisms, as well as the absence of a dedicated modeling infrastructure towards system configuration.

Given this, the following set of goals were specified:

- 1. Perform a comprehensive survey on IPC and access-control facilities within microkernels context, identifying common vulnerabilities;

- 2. Implement an IPC infrastructure, with both communication and synchronization mechanisms. This should be achieved by following state-of-the-art principles with respect to microkernels, placing special focus on security;

- 3. Implement a lightweight access-control facility, that enhances IPC mechanisms with ICF;

- 4. Adopt a secure development process by recurring to C++ instead of C, performing code certification recurring to the MISRA C++ standard, that advocates a set of principles and rules towards a more secure development;

- 5. Conceive a meta-model towards hypervisors design automation, placing special focus on IPC resources and communication channels;

- 6. Evaluate the hypervisor's implemented artifacts, namely in terms of performance and security;

- 7. Evaluate the conceived work regarding the design automation tool, namely identifying the gains of the used approach, as well as the counter-parts.

#### 1.3 Document's Structure

This document is structured as follows:

- Chapter 2 provides the knowledge framework for understanding the developed work. It defines virtualization fundamental concepts, followed by making the comparison between two different kernel architectures. Then, it provides a review on IPC comprising elemental concepts, policies, elemental mechanisms and security. Access-control general concepts are introduced, to then support the description of capability-based access-control facilities. Some microkernel implementations are described, emphasizing on implemented Inter-Partition Communication (IPC) policies and access-control approaches. The Arm TrustZone architecture is described to support the architectural description of RTZVisor, which is the root for the developed hypervisor artifacts. Model-Driven engineering is introduced, emphasizing DSL, component-based approaches and ontologies. Lastly, SeML infrastructure is described.

- Chapter 3 describes the μRTZVisor architecture. It starts by presenting an overview of the implemented work, starting by stating the advocated principles and architectural goals, as well as a general functional description. Then, each subsystem within the kernel is described, following an order that enables to understand how each subsystem role, and which dependencies are established with the remaining. It is then followed by a structural and behavioral description of the developed work; however, confining to communication mechanisms, access-control facilities and other correlated contributions.

- Chapter 4 describes our approach towards the hypervisor's design automation. It starts by describing the goals for the design automation, specifying SeML's role in all this. Then, a DSL towards microkernel-like systems is presented. It is described the developed ontology for integration with SeML infrastructure, language constructs, and code generation process. An example is then provided, and a discussion is conducted to evaluate the developed work and achieved results.

- Chapter 5 concludes this thesis. It presents the conclusions obtained from this research, highlighting the contributions, identifying the limitations, and suggesting future work towards addressing pointed limitations.

## Chapter 2

# Theoretical Foundation and Background

This chapter aims at providing the necessary background to understand and contextualize the developed work. Virtualization is defined, followed by a comparison between microkernels and monolithic architectures. Next, it is presented a concise survey on IPC, approaching security, as well as applied policies and mechanisms. It is followed by the definition of access-control, and then presenting capabilities as the *de facto* standard for access-control in microkernel-like architectures. Then, it is introduced the key-enabling technology towards RTZVisor implementation, followed by the latter's architectural description. Model-driven engineering concepts are also presented, placing emphasis on ontologies and component-based architectures. Lastly, the SeML infrastructure is described.

#### 2.1 Virtualization

Virtualization enables the cooping of multiple OSes, in this context also called Virtual Machine (VM)s, by providing an environment that abstract the underlying hardware platform and enables the safe sharing of available resources. This abstraction is provided by introducing another software layer, often called Virtual Machine Monitor (VMM) or hypervisor [4, 29, 30, 5]. Its main applicability is to

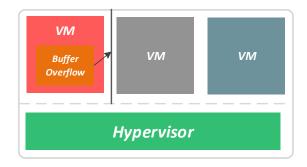

Figure 2.1: Common example of Security achieved by isolation [1].

improve system's safety and security, by providing environment isolation, which is expected to prevent that a given vulnerability or buggy behavior does not jeopardize sibling VMs [26]. Figure 2.1 is a common example of the security provided by isolation, in which a buffer overflow attack happens in a given VM. This is also a necessary requirement for other incurring benefits, like application consolidation, which helps in reducing production costs by lowering the amount of required hardware to support all the desired functionality, and to reduce energy consumption by load-balancing across clusters, creating VMs on slightly utilized hosts [29, 1, 31]. Other uses for applying virtualization techniques are: to enable hardware compatibility with legacy software applications; to increase software portability making it hardware-independent; and to provide an environment that support different OSes [32, 4]. A typical example of a very-well known virtualized system is the cell-phone, that usually requires a Real-Time Operating Sytem (RTOS) to interact with the cell-phone's sensors and to perform important real-time tasks, in addition to a General-Purpose Operating Sytem (GPOS) that supports the Graphical User Interface (GUI), functionality towards network connectivity, and so on. Virtualization in this context prevents, for example, a remote attack on the GPOS to have repercussions on the RTOS.

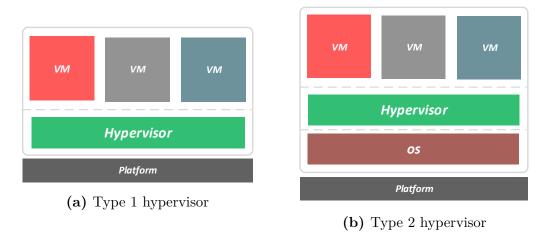

There are two types of hypervisors: type 1 (Figure 2.2a) that execute directly above the hardware, being the only software executing in kernel mode; type 2 (Figure 2.2b) hypervisors run on top of an OS [29, 5, 30, 31]. In both cases, VMs must behave exactly in the same matter within the virtualized system as they would, by executing directly over the hardware platform. In addition, for tightly coupled systems the IPC infrastructure must behave efficiently, i.e. with good performance and considerable throughput [5, 6, 31]. Typical embedded virtualization solutions belong to type 1 category, as type 2 would not be a good fit for embedded systems. This is due to the overhead inherent to the existence of an OS between the hypervisor and the hardware platform [30].

Regardless of their type, there are two different approaches towards a virtualization solution. Full-virtualization solutions are characterized for providing an environment that allows legacy VMs to execute without modifications, which is achieved by trapping sensitive instructions of the guest OS and emulating them on the actual hardware platform. In contrast, para-virtualization requires specific changes at the OS level in order to make VMs suitable to run over a given hypervisor, replacing specific instructions with system calls to the hypervisor. In one hand, full-virtualization require little engineering effort for VM's deployment in a given virtualized system and does not require code availability. Para-virtualized

Figure 2.2: Type of hypervisors architectures.

solutions usually incur into better performance, as the performed changes may also aim at removing unnecessary operations. However an obvious obstacle is the OS code availability, necessary to perform the aforementioned changes [33, 5].

Although virtualization is a way to achieve many benefits, these come at expected costs. Typical virtualization solutions can be modified in order to make them usable in embedded platforms, although they lack on fulfilling restrictions and requirements specific of embedded systems, such as memory footprint or real-time scheduling guarantees [6, 4, 29]. For critical systems the amount of code constituting the Trust Computing Base (TCB) is relevant, as the number of buggy behavior is directly proportional with the number of code lines. Thus, in addition to being carefully written, these must be reduced to the strictly necessary, favoring system's safety and also for matching embedded systems' memory requirements [6, 30]. Regarding scheduling capabilities, real-time systems are often required to quickly operate upon events, as well as to provide a meaningful time quantum for hard-real-time systems to complete their work under established deadlines [4, 15].

#### 2.2 Microkernels vs Monolitic

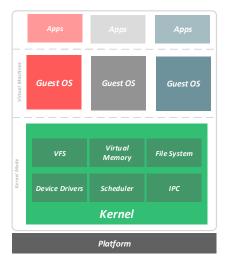

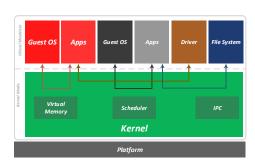

The kernel part of any OS is the software part that runs with the highest privilege, executing with no access restrictions over the hardware resources, in addition to being part of its TCB. TCB is defined by a set of assertions that the complete system is built upon, which is intended to be secure and reliable. Penetrating this systems' layer corroborates all asserted security and safety that characterizes the system [18]. In monolitic (Figure 2.3a) architectures, it is where

most OS functionalities are implemented, including interrupt handling, to memory management, device drivers, network stacks, IPC facilities and file systems. [9, 10]. The functionality consolidation, hardware architecture heterogeneity and support for different contexts (i.e. RTOS-based applications and GPOSes) contribute to increased software complexity and, consequently, considerable growth of kernel code size. Considerably large code implementations are usually difficult to maintain, escalate and are often prone to hide bugs which, given the amount of code, are hard to detect [9, 23, 34, 35]. It has been proved that, for the aforementioned reasons, smaller TCBs are preferable for the development of criticality computer systems [8, 36]. Microkernels (Figure 2.3b) constitute a paradigm shift

(b) Microkernel architecture

(a) Monolitic kernel architecture

Figure 2.3: Monolitic vs Microkernel architectures

from monolitic architectures, which basically consist in moving kernel services to userspace. The only acceptable services to provide within the kernel are those of memory management, IPC, and scheduler, thus promoting a minimalistic implementation that aims at considerably reducing TCB's code size [15, 14]. In addition, primitives implemented within the microkernel must comply with the principle of minimality [14, 10]. This advocates that system calls must be characterized with policy absence, i.e., as simple as possible. However, these must comprise a vast and rich number of services that make the implementation of meaningful systems feasible [1]. In order to keep the kernel simple, device drivers and other services (that regard with some type of service) are confined to a userspace server. Device drivers are usually the least trusted code within a kernel, and are usually prone to suffer remote attacks. The isolation in userspace limits the attack surface and prevents them to access system's critical information [8, 23].

The main handicap of microkernel approach is the obligatory reliance on IPC infrastructure, which, for a long time, was the main reason for microkernels to not be accepted as a valid solution [37]. By moving services within the kernel to a userspace server, the way to access them is through Remote Procedure Calls (RPC) interfaces or by client-server communication (more detail about this given in Section 2.3). As such, IPC has to be of great performance, which was achieved by Liedtke et al. [13, 12] by implementing L4 microkernel whose design primarily goal was to provide fast IPC, proving that microkernels are a valid solution for modern computing systems. However, IPC is not only used for client-server communication: Hardware-generated interrupts or traps caused by user level processes can be converted into IPC messages by the microkernel and are sent to a responsible handler (a user level process) [4].

Security is also achieved by providing an environment that fosters functionality segregation, which results in higher level of fault containment, as a given vulnerability is confined in a smaller domain. In virtualization contexts, guest OSes's kernel and all running applications are segregated in its own separated thread, in its own address-space. So, applying microkernels into virtualization domain requires highly paravirtualized VMs, which may be a drawback considering the required engineering effort. In opposition, functionality segregation, combined with clear microkernel interfaces ease to achieve a modular design, which brings benefits for testing, debugging and system scalability [11, 37].

## 2.3 Inter-Partition Communication

In virtualized environments VMs often need to communicate in order to exchange services. In non-virtualized machines communication happen through TCP/IP network stack, which could also be achieved in VMs. However, when communicating with co-resident machines, this entails unnecessary performance burden, because the infrastructure does not differentiate between data coming from the same machine and from outside the machine, processing it the same way, i.e., through TCP/IP network stack [38]. This could easily be circumvented by making the kernel aware of these scenarios while maintaining the abstraction, i.e., maintaining the interface for IPC mechanisms. This approach would traduce into gains of performance and software portability, as it would these mechanisms transparent to the user API, thus reducing the para-virtualization effort [38]. There already exists some work in virtualization exploiting this kind of approach like in

[39, 40], where shared memory facilities were used to circumvent the stack's software whenever the recipient IP belongs to the same machine as the sender. Given that embedded systems are highly cooperative systems, that often require synchronization facilities and faster data transmission mechanisms, user API transparency is often dropped in favor of performance.

Microkernels approaches heavily rely on IPC mechanisms for service provision due to the high segregation of VMs into domains, which work in favor of security, however, incurring into performance burden. Given the central role it possesses in microkernels, and also other types of highly cooperative infrastructures, it must be carefully designed as it could be exploited for possible attacks [41, 13, 9]. In [16] some requirements that IPC infrastructure must usually fulfill are presented:

- Reliable delivery, which refers to guaranteeing that messages are successfully delivered;

- Atomicity characterizes IPC operations as uninterruptible;

- Recipients endpoints must not be forgeable;

- The message's integrity is maintained though out the communication process;

- Multiple IPC calls must be independent from each other;

- Snooping traffic must also be impossible.

Also, when specifying system API, it should be taken into account that IPC system calls must be general enough to be applied in a plethora of contexts; however, IPC system calls must be powerful enough to reduce the number of system calls required, because the change between user and kernel modes usually deteriorates performance [13, 42].

#### 2.3.1 Policies and Mechanisms

There are two types of policies that are usually applied for message passing IPC mechanisms: synchronous and asynchronous. In synchronous communication, involved partitions meet at a given point in time to proceed the communication. This means that both are in a known state, i.e., the sender is in a sending state specifying the message to be transfered, while the receiver is prepared for the acceptance of a new message specifying the incoming message's buffer. Thus, at least one of them must be blocked waiting for the other to perform the complementary operation. Inherently there are some accruing benefits in terms of

performance and resource management. The data transfer can happen directly between address spaces, which will reduce the message propagation latency, and no buffering within the kernel is required [17, 16, 14]. Synchronous communication usually encompass a donation scheme, where in a client-server scenario the requester may donate its time execution in order to quicker resolve its dependency towards the server [43]. This is suitable for Remote Procedure Calls (RPC) abstractions, which consists on providing a interface to access services from a given server through the use of function calls. In this scenario, from the client's perspective, a function call is solely happening. However, it abstracts a sequence of IPC operations that sends the request and blocks waiting for the response. It also performs parameter marshallings and unmarshallings upon message sending and upon response arrival[10, 44, 16]. Apart from performance, a sound synchronous IPC design encompass security considerations, as synchronous communication is prone to DoS attacks, or even unintended deadlocks. One widely spoken problem of synchronous communication is the asymmetric-trust problem, which happens when multiple clients rely on the same server. In this relationship that works based on trust, there could be one badly intended partition that jeopardizes the execution of one of its siblings. Figure 2.4 depicts the different scenarios in which the asymmetric trust model becomes a problem. The best case scenario (A), both client and server perform their operations as supposed. Thus, the execution happens without incurring into problems to the system.

Figure 2.4: Representation of the asymmetric trust model.

On scenario (B) one malicious client may block the server infinitely, causing them to fail answering the requests from other clients. This problem can and should be considered in the opposite way, where a malicious server may cause a client to block, by failing to perform the desired operations at specific points in time (scenarios C and D) [16, 17]. Timeouts could be used in order to overcome these problems, however from L4 family experience [14] these are not effective, due to inappropriate use from user perspective, and also because it is not a good mensurable way to determine a given timeout value. Synchronous communication pushes a given system towards a purely multi-threaded environment, which forces functionality segregation, isolation and consequently enforces fault-containment. Nonetheless, it does not pose a definite solution against DoS but it helps to reduce the impacts of such an event [14, 16].

Regarding asynchronous communication, in contrast with the previous policy, message sending and reception does not meet at a specific point in time. Consequently, there is no blockage of any involved partition, therefore the asymmetric-trust problem is avoided [17, 16]. However, buffering within the kernel and, consequently, a double data copy are required. This makes partition execution more secure, but with an inherent performance cost [14]. There is no risk of directly causing a partition to fail; however, when not properly mediated, asynchronous communication is prone to suffer attacks of resource exhaustion, so there's the need to provide ICF mechanisms. Also, asynchronous communication can be paired with event mechanisms for interrupt execution upon message arrival [18], which in turn can also provide the opportunity for tampering a partition's execution.

Figure 2.5: Representation of the asymmetric trust model.

In both synchronous and asynchronous communication, one thing to have in mind is the IPC destination. Original L4 microkernel's implementation used threads as the destination of a given IPC operation. This would create the opportunity for a malicious entity to gather information which could be used to create an effective attack [18, 14]. Thus, the concept of endpoint was introduced and it consists on providing an abstraction to communication, from where messages could be read or write to. The most widely used concept is the notion of a *port* that usually is used as being the endpoint for message passing. Figure 2.5 depicts

the simple scenario for using *ports*. These could likely have an owner, who is intended to be the recipient for sent messages [14, 10, 19].

## 2.3.2 Review Of IPC security

In the literature there are some publications that aim at documenting IPC vulnerabilities in multiserver systems, as well as the attacks [16, 18, 17, 42]. Microkernel's principal of minimality, as explained in Section 2.2, aims at mitigating these effects by moving policies to userspace, preventing malfunctions to spread. Nonetheless, when designing an IPC infrastructure it must be considered where vulnerabilities may be located to prevent or mitigate possible attacks [19].

In [18] attacks have been documented as direct and indirect. Direct DoS attacks that aim at monopolizing a given resource, may cause another partition relying at the resource, or even the whole system, to fail. For example, sending a considerate amount of messages may cause a partition to spend most of its time dealing with messages, forbidding it from performing another concurrent task. Indirect attacks are those that aim at tampering the system's manager, thus not directly tampering a sibling partition, however jeopardizing its execution through means of the manager. For example, sending a lot of spurious messages, with the purpose of exhausting buffering resources. In [16, 17] these notions are extended with categorizing attacks according to the means of exploit. One means of exploit is the IPC subsystem by maliciously tampering the parameters of system calls, which, for example, may include a pointer to an invalid memory region, preventing the communication to happen. Another way to attack the IPC subsystem would be by exhausting memory resources, in the case they are dynamically allocated. The message delivery process is another concern, where addressing for IPC operations may also be secured, since partition A may not be intended to access services from partition B, thus by performing any communication attempt with partition B, could mean A was trying to tamper B. As such, there should be prevented identity spoofing by maliciously party. Another message delivery problem should be the payload size. There should exist prevention against memory overflows, in order to recipient's memory not be overwritten. Finally, another concern should be the established communication relationships and interactions between groups, in which many partitions can be blocked along the process. As previously explained in Section 2.3.1, synchronous communication requires mechanisms to prevent deadlocks and unwanted blocks to happen, as well as to avoid the asymmetric trust problem. In addition, quantum donation combined with

priority inheritance may introduce problems like priority inversion and starvation of low priority partitions [43].

Stated the problems that may occur whilst conceiving an IPC infrastructure, some solutions for them must be pointed out [16, 17]. Regarding attacks through the system call, parameter checking must be thoroughly deployed, namely to ensure that memory accesses are properly specified. To prevent deadlocks and unwanted blockage results, as aforementioned, there is no practical way of defining timeout values, as such, has been dropped in some microkernel implementations [14]. Asynchronous communication prevents these scenarios because partitions are not required to block throughout the communication process. The level of functional segregation inherent to microkernel-based systems also reduces the impact of an unwanted blockage.

## 2.4 Access-Control

Although Hypervisors and OSes already confine processes to their own sandbox, i.e., enforce separation between partitions preventing system failures and vulnerabilities to spread across the entire system, kernel APIs can still be exploited to cause some unwanted effects on the overall system [45]. Namely, system calls for message sending (among others) should be monitored to prevent malicious communications attempts, that aim at tampering a sibling's partition execution, or even exhaust message buffering resources [16]. Or a malicious partition may ask the system to erase page table entry that contain sensitive critical information. Thus, critical systems must be featured with mechanisms to prevent actions which are performed by unintended agents [19].

On OSes, access-control consists on creating mechanisms to restrict the way partitions operate on system's interfaces and resources, which usually requires the existence of a reference monitor that mediates every activity accessed by a given entity. These monitors must carry an authentication to prevent spoofing attacks, where a given subject masquerades its identity [46]. An important goal of these systems is to ensure that the principle of least-authority prevails. It states that partitions uniquely possess permissions to perform what strictly necessary. [47, 19] advocate that this is a requirement to have confinement within a system. There are also concerns regarding access control mechanisms' simplicity and granularity over resources. A mechanism can not be too simple that is easily fooled or provide more permissions than necessary, and at the same time should provide control over granularity regarding resources within a system [26].

Inside kernels there are two types of applied access policies: Mandatory Access Control (MAC) and Descritionary Access Control (DAC). The first refers to more rigid policies, that determine permissions are configured based on subjects and objects, in addition to being configured uniquely by a privilege entity, while the later refers to more flexible approaches, like the distributed scenario where permissions may be granted by more than one entity within a system [26, 46, 47], often by object owners [48].

## 2.4.1 Capability-based Access-Control

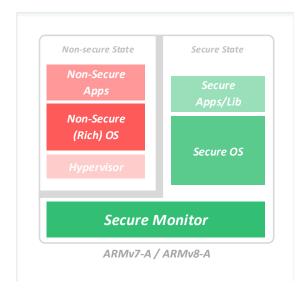

Capabilities are the de facto solution in distributed systems and microkernellike operating systems for access-control facilities [49]. In their simplest form, these are a reference to an object that can be assigned to one or more partitions [19]. Capability ownership implies some access permission over the referenced object, which in turn encapsulates functionality, accessible through a well-defined interface [19, 44]. In systems that are completely based in capabilities, all operations require the possession of one referencing the object which provides a given functionality, which may include communication objects in operating systems, as well as memory page-tables. The access monitor is the entity that manages the objects, which in this facility may be either the kernel to manage kernel objects, or even applications. An example of an application is a process that supports a file system may mediate files read and write operations recurring to capabilities [44]. Figure 2.6 depicts a general scenario of object access mediate through capabilities. Subject Y and Subject Z aim at performing one operation each. In order to do so, they should provide their capability to the *Objects Monitor*, that upon permissions verification will perform the operation on the referenced object.

Figure 2.6: Representation of the asymmetric trust model.

In capability-based access-control systems permissions are conveyable, meaning the set of permissions a given subject possesses may change over time [44, 47]. In order to do so, another subject within the system owning a capability, can ask the objects monitor to perform a grant operation, thus transferring a subset of its-own rights. The grant is, on itself, an operation whose permission must be set in the respective capability. In addition, a revocation operation is also usually available [20]. The existence of grant and revoke operations makes capabilities suitable to provide DAC-like access-control facilities. However, their use must be restricted to limit propagation towards intended subjects [19]. With these operations it is possible to achieve more rigid scenarios, that do not even change over time, like with MAC policies [26].

To make capabilities dependable there are a set of requirements that need to be met: subjects should not be capable of tampering capabilities, to either forge their identity nor possessing rights over an object; and, permission check must be lightweight to avoid performance degradation. This type of access-control facilities can be implemented in a centralized schema, in which protection is achieved by hardware or provided by the OS. In distributed scenarios the capability possesses owner's identity, thus protection is provided by means of signatures, preventing identity tamper towards unintended access [44, 50, 47].

Capabilities are also seen as the perfect fit to manage granularity and to support different types of objects for access-control, as it can be used to obliquely mediate access to a plethora of different types of objects [26]. The most obvious advantage in applying capabilities is for enhancing communication infrastructures with ICF. Thus, enforcing isolation provided, possibly, by a microkernel with containment of subsystems. This means, permissions configuration will influence how capabilities are granted over the time, thus aggregating and compartmentalizing groups of subjects in subsystems [44, 48].

## 2.5 Microkernels Related Work

Microkernels were not always a viable solution, due to the architecture's reliance on IPC, which constituted a bottleneck on system performance. The L4 microkernel, developed by Jochen Liedtke, appeared to break the stigma surrounding microkernels, proving their utility when providing efficient IPC mechanisms. L4 is the root of a family tree of microkernels that have a proven record of efficient performance and reliability, by following the core idea of kernel minimality and policy-void mechanisms [14]. In this section, we briefly survey some members of this family that served as the main source of inspiration for the ideas implemented in  $\mu$ RTZVisor, emphasizing those which aim to support virtualization.

Fiasco is an open-source descendant of L4 implemented in C++ aimed at security and critical real-time systems. It implements protected address spaces, synchronous IPC and a scheduler with multiple fixed-priority levels, whereby kernel executes a round-robing algorithm on threads characterized with the same priority [51, 52]. The latest version Fiasco.OC also includes capabilities for access-control, which are propagated through IPC [53]. In addition, capabilities are protected within the kernel memory, thus threads do not access directly to capabilities, making the access-control infrastructure reliable. Each partition possess a capability table, that maps the partition's access permissions into kernel resources. Capabilities are propagated through message passing facilities, and mapped into the capability table upon mapping request by the capability's recipient [19].

The NOVA microhypervisor [54] proposes a solution that deallocates virtualization to user space, which will inherently incur performance overhead and augmented engineering effort due to the highly para-virtualized approach, although augmenting security by significantly reducing TCB's size. As such, the kernel solely provides services for spacial and temporal isolation, in addition to message passing and synchronization mechanisms. Also, kernel operations require capabilities to access the kernel objects. Capabilities are immutable, and inaccessible in user-space, thus permissions are statically assigned and prevail through out system's execution. Accessing them is done by an integral number that works as the index for the domain's capability space. This happens every time a system call is performed. Destinations for IPC operations are endpoints designated by portals, which represent an entry to the owner's address space. In client-server communication, a reply capability can be granted to the server referencing a portal for the response to be addressed. Also, semaphores objects are provided for synchronization purposes. [55] presents Mini-NOVA, a simplified version of NOVA ported the Arm cortex-A9 architecture from the original x86 implementation. It aims at achieving lower overhead, smaller TCB size and higher security, thus making it more flexible and portable for embedded-systems.

PikeOS is an early spin-off of the L4 microkernel, whose purpose is to address requirements of safety-critical real-time embedded systems. It features spacial and temporal isolation, favoring minimum code size, in some cases to the detriment of flexibility [4]. It aims at providing a system that enables the coexistence of time-driven and event-driven partitions. The result is not the perfect fit for this kind of system, although by properly configuring each partition, it is possible to achieve a considerably good compromise [15]. It is also featured with access control facilities based on the *abilities* concept. To each partition is assigned a table with

abilities that is not expandable over time, where each entry represents a system call that the partition is allowed to perform. Given that partitions may be created dynamically, a parent partition may further restrict child's permissions, however it can never extend them. In addition, there were efforts on verifying functional correctness of PikeOS [56].

OKL4 adopts a microkernel approach completely directed at virtualization and, thus, is dubbed a microvisor [8]. It features a fast and reliable IPC, which is abstracted by channels and virtual interrupts for synchronization purposes. It implements only asynchronous IPC, which maps better to the VM model, and is less susceptible to DoS attacks. By the heritage of its seL4 predecessor, it provides access-control facilities based on capabilities, since any kernel operation requires one. OKL4 has been augmented to take advantage of the Arm virtualization extensions and support unmodified guest OSes [57].

EROS [47, 17] is a microkernel-based operating systems that was pioneer in providing access-control facilities based on capabilities. All system provided functionality is done by invoking a capability, providing the index from partition's capability list, referencing a kernel object. Regarding the IPC facility EROS provides three different primitives: send, call and return. The first performs a send operation and continues partition's normal flow, while the others block waiting for new messages. The laters distinction resides on the type of used capability to perform the operation. The call primitive will generate a reply capability for the recipient to use with a return primitive. This imposed semantic aims at safe client-server communication.

Finally, MINIX [58] is an open-source microkernel, firstly developed by Tannenbaum trying to prove the worth of microkernel principles towards trustworthy computer systems. Nowadays, the current available version is the MINIX3, that supports IPC operations through the use of ports as the destination for these operations. Most IPC primitives are synchronous, as this has been used for security evaluations regarding IPC policies [16]. In addition to support synchronous, it provides two asynchronous primitives, the *asend* that sends message without blocking the sender, and *notify* that provides an event delivery mechanism.

## 2.6 ARM Trustzone

TrustZone technology is a set of hardware security extensions, which have been available on Arm Cortex-A series processors for several years [59] and has recently

been extended to cover the new generation Cortex-M processor family. Trust-Zone for Armv8-M has the same high-level features as TrustZone for applications processors, but it is different in the sense that the design is optimized for microcontrollers and low-power applications. In the remainder of this section, when describing TrustZone, the focus will be on the specificities of this technology for Cortex-A processors (Figure 2.7).

Figure 2.7: RTZVisor system architecture.

The TrustZone hardware architecture virtualizes a physical core as two virtual cores, providing two completely separated execution environments: the secure and the non-secure worlds. A new 33rd processor bit, the Non-Secure (NS) bit, indicates in which world the processor is currently executing. To preserve the processor state during the world switch, TrustZone adds an extra processor mode: the monitor mode. The monitor mode is completely different from other modes because, when the processor runs in this privileged mode, the state is always considered secure, independently of the NS bit state. Software stacks in the two worlds can be bridged via a new privileged instruction-Secure Monitor Call (SMC). The monitor mode can also be entered by configuring it to handle interrupts and exceptions in the secure side. To ensure a strong isolation between secure and non-secure states, some special registers are banked, while others are either totally unavailable for the non-secure side.

The TrustZone Address Space Controller (TZASC) and the TrustZone Memory Adapter (TZMA) extend TrustZone security to the memory infrastructure. TZASC can partition the DRAM into different secure and non-secure memory regions, by using a programming interface which is only accessible from the secure side. By design, secure world applications can access normal world memory, but

the reverse is not possible. TZMA provides similar functionality but for off-chip Read-Only Memory (ROM) or Static Random-Access Memory (SRAM). Both the TZASC and TZMA are optional and implementation-specific components on the TrustZone specification. In addition, the granularity of memory regions depends on the System on Chip (SoC). The TrustZone-aware MMU provides two distinct MMU interfaces, enabling each world to have a local set of virtual-to-physical memory address translation tables. The isolation is still available at the cache-level because processor's caches have been extended with an additional tag that signals in which state the processor accessed the memory.

System devices can be dynamically configured as secure or non-secure through the TrustZone Protection Controller (TZPC). The TZPC is also an optional and implementation-specific component on the TrustZone specification. To support the robust management of secure and non-secure interrupts, the Generic Interrupt Controller (GIC) provides both secure and non-secure prioritized interrupt sources. The interrupt controller supports interrupt prioritization, allowing the configuration of secure interrupts with a higher priority than the non-secure interrupts. Such configurability prevents non-secure software from performing a Denial-Of-Service (DoS) attack against the secure side. The GIC also supports several interrupt models, allowing for the configuration of Interrupt Request (IRQ)s and Fast Interrupt Request (FIQ) as secure or non-secure interrupt sources.

## 2.7 RTZVisor