# **Universidade do Minho** Escola de Engenharia Departamento de Eletrónica

Ana Cláudia Rodrigues Ferreira

Rectification, amplification and switching capabilities for energy harvesting systems

Power management circuit for piezoelectric energy harvester

**Universidade do Minho** Escola de Engenharia Departamento de Eletrónica

Ana Cláudia Rodrigues Ferreira

**Rectification, amplification and switching capabilities for energy harvesting systems**

Power management circuit for piezoelectric energy harvester

Master dissertation Master Degree in Biomedical Engineering

Dissertation supervised by Tao Dong José Correia

July 2020

# DIREITOS DE AUTOR E CONDIÇÕES DE UTILIZAÇÃO DO TRABALHO POR TERCEIROS

Este é um trabalho académico que pode ser utilizado por terceiros desde que respeitadas as regras e boas práticas internacionalmente aceites, no que concerne aos direitos de autor e direitos conexos.

Assim, o presente trabalho pode ser utilizado nos termos previstos na licença abaixo indicada.

Caso o utilizador necessite de permissão para poder fazer um uso do trabalho em condições não previstas no licenciamento indicado, deverá contactar o autor, através do RepositóriUM da Universidade do Minho.

# Licença concedida aos utilizadores deste trabalho

Atribuição CC BY

https://creativecommons.org/licenses/by/4.0/

#### ACKNOWLEDGEMENTS

First of all, I want to thank my project supervisor at the University of South-Eastern Norway, Professor Tao Dong, for all the support, supervision and motivational speeches. Those were imperative to the progress of my master's thesis.

My appreciation goes to my supervisor at the University of Minho, Professor José Correia, throughout my academic period, his lectures, the relationship with his students and always being available for me.

I am grateful for the contact with Professor Zhaochu Yang from Chongqing Technology and Business University (CTBU), and Ph.D. Haakon Karlsen from Sensovann AS, whose wise advice and contact with the industry sector gave me skills regarding project management and proposal writing. I also would like to thank Ph.D. student Rui Carvalho, whose cooperation in the project was valuable to its development through interdisciplinary discussions and motivation. Acknowledgment also goes to Ph.D. Marino Maciel for the thorough manuscript review.

I want to thank all my research colleagues at the University of South-Eastern Norway for the assistance and support throughout my studies. Likewise, I have to thank all my fellow course colleagues and friends at the University of Minho. Together we overcame all the adversities through our academic years. My friends should also be mentioned here since their support and motivation helped me to get where I am today.

Finally, a special thanks to my parents and sister, who were always by my side, encouraging me to pursue my dreams. Further thanks to all my family.

Thank you! Tusen takk! Obrigada!

# STATEMENT OF INTEGRITY

I hereby declare having conducted this academic work with integrity. I confirm that I have not used plagiarism or any form of undue use of information or falsification of results along the process leading to its elaboration.

I further declare that I have fully acknowledged the Code of Ethical Conduct of the University of Minho.

#### RESUMO

Para combater a dependência dos dispositivos eletrónicos relativamente ás baterias é necessário um novo sistema energético, que permita prolongar o tempo de vida útil dos mesmos. Energy Harvesting é uma tecnologia promissora utilizada para alimentar dispositivos sem bateria. Este trabalho consiste na realização de componentes empregáveis num circuito global para extrair energia a partir ds vibrações de um piezoelétricos com baixo consumo de energia e alta eficiência. Os níveis de potência e voltagem gerados pelo transdutor piezoelétrico são relativamente baixos, especialmente em sistemas de pequena escala, por isso requerem cuidado extra relativamente ao consumo de energia e eficiência dos circuitos.

A principal contribuição deste trabalho é um sistema apropriado para amplificar, retificar e alternar o sinal instável proveniente de uma fonte de energy harvesting. Os componentes do sistema são implementados com base na tecnologia CMOS com  $0.13 \, \mu m$ .

Um interruptor analógico capaz de modelar a frequência do sinal entre 1 Hz e 1 MHz e estável perante variações de temperatura, é implementado. O circuito tem um excelente isolamento de -111.24 dB, devido a uma resistência OFF de  $520.6 M\Omega$ .

O amplificador implementado é apto a amplificar um pequeno sinal com um ganho de 42.56 dB e baixo consumo. O sinal de saída é satisfatoriamente amplificado com uma voltagem de offset de  $8 \mu V$ .

Um retificador ativo de dois estágios com uma nova arquitetura é proposto. A eficiência de conversão de energia atinge os 40.4%, com uma eficiência de voltagem até 90%. O retificador consome pouca energia, apenas 17.7  $\mu$ W, incorporando um comparador de 113.9 *n*W.

Os resultados validam as exigências energéticas do circuito, que pode ser usado para outras aplicações similares no campo biomédico, industrial e comercial.

Palavras-chave: Interruptor analógico, CMOS, Energy Harvesting, Rectificador, Amplificador.

#### ABSTRACT

A new energy mechanism needs to be addressed to overcome the battery dependency, and consequently extend Wireless Sensor Nodes (WSN) lifetime effectively. Energy Harvesting is a promising technology that can fulfill that premise. This work consists of the realization of circuit components employable in a management system for a piezoelectric-based energy harvester, with low power consumption and high efficiency. The implementation of energy harvesting systems is necessary to power-up front-end applications without any battery. The input power and voltage levels generated by the piezoelectric transducer are relatively low, especially in small-scale systems, as such extra care has to be taken in power consumption and efficiency of the circuits.

The main contribution of this work is a system capable of amplifying, rectifying and switching the unstable signal from an energy harvester source. The circuit components are designed based on  $0.13 \,\mu m$  Complementary Metal-Oxide-Semiconductor (CMOS) technology.

An analog switch, capable of driving the harvesting circuit at a frequency between 1 Hz and 1 MHz, with proper temperature behaviour, is designed and verified. An OFF resistance of  $520.6 M\Omega$  and isolation of -111.24 dB, grant excellent isolation to the circuit.

The designed voltage amplifier is capable of amplifying a minor signal with a gain of 42.56 dB, while requiring low power consumption. The output signal is satisfactorily amplified with a reduced offset voltage of 8  $\mu V$ .

A new architecture of a two-stage active rectifier is proposed. The power conversion efficiency is 40.4%, with a voltage efficiency of up to 90%. Low power consumption of  $17.7 \,\mu W$  is achieved by the rectifier, with the embedded comparator consuming  $113.9 \,nW$ .

The outcomes validate the circuit's power demands, which can be used for other similar applications in biomedical, industrial, and commercial fields.

Keywords: Analog Switch, CMOS, Energy Harvesting, Rectifier, Voltage Amplifier.

# CONTENTS

| 1 | Intro | oduction  |                                     | 1  |

|---|-------|-----------|-------------------------------------|----|

|   | 1.1   | Motivat   | tion and Applications               | 1  |

|   | 1.2   | Energy    | / Harvesting                        | 3  |

|   | 1.3   | Piezoe    | lectric Transducer                  | 6  |

|   | 1.4   | Project   | t Implementation                    | 7  |

|   | 1.5   | Thesis    | Organization                        | 9  |

| 2 | Stat  | te of the | art                                 | 11 |

|   | 2.1   | Analog    | g Switch                            | 11 |

|   |       | 2.1.1     | Direct Energy Transfer              | 12 |

|   |       | 2.1.2     | Load Decoupling Interfaces          | 16 |

|   |       | 2.1.3     | Switching Techniques Summary        | 20 |

|   | 2.2   | Voltage   | e Amplifier                         | 21 |

|   |       | 2.2.1     | Amplifier Modes                     | 21 |

|   |       | 2.2.2     | Piezoelectric Amplification Patents | 23 |

|   |       | 2.2.3     | Amplifier Topologies                | 24 |

|   | 2.3   | Rectifie  | er                                  | 27 |

|   |       | 2.3.1     | Conventional Rectifier              | 28 |

|   |       | 2.3.2     | CMOS Rectifier                      | 32 |

| 3 | Dev   | elopmer   | nt and Results                      | 46 |

|   | 3.1   | Analog    | g Switch                            | 46 |

|     | 3.1.1                           | Up-conversion Technique                                                                                                                                                                                                                                                                                                                                                                | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 3.1.2                           | Management System                                                                                                                                                                                                                                                                                                                                                                      | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.1.3                           | Features                                                                                                                                                                                                                                                                                                                                                                               | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.1.4                           | Results                                                                                                                                                                                                                                                                                                                                                                                | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.1.5                           | Discussion                                                                                                                                                                                                                                                                                                                                                                             | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.1.6                           | Summary                                                                                                                                                                                                                                                                                                                                                                                | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.2 | Voltage                         | Amplifier                                                                                                                                                                                                                                                                                                                                                                              | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.2.1                           | Design and Modeling                                                                                                                                                                                                                                                                                                                                                                    | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.2.2                           | Features                                                                                                                                                                                                                                                                                                                                                                               | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.2.3                           | Results                                                                                                                                                                                                                                                                                                                                                                                | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.2.4                           | Discussion                                                                                                                                                                                                                                                                                                                                                                             | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.2.5                           | Summary                                                                                                                                                                                                                                                                                                                                                                                | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.3 | Rectifie                        | er                                                                                                                                                                                                                                                                                                                                                                                     | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.3.1                           | Design and Modeling                                                                                                                                                                                                                                                                                                                                                                    | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.3.2                           | Proposed Rectifier                                                                                                                                                                                                                                                                                                                                                                     | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.3.3                           | Results                                                                                                                                                                                                                                                                                                                                                                                | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.3.4                           | Discussion                                                                                                                                                                                                                                                                                                                                                                             | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.3.5                           | Summary                                                                                                                                                                                                                                                                                                                                                                                | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.4 | Layout                          | Design and Fabrication                                                                                                                                                                                                                                                                                                                                                                 | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.4.1                           | Layout Design                                                                                                                                                                                                                                                                                                                                                                          | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.4.2                           | Chip Fabrication                                                                                                                                                                                                                                                                                                                                                                       | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Cor | nclusion                        |                                                                                                                                                                                                                                                                                                                                                                                        | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.1 | Conclu                          | sions                                                                                                                                                                                                                                                                                                                                                                                  | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.2 | Future                          | Work                                                                                                                                                                                                                                                                                                                                                                                   | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Sup | port ma                         | terial                                                                                                                                                                                                                                                                                                                                                                                 | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 3.3<br>3.4<br>Cor<br>4.1<br>4.2 | <ul> <li>3.1.2</li> <li>3.1.3</li> <li>3.1.4</li> <li>3.1.5</li> <li>3.1.6</li> <li>3.1.6</li> <li>3.1.6</li> <li>3.1.6</li> <li>3.2.1</li> <li>3.2.2</li> <li>3.2.3</li> <li>3.2.4</li> <li>3.2.5</li> <li>3.3</li> <li>3.4.1</li> <li>3.4.2</li> <li>3.4.1</li> <li>3.4.2</li> <li>3.4.1</li> <li>3.4.2</li> <li>4.1</li> <li>Conclusion</li> <li>4.1</li> <li>Conclusion</li> </ul> | 3.1.2Management System3.1.3Features3.1.4Results3.1.5Discussion3.1.6Summary3.1Design and Modeling3.2.1Features3.2.3Results3.2.4Discussion3.2.5Summary3.7Rectfier3.3.1Design and Modeling3.3.2Proposed Rectfier3.3.3Results3.3.4Discussion3.3.5Summary3.4Discussion3.3.6Summary3.4Discussion3.3.7Cip Fabrication3.4Apout Design3.4Discussion3.4Cip Fabrication3.4Cip Fabrication3.4Cip Fabrication3.4Cip Fabrication3.4Cip Fabrication3.4Cip Fabrication |

# A.1 List of Publications

110

# LIST OF FIGURES

| Figure 1  | Biomedical applications requiring energy harvesting: (a) intra-cardiac implant pla   | iced   |

|-----------|--------------------------------------------------------------------------------------|--------|

|           | in the heart cavity scavenging energy from regular blood pressure (Deterre et        | al.,   |

|           | 2013); (b) a polyvinylidene fluoride harvester that extract energy from the arterial | wall   |

|           | deformation (Yang et al., 2018); (c) implanted arterial cuff power source integra    | ated   |

|           | into a self-powered blood pressure sensing system (Potkay and Brooks, 2008)          | and    |

|           | (d) flexible retinal implant device (Hwang et al., 2015).                            | 3      |

| Figure 2  | Overall share of energy from renewable sources in some the European Union merr       | ıber   |

|           | states (Eurostat Statistic Explained, 2020).                                         | 4      |

| Figure 3  | Comparison of energy sources with a fixed level of power generation (Roundy et       | : al., |

|           | 2003; Roundy et al., 2005; Cao et al., 2007). (A), (B) and (C) are vibration piezoe  | elec-  |

|           | tric, electromagnetic and electrostatic, respectively; (D) is a thermoelectric sou   | irce;  |

|           | (E), (F) and (G) are solar energy directly from sunlight on a clear weather day, o   | on a   |

|           | cloudy day and indoor, correspondingly.                                              | 5      |

| Figure 4  | General schematic of a vibration piezoelectric energy harvester.                     | 6      |

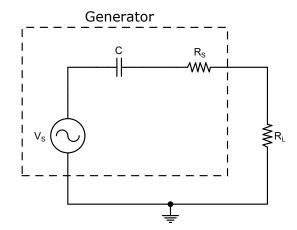

| Figure 5  | Equivalent circuit for a piezoelectric generator.                                    | 7      |

| Figure 6  | Circuit schematic of the standard energy harvesting interface.                       | 12     |

| Figure 7  | Circuit schematic of the S-SSHI rectifier.                                           | 12     |

| Figure 8  | Circuit schematic of the P-SSHI rectifier.                                           | 13     |

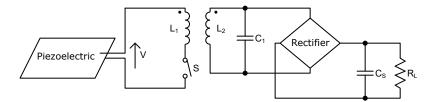

| Figure 9  | Circuit diagram of the MR-SSHI.                                                      | 14     |

| Figure 10 | Schematic of the Hybrid SSHI rectifier.                                              | 15     |

| Figure 11 | Circuit diagram of the SSDCI rectifier.                                              | 16     |

| Figure 12 | Schematic of the SECE and the PS-SECE recifiers.                                     | 17     |

| Figure 13 | Circuit schematic of the DSSH, ESSH and ASSH rectifiers.                             | 18     |

| Figure 14 | Circuit schematic of the energy injection technique.                                 | 19     |

| Figure 15 | Circuit of a voltage mode amplifier.(Karki, 2000)                                    | 22     |

|           |                                                                                      |        |

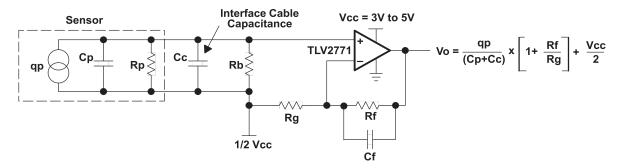

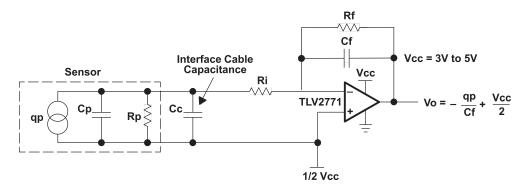

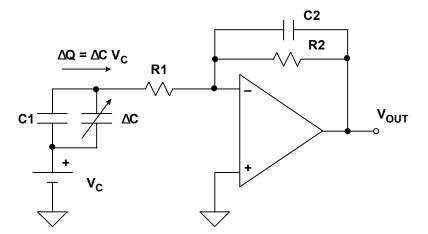

| Figure 16 | Circuit of a charge mode amplifier. (Karki, 2000)                                 | 22     |

|-----------|-----------------------------------------------------------------------------------|--------|

| Figure 17 | Schematic circuit of charge amplifier. (Jung, 2004)                               | 24     |

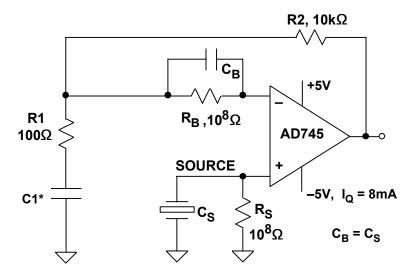

| Figure 18 | Schematic of a piezoelectric sensor amplifier. (Jung, 2004)                       | 25     |

| Figure 19 | Circuit diagram of the vibration system. (Li et al., 2011)                        | 26     |

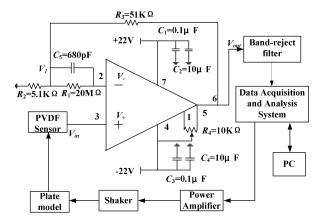

| Figure 20 | Circuit diagram of the operational amplifying system. (Jeong et al., 2019)        | 27     |

| Figure 21 | Schematic circuit of a booster. (Barcola et al., 2016)                            | 27     |

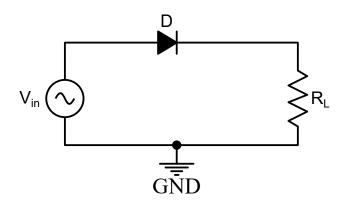

| Figure 22 | Schematic circuit of the half-wave rectifier.                                     | 28     |

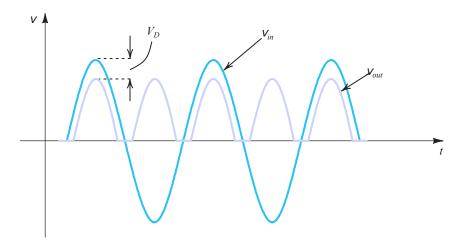

| Figure 23 | Half-wave rectifier: (a) input waveform and (b) output waveform rectified. (Sedra | and    |

|           | Smith, 2014)                                                                      | 29     |

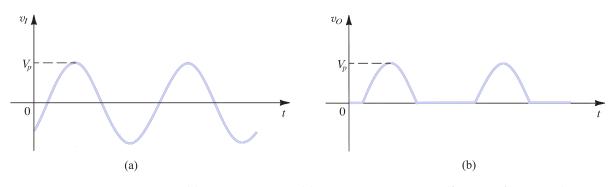

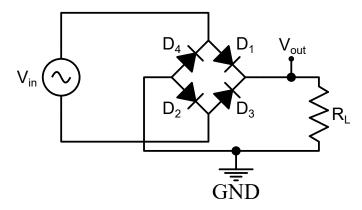

| Figure 24 | Schematic circuit of the full-wave rectifier.                                     | 29     |

| Figure 25 | Input and output waveforms of a full-wave rectifier. (Sedra and Smith, 2014)      | 30     |

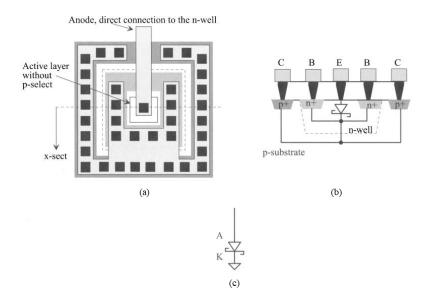

| Figure 26 | Schottky diode: (a) layout, (b) cross-section and (c) symbol. (Baker, 2010)       | 31     |

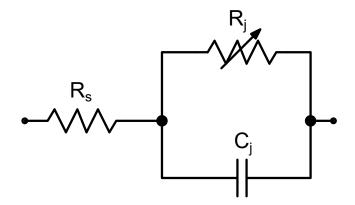

| Figure 27 | Schottky diode equivalent linear circuit model.                                   | 31     |

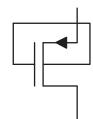

| Figure 28 | DTMOS configuration. (Babacan, 2018)                                              | 33     |

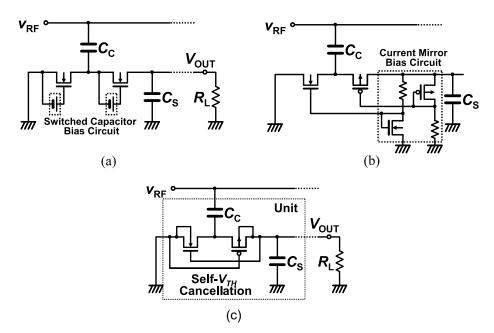

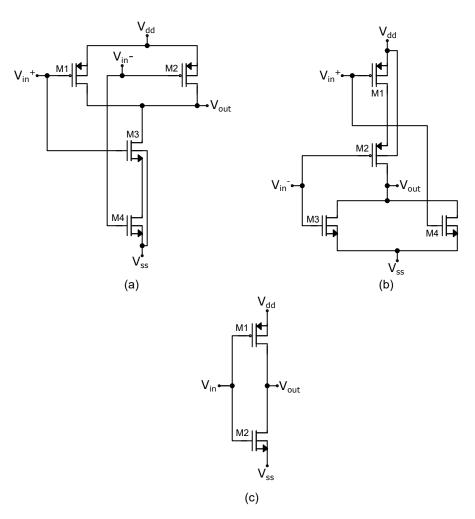

| Figure 29 | Circuit of the (a) EVC, (b) IVC and (c) SVC techniques. (Kotani and Ito, 2009)    | 35     |

| Figure 30 | Schematic of the IVC technique combined with switches. (Nguyen et al., 2014)      | 35     |

| Figure 31 | Schematic of a rectifier combining an active diode with an op-amp. (Sun ef        | t al., |

|           | 2012)                                                                             | 36     |

| Figure 32 | Circuit of an op-amp with a compensation block. (Kakoty, 2011)                    | 37     |

| Figure 33 | Circuit of a bridgeless rectifier. (Wang et al., 2013)                            | 37     |

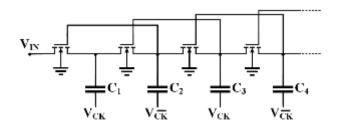

| Figure 34 | Dickson charge pump with NMOS transistors. (Ballo et al., 2019)                   | 38     |

| Figure 35 | Dickson charge pump rectifier. (Wong et al., 2016)                                | 38     |

| Figure 36 | Circuit design of a full-wave passive rectifier. (Le et al., 2006)                | 39     |

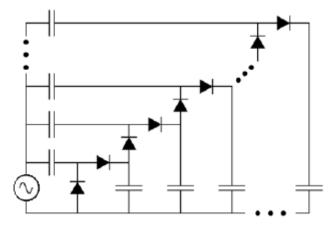

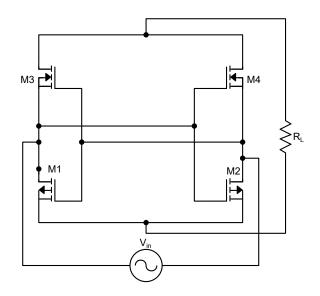

| Figure 37 | Schematic of a full-wave cross-couple rectifier.                                  | 40     |

| Figure 38 | Schematic of the full-wave cross-couple rectifier. (Hashemi et al., 2009)         | 41     |

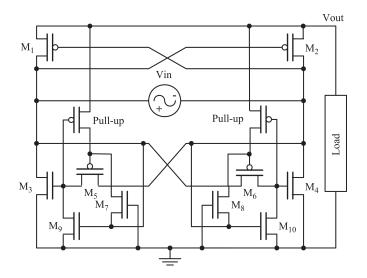

| Figure 39 | Full-wave active rectifier: (a) schematic diagram and (b) implemented active di   | iode.  |

|           | (Lam et al., 2006)                                                                | 42     |

| Figure 40 | Design of the comparator and respective sub-circuits. (Peters et al., 2010)       | 43     |

| Figure 41 | Schematic of the frequency up-conversion rectifier.                               | 47     |

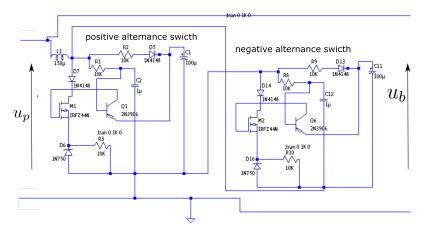

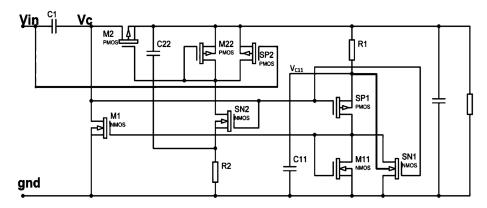

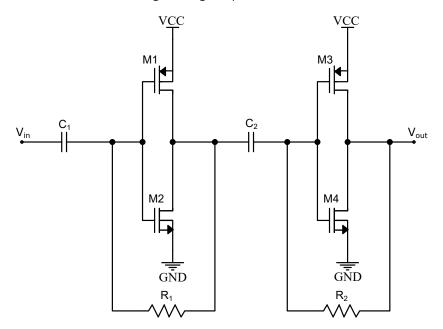

| Figure 42 | Circuit diagram of the switching approach for vibrational energy harvesting.      | 48     |

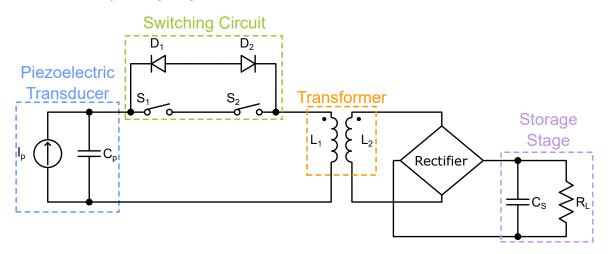

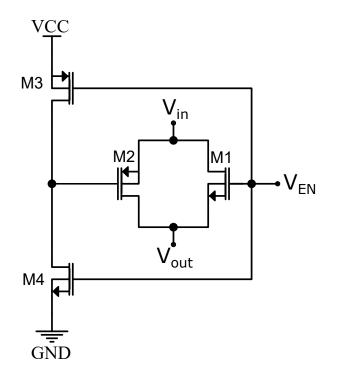

| Figure 43 | Analog switch schematic for the switching circuit.                                               | 51               |

|-----------|--------------------------------------------------------------------------------------------------|------------------|

| Figure 44 | Enchanced analog switch coupling the (a) conventional switch with a (b) cur                      | rrent            |

|           | starved technique.                                                                               | 52               |

| Figure 45 | Operation principle representation of the designed analog switch, including the i                | nput             |

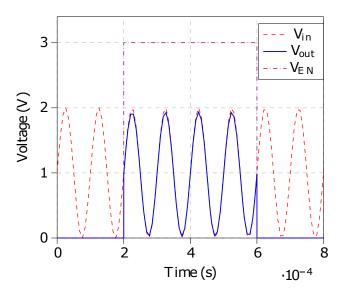

|           | signal ( $V_{in}$ ), enable signal ( $V_{EN}$ ) and the output waveform ( $V_{out}$ ).           | 54               |

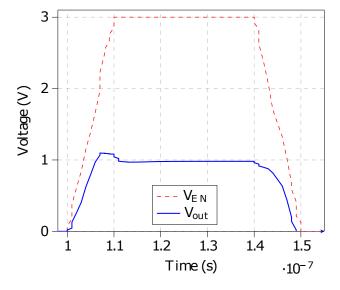

| Figure 46 | Switching speed estimation of the analog switch, with representation of the sign                 | ial to           |

|           | enable ( $V_{EN}$ ) and the output signal ( $V_{out}$ ).                                         | 55               |

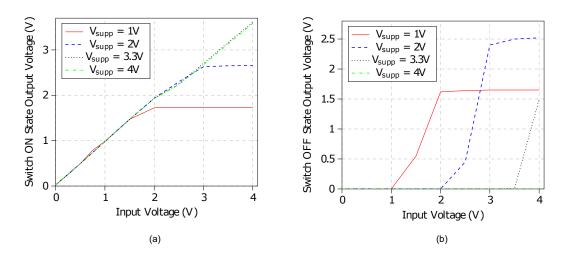

| Figure 47 | Output signal of the analog switch in (a) ON ( $V_{out,ON}$ ) and (b) OFF ( $V_{out,ON}$         | <sub>OFF</sub> ) |

|           | states, according to the input ( $V_{in}$ ) and supply ( $V_{supp}$ ) voltages.                  | 56               |

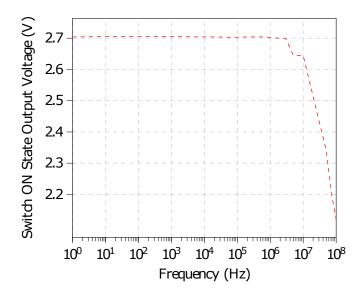

| Figure 48 | Operational frequency range of the analog switch, representing the output vol                    | Itage            |

|           | during the switch conducting state ( $V_{out,ON}$ ).                                             | 57               |

| Figure 49 | Output voltage when the switch is closed ( $V_{out,ON}$ ) and supply current ( $I_{supp}$ ) u    | nder             |

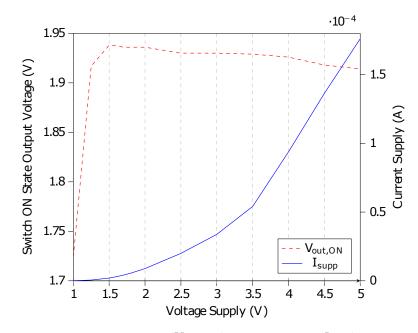

|           | different voltages supply.                                                                       | 58               |

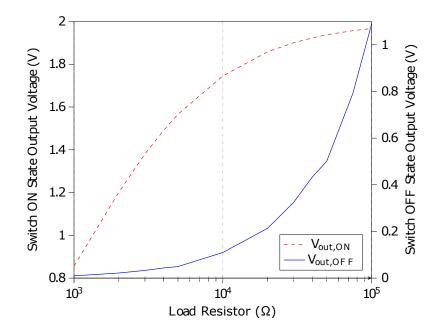

| Figure 50 | Output voltage when the switch is in conducting ( $V_{out,ON}$ ) and in non-conducting           | cting            |

|           | $(V_{out,OFF})$ states, through different ohmic load values.                                     | 59               |

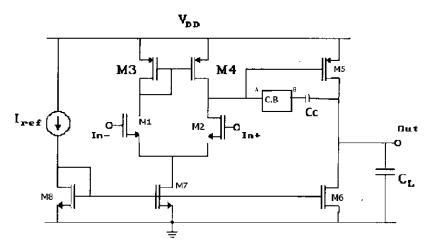

| Figure 51 | Circuit schematic of the designed voltage amplifier.                                             | 62               |

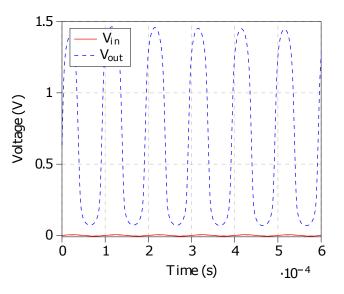

| Figure 52 | Input signal ( $V_{in}$ ) and amplified output signal ( $V_{out}$ ) of the projected amplifier.  | 65               |

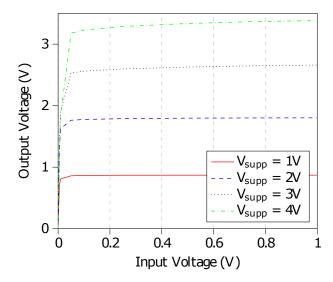

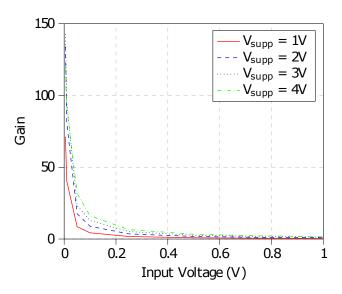

| Figure 53 | Output signal ( $V_{out}$ ) of the voltage amplifier through different input ( $V_{in}$ ) and su | ipply            |

|           | $(V_{supp})$ voltages.                                                                           | 65               |

| Figure 54 | Gain versus input voltages, according to the variation of supply voltages of the                 | e de-            |

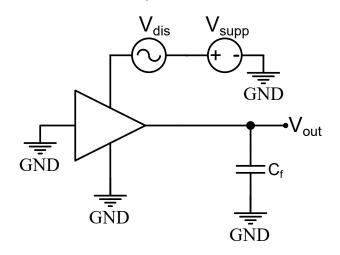

|           | signed voltage amplifier.                                                                        | 66               |

| Figure 55 | Circuit used for PSRR simulation of the amplifier.                                               | 66               |

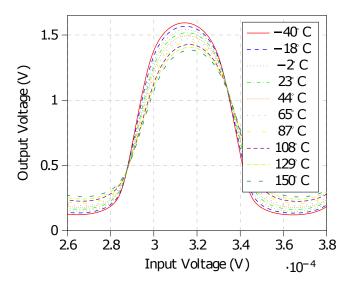

| Figure 56 | Output signal of the amplifier according to the variation of the temperature.                    | 68               |

| Figure 57 | Layout of a full-wave rectifier using Schottky diodes.                                           | 72               |

| Figure 58 | Schematic design of a full-wave rectifier with cross-couple PMOS.                                | 73               |

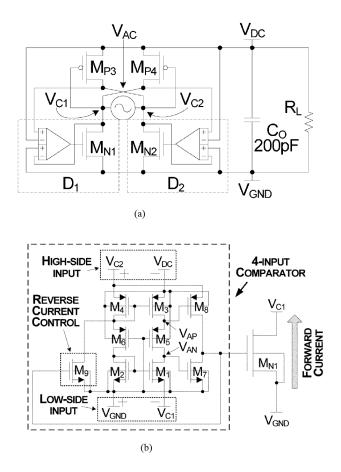

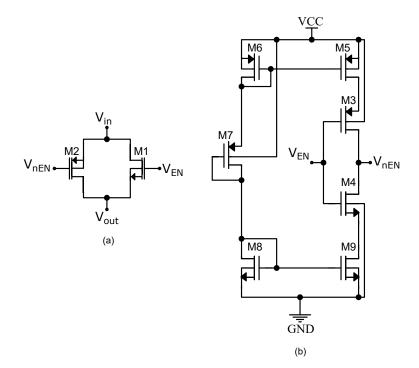

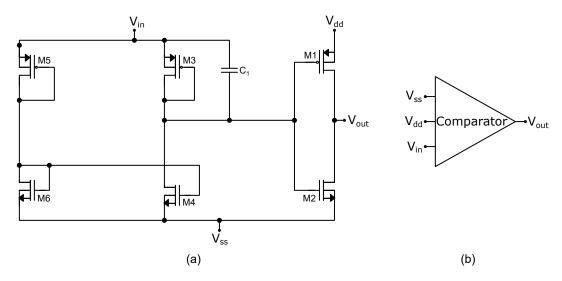

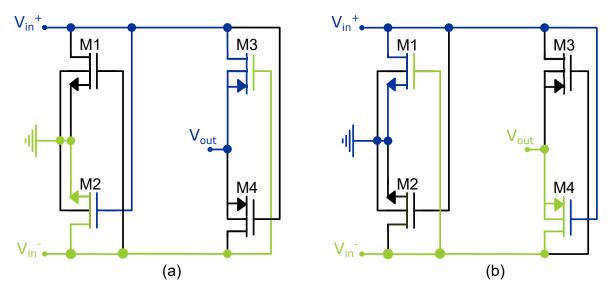

| Figure 59 | Design of a comparator: (a) schematic and respective (b) symbol.                                 | 73               |

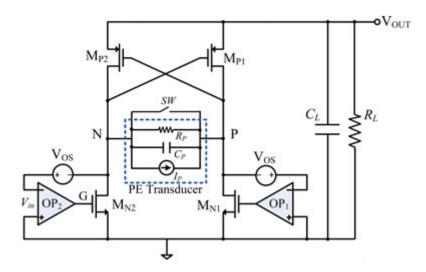

| Figure 60 | Structure of a full-wave active rectifier.                                                       | 74               |

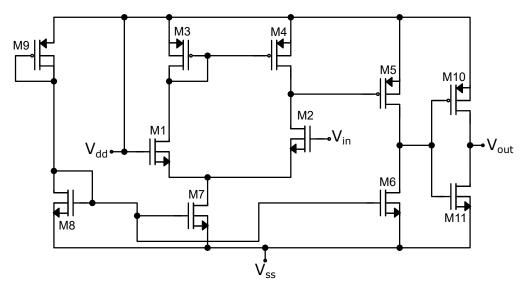

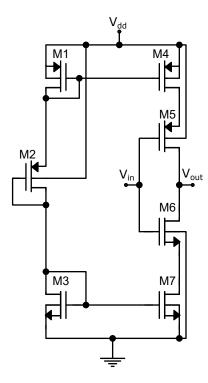

| Figure 61 | Circuit design of a four-stage comparator.                                                       | 75               |

| Figure 62 | Schematic of the logic gate: (a) NAND, (b) NOR, and (c) NOT.                                     | 77               |

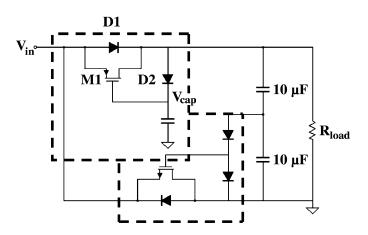

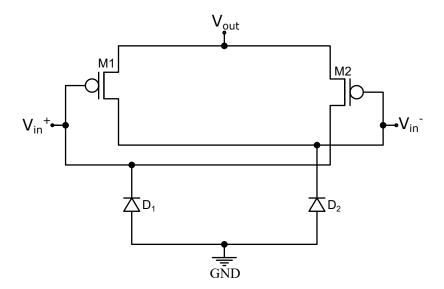

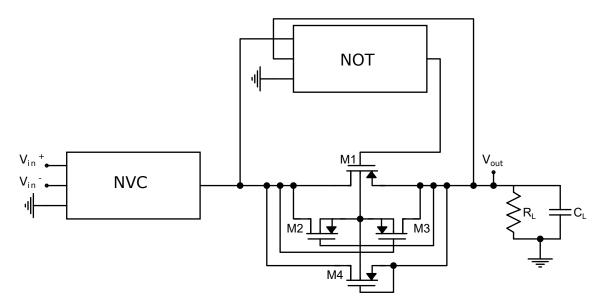

| Figure 63 | Projected two-stage active rectifier circuit.                                                    | 79               |

|           |                                                                                                  |                  |

| Figure 64 | Negative voltage converter circuit conducting for (a) positive and (b) negative                    | half- |

|-----------|----------------------------------------------------------------------------------------------------|-------|

|           | cycles.                                                                                            | 79    |

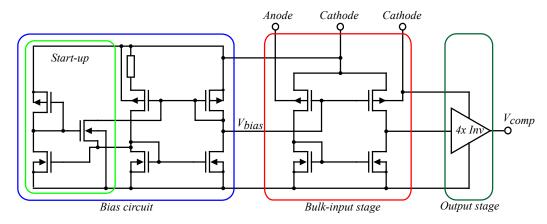

| Figure 65 | Comparator circuit implemented by a ${\scriptstyle \rm NOT}$ gate with starving current technique. | 82    |

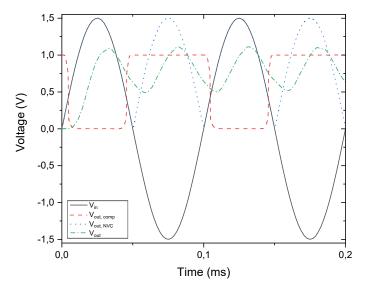

| Figure 66 | Operational principle of the NVC ( $V_{out,NVC}$ ), the comparator ( $V_{out,comp}$ ), and         | l the |

|           | rectifier ( $V_{out}$ ), with $V_{in}$ as the input signal for each simulation.                    | 83    |

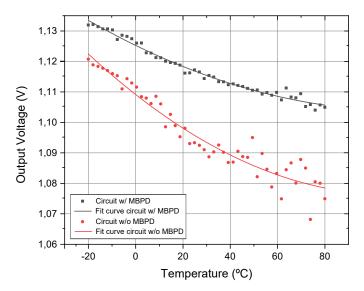

| Figure 67 | Output voltage according to the temperature variation, with and without the ME                     | 3PD,  |

|           | and 2nd order polynomial fitting.                                                                  | 84    |

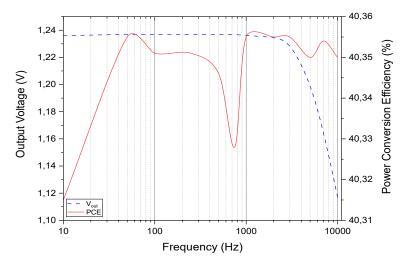

| Figure 68 | Output voltage and power conversion efficiency through different frequencies.                      | 85    |

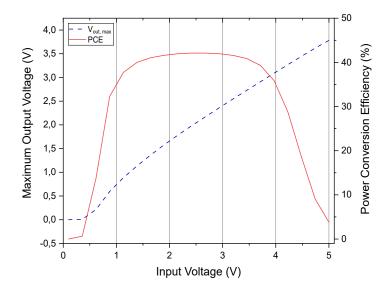

| Figure 69 | Output voltage and power conversion efficiency values, according to input vol                      | tage  |

|           | variations.                                                                                        | 86    |

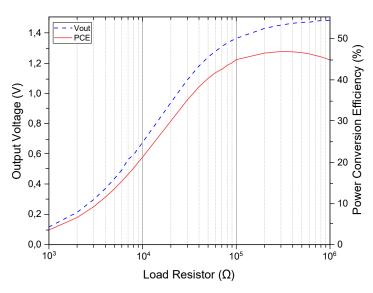

| Figure 70 | Simulated output voltage and power conversion efficiency through different of                      | ımic  |

|           | load values.                                                                                       | 86    |

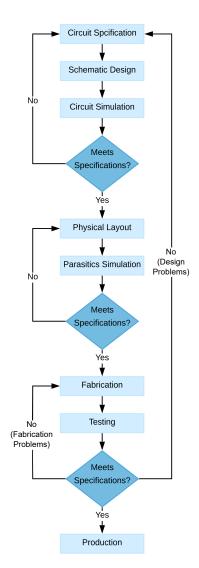

| Figure 71 | Diagram flow of the CMOS process fabrication.                                                      | 90    |

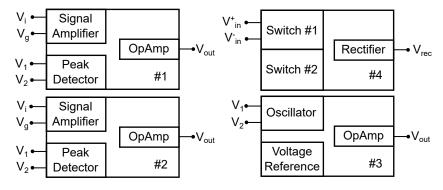

| Figure 72 | IC block representation.                                                                           | 91    |

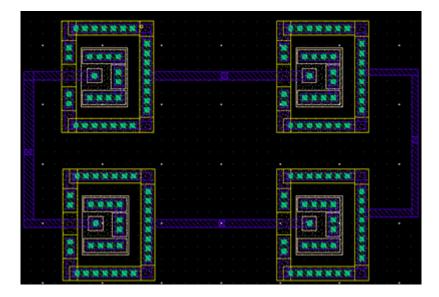

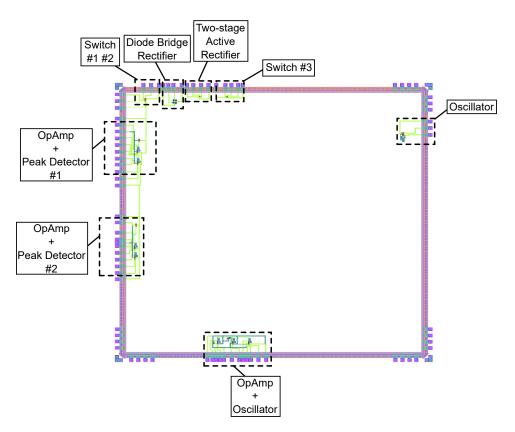

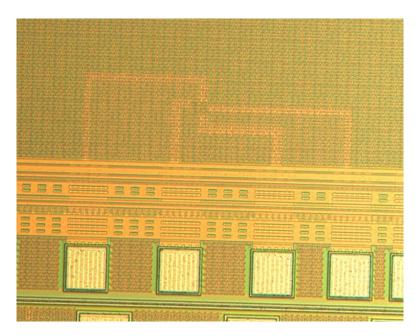

| Figure 73 | Complete layout of the energy harvesting system with each sub-circuit labeled.                     | 93    |

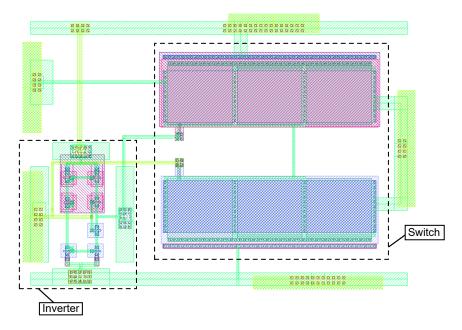

| Figure 74 | Layout design of the analog circuit, including the inverter and the standard switch.               | 94    |

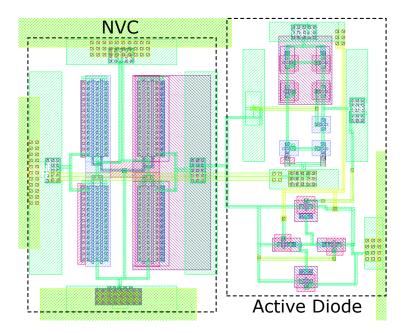

| Figure 75 | Layout design of the two-stage active rectifier, including the negative voltage conve              | erter |

|           | and the active diode.                                                                              | 95    |

| Figure 76 | Microscope view, with $50	imes$ amplification, of the two-stage active rectifier implement         | nted  |

|           | on the IC chip.                                                                                    | 96    |

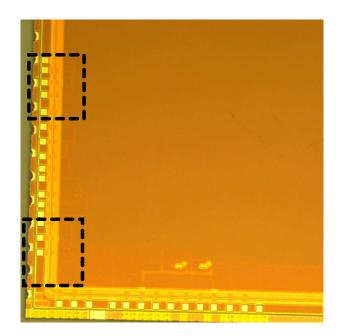

| Figure 77 | Microscope view, with $25\times$ amplification, of the analog switch on the fabric                 | ated  |

|           | chip.                                                                                              | 96    |

# LIST OF TABLES

| Table 1  | Transducers for different ambient energy sources.                         | 4      |

|----------|---------------------------------------------------------------------------|--------|

| Table 2  | State-of-the-art piezoelectric harvesting interfaces.                     | 20     |

| Table 3  | Comparison of the state-of-the-art of convencional rectifier topologies.  | 32     |

| Table 4  | Comparison of the state-of-the-art of CMOS rectifier topologies.          | 45     |

| Table 5  | Dimensions of the switching circuit transistors.                          | 53     |

| Table 6  | Comparison of proposed analog switch with off-the-shelf components.       | 61     |

| Table 7  | Specifications of the voltage amplifier circuit components.               | 63     |

| Table 8  | Comparison of the proposed voltage amplifier with commercial components.  | 69     |

| Table 9  | Diodes model and respective SPICE parameters.                             | 71     |

| Table 10 | Dimensions of the transistors from the comparator circuit.                | 72     |

| Table 11 | Dimensions of the transistors from the active rectifier.                  | 75     |

| Table 12 | Dimensions of the transistors of the four-stage comparator.               | 76     |

| Table 13 | Performance summary of different logic gates in a full-wave and two stage | active |

|          | rectifiers topologies.                                                    | 78     |

| Table 14 | Dimensions of the transistors from the proposed comparator circuit.       | 82     |

| Table 15 | Comparison of the proposed rectifier with other previously reported.      | 87     |

| Table 16 | Pins description of the energy harvesting IC system.                      | 91     |

| Table 17 | Integrated circuit die fabrication report.                                | 95     |

# ACRONYMS

| A                                                    |

|------------------------------------------------------|

| <b>AC</b> Alternating Current.                       |

| ADC Analog-to-Digital Converters.                    |

| ASIC Application-Specific Integrated Circuit.        |

| ASSH Adaptive Synchronized Switch Harvesting.        |

| В                                                    |

| BBM Break-Before-Make.                               |

| BICMOS Bipolar CMOS.                                 |

| <b>BJT</b> Bipolar Junction Transistor.              |

| BR Bulk Regulation.                                  |

| C                                                    |

| <b>cmos</b> Complementary Metal-Oxide-Semiconductor. |

| <b>CPU</b> Central Processing Unit.                  |

| D                                                    |

| <b>DC</b> Direct Current.                            |

| <b>DRC</b> Design Rule Check.                        |

| <b>DSSH</b> Double Synchronized Switch Harvesting.   |

**DTMOS** Dynamic Threshold Voltage MOSFET.

| EDA | Electronic | Design | Automation. |

|-----|------------|--------|-------------|

|-----|------------|--------|-------------|

- **ESD** Electrostatic Discharge.

- **ESSH** Enhanced Synchronized Switch Harvesting.

- EU European Union.

- **EVC** External  $V_{th}$  Cancellation.

F

FET Field Efect Transistor.

G

**GBW** Gain Bandwidth.

I

```

Ic Integrated Circuit.

```

- **ID** Input and Output.

- **IVC** Internal  $V_{th}$  Cancellation.

J

```

JFET Junction gate Field-Effect Transistor.

```

L

Lvs Layout Versus Schematic.

Μ

- мвв Make-Before-Break.

- **MBPD** MOSFET Bypass PMOS Diode.

- **MEMS** Microelectromechanical Systems.

- MIM Metal-Insulator-Metal.

- **mos** Metal-Oxide-Semiconductor.

- **MOSFET** Metal-Oxide-Semiconductor Field-Effect Transistor.

- MR-SSHI Synchronized Switch Harvesting on Inductor using Magnetic Rectifier.

- Ν

- NVC Negative Voltage Converter.

- 0

- **OP-AMP** Operational Amplifier.

- Р

- P-SSHI Parallel Synchronized Switch Harvesting on Inductor.

- PCE Power Conversion Efficiency.

- PEG Piezoelectric Electrical Generator.

- **PS-SECE** Phase Shift Synchronous Electric Charge Extraction.

- **PSRR** Power Supply Rejection Ratio.

- PWL Piecewise Linear.

#### R

- **R&D** Research and Development.

- **RF** Radio-Frequency.

#### S

s-sshi Series Synchronized Switch Harvesting on Inductor.

- **SECE** Synchronous Electric Charge Extraction.

- **SMPS** Switch Mode Power Supply.

- **SPICE** Simulation Program with Integrated Circuit Emphasis.

- **ssp** Synchronized Switch Damping.

- **sspci** Synchronized Switching and Discharging to a storage Capacitor through an Inductor.

- **SSHI** Synchronized Switch Harvesting on Inductor.

- **svc** Self- $V_{th}$  Cancellation.

## U

- Ultra-Low Power.

- w

- wsn Wireless Sensor Nodes.

# INTRODUCTION

The increasing demands for powering electronic devices, such as wearable, wireless sensor networks, biomedical implants, and so forth, have led to the current extensive exploration of power harvesting devices. The goal of electronic energy harvesting interfaces is to efficiently manage the scavenged energy to enable battery-free, lowmaintenance and more eco-friendly devices, consequently allowing for more portable and lightweight electronic devices.

#### 1.1 Motivation and Applications

Microsensor networks have an energy constraint on the sensor nodes imposed by the capacity of the nodes' battery. In order to extend the sensor lifetime, most microsensors work through a duty cycle, alternating between an active and a sleep mode, and shutdown unused components whenever possible. However, this does not remove the energy constraint by the battery.

For some applications, a pure Lithium battery of  $1 cm^3$ , capable of continuously supplying  $1 \mu W$  for five years, is enough (Calhoun et al., 2005). Nonetheless, nowadays batteries are a handicap for higher peak power and extended lifespan applications due to their low energy density and high costs (Bawa and Ghovanloo, 2008), raising maintenance, complexity, and recycling issues (Guyomar, 2011). In some situations, it is impractical or even impossible to change batteries. Therefore, a new approach to solve this problem involves using energy from the environment to supply devices, overcoming the previous issue, and making them self-powered and self-sufficient (Guyomar, 2011).

The recent increase of autonomous and efficient devices encouraged by industrial fields and personal applications has raised powering issues (Guyomar, 2011). There is a need for reduced power consumption, depending on the kind of use, e.g. low power sensors consumption is around  $10 \,\mu W$  to  $100 \,\mu W$ . Energy harvesting has become a significant research and development topic. This technology has a massive impact on people's life since it extends its applications in many fields, such as aeronautics, transports, civil engineering, biomedical engineer, Radio-Frequency (RF), home automation, nomad devices, and so on (Dai et al., 2015; Guyomar, 2011). Its impact on the deployment of WSN and wearable electronic devices is crucial (Dai et al., 2015), allowing the information collected from the systems to be transferred to the outside world in real-time (Bawa and Ghovanloo, 2008). Theoretically, those devices can have an infinite lifespan, being only limited by the lifetimes of their components.

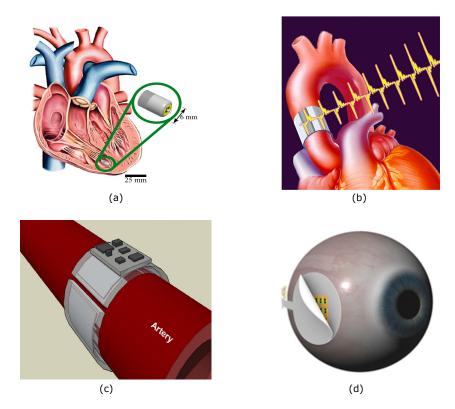

Regarding the innovations above, the biomedical field benefits extensively from this technology progress through implantable sensors (Deterre et al., 2013), sending data from inside the human body (Peters et al., 2007) and allowing monitoring patient's health anywhere in real-time (Wong et al., 2016). Through these developments, patients can have a comfortable lifestyle, thanks to the freedom of movements due to wireless devices. Contrary to previous methods, which need for invasive procedures to replace batteries, these innovations reduce infection risk. Besides, they do not cause any discomfort or health risks to the patients (Peters et al., 2007). In this domain, the applications are widely explored, enabling the detection and treatment of diseases such as muscle paralysis and deafness (Cha et al., 2012). It can also be used to measure the physiological signals as heartbeat or blood flow sensing. Furthermore, it can record neuronal activity in patients with Parkinson or retinal prosthesis (Vakili and Golmakani, 2013). Figure 1 shows some of the aforementioned applications.

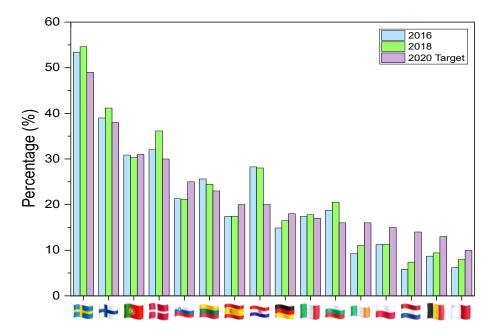

The implementation of these technologies has notably prompted a shift in the design approach of electronic systems, introducing new challenges for system designers. It is expected that by 2024, the global market of devices powered by ambient energy accomplish a total of 2.6 billion units (Chetto and Queudet, 2016). The European Commission presented the European Green Deal, the most ambitious package of measures aiming to become the world's first climate-neutral continent by 2050. That should enable European citizens and businesses to benefit from sustainable green transition (European Commission, 2019). A recent statistic on renewable energy sources in the European Union (EU) is given in Figure 2 (Eurostat Statistic Explained, 2020). It can be observed that the majority of countries increased the percentage of renewable sources from 2016 to 2018. For this year, 2020, most of the countries already achieve the expected goals in 2018, like Norway and Germany. Therefore, Europe is rapidly developing for a more sustainable continent.

Figure 1: Biomedical applications requiring energy harvesting: (a) intra-cardiac implant placed in the heart cavity scavenging energy from regular blood pressure (Deterre et al., 2013); (b) a polyvinylidene fluoride harvester that extract energy from the arterial wall deformation (Yang et al., 2018); (c) implanted arterial cuff power source integrated into a self-powered blood pressure sensing system (Potkay and Brooks, 2008) and (d) flexible retinal implant device (Hwang et al., 2015).

# 1.2 Energy Harvesting

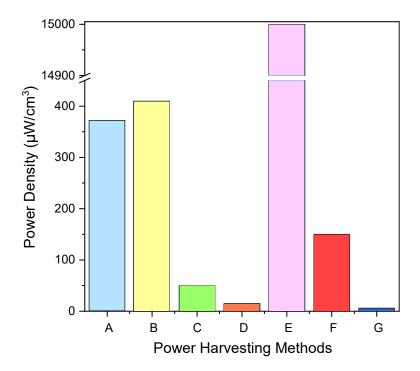

Energy harvesting has long been known as the process of scavenging energy available from the surrounding environment and converts it into electrical energy. Several types of sources can be used to harvest energy (Ali et al., 2014), and those are divided into two groups according to their characteristics (Dang et al., 2012). Firstly, the natural sources that are available directly from the environment, such as RF, solar power, thermal gradients, in particular geothermal heat, and mechanical vibration (Maiorca et al., 2013). Secondly, the artificial sources that are not generated by nature and result from human or system activities, such as body motion, breathing, blood pressure, and system vibration during their operational mode (Priya, 2007). A comparison of power densities from some energy harvesting mechanisms for a 10-year lifetime is given in Figure 3 (Roundy et al., 2003; Roundy et al., 2005; Cao et al., 2007). The highest power density comes from solar cells in direct sunlight - Figure 3(E). However, the best conditions for extracting solar energy are not available whenever (night) and everywhere because of climate changes. In areas with cloudy weather, Figure 3(F), where the light is not maximum, or even at

Figure 2: Overall share of energy from renewable sources in some the European Union member states (Eurostat Statistic Explained, 2020).

an indoor environment, Figure 3(G), as dim offices, the power density decreases drastically from  $15000 \ \mu W/cm^3$  to  $6 \ \mu W/cm^3$ . Thermoelectric sources, Figure 3(D), scavenge power from thermal gradients with  $15 \ \mu W/cm^3$  at a  $10 \ ^{\circ}C$  gradient. Nonetheless, since there are sources more accessible to harvesting energy and with higher values, this method is considered inadequate.

Nevertheless, the implemented energy transducer depends on the available ambient energy to harvest. Therefore, Table 1 displays the correlation between the different ambient sources and what kind of transducer should be employed (Mateu et al., 2014).

| Table 1: Transducers for different ambient energy sources. |                                               |  |

|------------------------------------------------------------|-----------------------------------------------|--|

| Ambient Energy Source                                      | Transducer                                    |  |

| Light                                                      | Photovoltaic cell                             |  |

| Mechanical                                                 | Piezoelectric, electromagnetic, electrostatic |  |

| Thermal                                                    | Thermoelectric generator                      |  |

Among the numerous sources, mechanical vibration energy is commonly explored since it is available in small-scale systems (Guyomar, 2011; Maiorca et al., 2013). Common day activities, such as walking produces energy with a power density of  $850 \,\mu W$ , through mechanical vibrations, by applying a force of  $2500 \,N$  on a knee (Seunghyun, 2013). The best-known methods of transduction technologies for this source are piezoelectric,

Figure 3: Comparison of energy sources with a fixed level of power generation (Roundy et al., 2003; Roundy et al., 2005; Cao et al., 2007). (A), (B) and (C) are vibration piezoelectric, electromagnetic and electrostatic, respectively; (D) is a thermoelectric source; (E), (F) and (G) are solar energy directly from sunlight on a clear weather day, on a cloudy day and indoor, correspondingly.

electromagnetic, or electrostatic (Figure 3). Those are coupled to the extraction structure to convert vibrations into electrical energy (Maiorca et al., 2013).

In Figure 3(C), with  $50 \ \mu W/cm^3$ , is the electrostatic generation. Its operation consists of two conductors moving in relation to each other, separated by a dielectric. When the conductors move, the energy stored changes and the mechanical energy is converted into electrical energy (Roundy et al., 2003). These converters, combined with Microelectromechanical Systems (MEMS) processing technology, offer an effective method to obtain close integration with electronics and the potential to scale down to smaller sizes. These advantages are more significant for electrostatic converters than for the others. Nevertheless, the requirements of a separate voltage source to initiate the conversion process and the difficulties in their implementation constitute drawbacks for this transducer (S.P. Beepy, 2006).

The transducers represented by Figure 3(B) are ruled by the principle of electromagnetic induction defined by Faraday's law (Singh, 2011). A magnetic flux variation is created due to relative motion between a magnet and a coil, inducing an electromotive force across the coils. The corresponding energy to the motion damped is transduced into electrical energy (Kiziroglou and Yeatman, 2012). Although the energy is usually implemented for rotational movement, in energy harvesting sources, the free motion does not often come from rotational. In literature, no inherent advantage is pointed to electromagnetic transducers over the other converters (Roundy et al., 2003).

# 1.3 Piezoelectric Transducer

Despite all the transducers above mentioned, this thesis project focuses on piezoelectric materials. A piezoelectric crystal suffers a charge separation due to a mechanical strain in the dielectric material, that is converted into electrical energy associated with the presence of electric charges. Thus, mechanical stress produces a voltage in the piezoelectric element (Roundy et al., 2003).

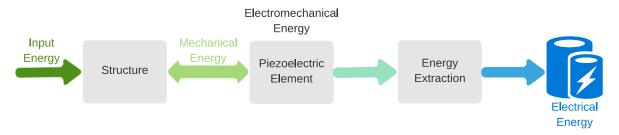

Generally, Figure 4 describes a vibration energy harvester. There is a special interest in piezoelectric elements thanks to their high energy densities and potential integration (Guyomar, 2011), exhibiting better performance than others (Maiorca et al., 2013). Even though they are more difficult to integrate into a microfabrication process than the other technologies, a recently study (Roundy et al., 2003) proves it is possible to integrate a piezoelectric transducer into a MEMS package. In this way, it becomes the premium option for the design of miniaturized and self-power devices (Guyomar, 2011). The efficiency of the conversion process from vibration into electric energy depends on the method of applying the oscillating stress onto the piezoelectric and material parameters (Priya, 2007).

Figure 4: General schematic of a vibration piezoelectric energy harvester.

The equations (1) and (2) describe the mechanical and electrical behaviour of piezoelectric materials (Roundy et al., 2003). Assuming that  $\delta$  is the mechanical strain,  $\sigma$  the mechanical stress, Y is the Young's modulus, also known as elastic modulus, used to describe stiffness of materials, D the electrical displacement, which is the charge density, E the electric field,  $\varepsilon$  the dielectric constant, and d the piezoelectric strain coefficient.

$$\delta = \frac{\sigma}{Y} + d \cdot E \tag{1}$$

$$D = \varepsilon \cdot E + d \cdot \sigma \tag{2}$$

An analytic model can be created associating the Euler–Bernoulli beam theory (Bauchau and Craig, 2009) and equations (1) and (2). Figure 5 shows an equivalent circuit of a basic configuration, where the output from the piezoelectric bender uses a resistive load ( $R_L$ ) as termination and the piezoelectric element is modeled as an Alternating Current (AC) voltage ( $V_S$ ) in series with a capacitor (C) and a resistor ( $R_S$ ).

Figure 5: Equivalent circuit for a piezoelectric generator.

The energy generated by Piezoelectric Electrical Generators (PEGs) is unappropriated to directly power most of the electronic systems since it limits the power from tens of microwatts to a few milliwatts (Sodano et al., 2005). Most researchers came across this problem; thus, new methods to accumulate the generated energy are needed (Sodano et al., 2005). In order to address this issue, it is proposed the use of intrinsic mechanical nonlinearities that aims to increase the input energy in the host structure to provide more power. Beyond the type of approach, nonlinear electronic interfaces have been suggested to increase the conversion capabilities of piezo elements and extract a significant amount of energy (Guyomar, 2011).

## 1.4 Project Implementation

In a real-world application, the mechanical force applied to the piezoelectric crystals changes over time, resulting in changes in amplitude and frequency of the signal, and output impedance variations. A highly optimized control circuit is desirable to scavenge these power fluctuations from the different surrounding conditions. The main problem with using these energy sources is the difference between the power generated and the power consumed. Technology developments have allowed this discrepancy to decrease, although a breakthrough is needed for an effective solution to be achieved. If the design of the piezoelectric element takes into account the typical vibration frequency of the application, the energy that is given by the transducers can be improved. Since the power output from a piezoelectric material is directly proportional to the vibrating frequency until the energy produced is optimal. This occurs when the natural frequency of the piezoelectric crystals matches the environment's vibrating frequency. Nonetheless, the development of these frequency-specific devices is costly and inconvenient, considering a new design had to be produced for each application. Thereby the power generated by the energy harvester is mostly enhanced in the power management circuit.

Another way to improve the power output is to create more efficient conversion circuits. The efficiency of these circuits is measured by a ratio between transducer energy and energy production of the final user device. Micro energy harvesters, which scavenged power is less than  $0.1 \,\mu W$ , requires an optimized power management circuit that effectively converts and stores this power. To reach the optimal efficiency point, research must be done involving electronic circuits and methods to be employed on the desirable system.

The power management circuit of an energy harvester extracts the energy generated by the transducer element, converts it into usable electric signal for a specific application, and conveys it to the requesting devices. Thus, the AC voltage must be converted to a Direct Current (DC) voltage, typically by a rectifier for energy storage and power systems (Peters et al., 2007; Sun et al., 2016). Thence a rectifier should be capable of handling low input amplitude and high sensitivity, along with low power consumption to achieve high efficiency (Wong et al., 2016).

Several research was conducted in the past few years, revealing that the main requirements for the extraction circuits for piezoelectric energy harvesters are efficiency and autonomous operation. The circuit should operate at very low power consumption, as the transducer's energy is already extremely low. As such, the circuit efficiency is of the utmost importance.

On the final application, the harvesting circuit should operate independently from the other devices. Due to this, the energy harvester can work without the aid of external sources, ensuring the electronic device is powered as needed. It is also crucial the circuit adaptation to environmental changes, to maximize efficiency. Besides being an attempt to match the transducer's excitation frequency, the circuit should be prepared for sudden amplitude changes in the oscillation.

The main goal of this study is to design and simulate an Integrated Circuit (IC) to efficiently scavenge energy from a random low power input signal generated by a vibrating piezoelectric transducer. Furthermore, implemen-

tation of custom components taking into account the CMOS technology advantages to their maximum capability is also a requirement. The fabrication of CMOS devices can have different process sizes, in particular, for this project, it was chosen the  $0.13 \,\mu m$  CMOS process. This process size was chosen to shrink the design size yet remaining affordable, and keeping the leakage current low. Moreover, the reduction of parasitic capacitance and lower core voltage means the transistors can be driven by a lower voltage, which is suitable for application in diverse fields.

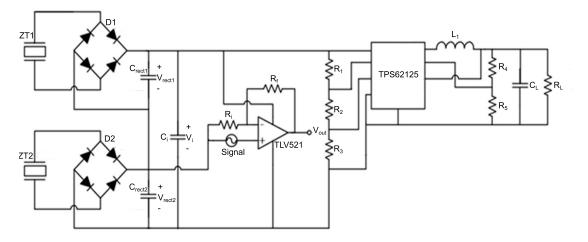

The harvesting architecture is based on an automatic frequency up-conversion technique (Li et al., 2014). It is designed to match the output impedance of the piezoelectric transducer dynamically by shifting the vibrational frequency of the piezoelectric element up to the resonant frequency of the harvesting interface. Thereby, an analog switch and a voltage amplifier are added to the circuit.

## 1.5 Thesis Organization

The present chapter introduces the concept of energy harvesting systems coming up until the concept of a piezoelectric transducer, also referring to the motivation and objectives of this dissertation. The necessary knowledge basis was acquired through a literature study in the preliminary work is presented in chapter 2, which addresses piezoelectric energy harvesters, electronic design and optimization, power management circuitry, and CMOS design/fabrication. Regarding the practical knowledge and requirements, those are supplied by the CMOS foundry partner. This chapter also explores in detail the background of the circuit of interest.

The main goal of the present study is to develop, design and simulate an IC, which includes a pre-voltage amplifier, an analog switch, and a rectifier. Those are designed according to the requested parameters by the extraction circuit with a very low power consumption. In chapter 3, an analysis of the system is done to compare topologies and to find the flaws in the circuits. It starts by modelling the system in manageable blocks and proceeding with the simulation of those blocks. The simulation results of each topology are followed by a comparison with previous works or off-the-shelf components. An iterative optimization is used to find the best topology for the use case, by maximizing the power efficiency of the circuit. Additionally, chapter 3 describes the project fabrication process.

In chapter 4 is presented the conclusion, along with some ideas that can become future target research. In addition, chapter A includes more detail regarding the CMOS fabrication, in conjunction with photos of the designs, layouts and chip. Beyond this, some of the outputs from this thesis are two articles, "A Low-power Two-Stage

Active Rectifier for Energy Harvesting Applications" and "A CMOS Low-power Two-Stage Active Rectifier for Energy Harvesting Applications", that are annexed to this document in chapter **??**.

# STATE OF THE ART

In this chapter, for a more complete knowledge of what is done is imperative to understand the background of the critical components: switch, amplifier and rectifier. Thus, an exhaustive and detailed review is given in this chapter.

# 2.1 Analog Switch

Numerous harvesting interfaces have been proposed in the literature to maximize the energy extraction derived from mechanical vibrations. Switched magnetic elements, as inductors or transformers, are used in rectification stages to partially match the reactive component of the piezoelectric impedance, causing a resonance effect.

Piezoelectric rectifiers use switched magnetic components to reduce the size of inductors and transducers and efficiently extract vibrational energy. This allows scavenging energy from a wide range of frequencies caused by the use of autonomous switch techniques monitoring the surrounding conditions.

The switch-mode transformers, also known as Switch Mode Power Supply (SMPS) transformers, use a regulated power supply to step up or step down voltage or current. Besides, they are capable of providing isolation between the input and output. Their goal is to deliver a constant output voltage over varying load conditions.

According to Guyomar (2011), there are two approaches, whether the piezoelectric element is directly connected to the switched magnetic components, or just after the rectifier. The operation principles are identical: both aim to enhance the conversion by increasing the voltage and decreasing the time shift between the voltage and the velocity. A nonlinear approach reduces time shift and increase voltage.

#### 2.1.1 Direct Energy Transfer

#### Standard Energy Harvesting Interface

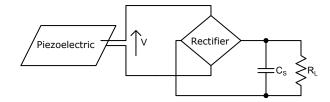

The standard interface of an energy harvesting is depicted in Figure 6, consisting of a merely direct connection between the piezoelectric material and the storage stage through a rectifier bridge.

Figure 6: Circuit schematic of the standard energy harvesting interface.

The energy from the piezoelectric flows to charge the storage capacitor ( $C_s$ ) anytime the absolute value of the piezo voltage (V) is higher than the rectified voltage (Lallart et al., 2011). On the contrary, when the absolute value of the piezoelectric material voltage is less than the output voltage of the rectifier, the piezoelectric element is let in open circuit, and the rectifier is blocked (Garbuio et al., 2009). Nonetheless, regarding the amount of energy that can be harvested, there is an upper limit due to the vibrational amplitude of the structure that determines the maximum piezoelectric voltage (Makihara and Asahina, 2017).

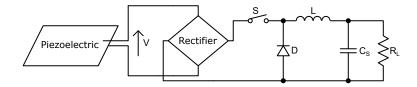

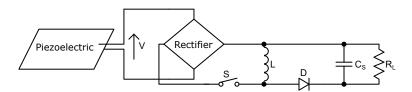

#### Parallel and Series Synchronized Switch Harvesting on Inductor

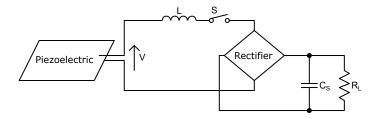

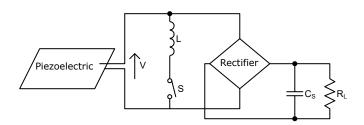

Series Synchronized Switch Harvesting on Inductor (S-SSHI) and Parallel Synchronized Switch Harvesting on Inductor (P-SSHI) are the first and simplest two resonant rectifiers proposed (Badel et al., 2006). The switch and the inductor, S and L, respectively, are directly connected in series, Figure 7, or in parallel, Figure 8, to the piezoelectric element. These techniques aim at artificially increasing the conversion capabilities of the piezoelectric element (Lefeuvre et al., 2006).

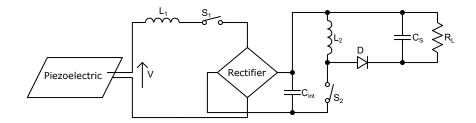

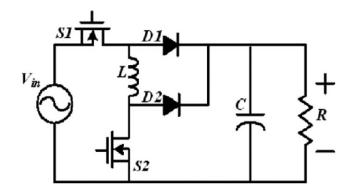

Figure 7: Circuit schematic of the S-SSHI rectifier.

Figure 8: Circuit schematic of the P-SSHI rectifier.

In both structures, the switch S is closed when the voltage generated by the piezoelectric transducer (V) reaches an extremum. In other words, the switch closes at the maximum and minimum of the mass displacement, and is kept close until a full voltage inversion on the piezoelectric transducer is achieved. The voltage inversion occurs if the switching period ( $t_i$ ) corresponds to half of the pseudo-period of the electrical resonant circuit (Equation 3) shaped by the capacitance of the piezoelectric ( $C_0$ ) and the inductor (Garbuio et al., 2009).

$$t_i = \pi \cdot \sqrt{L \cdot C_0} \tag{3}$$

However, this inversion is not perfect as a result of the internal inductor losses, and it is characterized by the inversion coefficient  $\gamma$  defined by Lallart et al. (2011) as:

$$\gamma \approx e^{\frac{-2\cdot\pi}{Q_i}},\tag{4}$$

assuming that  $Q_i$  is the electrical quality factor of the circuit.

A coil has an inductance (L) when the current flows through the coil and changes at a rate (di/dt) (Singh, 2011), inducting a voltage ( $V_L$ ) expressed according to Equation 5.

$$V_L = -L \cdot \frac{di}{dt} \tag{5}$$

The relationship between self-inductance and the number of turns (N) for a single coil can be given as:

$$L = N \cdot \frac{\Phi}{I},\tag{6}$$

admitting that  $\Phi$  is the magnetic flux and I the current. The coefficient of self-inductance also depends on design features, such as length, number of turns, and size. Therefore, for a coil, the magnetic flux produced in its inner core is equal to:

$$\Phi = B \cdot A,\tag{7}$$

where B is the flux density, and A is the cross-section area. The magnetic induction of a long solenoid coil with N number of turns per meter length in the inner core is given as (Singh, 2011):

$$B = \mu \cdot \frac{N \cdot I}{I},\tag{8}$$

where  $\mu$  is the permeability of the core material and I is the length of the coil, according to Faraday's Law, any change in the magnetic flux linkage produces a self-induced voltage in a single-coil as described in Equation 9 (Wadhwa, 2005).

$$V_L = N \cdot \frac{d\Phi}{dt} = \frac{\mu \cdot N^2 \cdot A}{1} \cdot \frac{di}{dt}$$

(9)

The operation principles of the interfaces are slightly different. In the P-SSHI, after the extraction of energy, the voltage is inverted, albeit, in S-SSHI, these two processes happen simultaneously. The Synchronized Switch Damping (SSD) is the effect of the voltage inversion, affecting the overall conversion efficiency, due to an electrical attenuation that opposes the mechanical vibration on the piezoelectric material. This is the main problem of both interfaces (Badel et al., 2006).

#### Synchronized Switch Harvesting on Inductor using Magnetic Rectifier

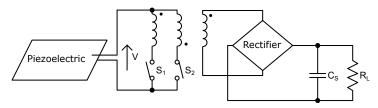

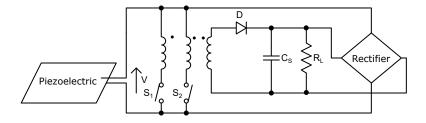

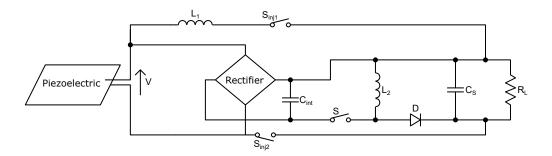

Synchronized Switch Harvesting on Inductor (SSHI) can also be achieved by replacing the switching inductor by a transformer, as exhibited in Figure 9, and it is called Synchronized Switch Harvesting on Inductor using Magnetic Rectifier (MR-SSHI).

Figure 9: Circuit diagram of the MR-SSHI.

The transformer has two primary windings in series with unidirectional switches,  $S_1$  and  $S_2$ , and one secondary winding connected to the rectifier (Garbuio et al., 2009). The two primary coils are connected with inverse polarity, to guarantee the secondary side has a proper charge flow for energy extraction. When the voltage on

the piezoelectric transducer is at its maximum, the switch  $S_1$  conducts (Lallart et al., 2011). Oppositely, the switch  $S_2$  leads when the transducer voltage is at its minimum. Thereby the electrical energy flowing through the transformer is converted into magnetic energy. Owing the secondary windings, this energy is converted back to electrical energy and finally stored on the storage capacitor ( $C_S$ ) and the load resistor ( $R_L$ ) (Lallart et al., 2011).

The set-up transformer allows an artificial change in the load seen by the piezoelectric element, since the coupling factor is chosen to be higher than 1, which increases the transducer voltage. Therefore, this technique is suitable to extract energy from reduced input power levels (Guyomar, 2011).

Hybrid Synchronized Switch Harvesting on Inductor