**Universidade do Minho** Escola de Engenharia

Ivo da Cruz Marques

A Loosely-Coupled Arm and RISC-V Locksteping Technology

**Universidade do Minho** Escola de Engenharia

Ivo da Cruz Marques

## A Loosely-Coupled Arm and RISC-V Locksteping Technology

Dissertação de Mestrado Mestrado em Engenharia Eletrónica Industrial e Computadores Sistemas Embebidos e Computadores

Trabalho efetuado sob a orientação do **Professor Doutor Adriano José Conceição Tavares**

### DIREITOS DE AUTOR E CONDIÇÕES DE UTILIZAÇÃO DO TRABALHO POR TERCEIROS

Este é um trabalho académico que pode ser utilizado por terceiros desde que respeitadas as regras e boas práticas internacionalmente aceites, no que concerne aos direitos de autor e direitos conexos.

Assim, o presente trabalho pode ser utilizado nos termos previstos na licença abaixo indicada. Caso o utilizador necessite de permissão para poder fazer um uso do trabalho em condições não previstas no licenciamento indicado, deverá contactar o autor, através do RepositóriUM da Universidade do Minho.

Atribuição-NãoComercial-Compartilhalgual CC BY-NC-SA

https://creativecommons.org/licenses/by-nc-sa/4.0/

## Agradecimentos

Primeiramente, gostaria de agradecer ao meu orientador, professor doutor Adriano Tavares, pela dedicação e disponibilidade quando mais foi preciso, assim como todo o conhecimento que partilhou ao longo do meu percurso académico. Também não poderia deixar de agradecer aos professores doutores Sandro Pinto e Tiago Gomes, pelo apoio e orientação ao longo desta dissertação.

Aos meus colegas de laboratório, que me acompanharam nesta jornada e proporcionaram momentos de trabalho assim como de pausas formidáveis. Aos meus amigos mais próximos, que estiveram presentes em vários momentos e foram fulcrais para realizar este percurso, principalmente aos meus amigos Cristiano, Daniel, José Pedro, José Nuno e Valter. E um especial obrigado para a Catarina, por me acompanhar, ajudar e apoiar.

Não podia deixar de agradecer à minha família, aos meus irmãos, aos meus pais e aos meus avós, por sempre me darem apoio, assim como todos os esforços que fazem por mim. Por último, deixo aqui um especial e carinhoso obrigado à minha avó Rosa, por todo o suporte e palavras amigas em momentos de mais aflição. Um grande obrigado a toda a minha família pelo amor, alegria e atenção.

A todas as pessoas que contribuíram para este percurso, um forte obrigado.

#### **STATEMENT OF INTEGRITY**

I hereby declare having conducted this academic work with integrity. I confirm that I have not used plagiarism or any form of undue use of information or falsification of results along the process leading to its elaboration. I further declare that I have fully acknowledged the Code of Ethical Conduct of the University of Minho.

## Resumo

# Tecnologia *Lockstep* em processadores Arm e RISC-V recorrendo a uma abordagem *loose-ly-coupled*

Nos últimos anos, o grande crescimento tecnológico tem originado o surgimento de novas necessidades, onde dispositivos eletrónicos e seres humanos passam a ter um maior contacto. Este crescimento, contudo, levanta problemas de fiabilidade e segurança. E apesar de na ciência computacional surgirem melhorias de desempenho e de eficiência energética, devido à redução dos transístores, altas frequências de relógio, e baixas tensões de execução do núcleo de processamento, estas trazem consigo lacunas na fiabilidade dos sistemas, tornando-os mas suscetíveis a faltas. Por exemplo, esta nova geração tecnológica é cada vez mais sensível a radiações que podem despoletar *Single Event Upset (SEU)*.

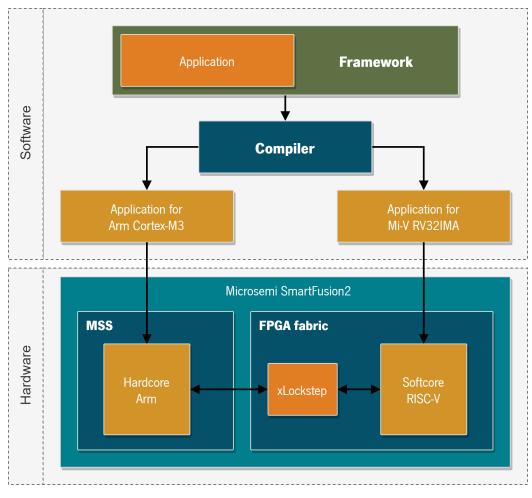

Esta dissertação visa fornecer uma nova solução para sistemas tolerantes a falhas, denominada de Lock-V, que combina duas técnicas, de forma a responder à lacuna atual. A solução foi implementada sobre a Microsemi SmartFusion2 que inclui um microcontrolador e um *Field-Programmable Gate Array (FPGA)* na mesma plataforma, esta solução consiste numa arquitetura *Dual-Core Lockstep (DCLS)* combinada com diversidade de desenho ao nível do conjunto de instruções que é obtida pelo uso de dois núcleos diferentes, um *hard-core* Arm Cortex-M3 e um *soft-core* com base em RICS-V. O DCLS é apoiado por um acelerador desenvolvido na FPGA e proporciona ao sistema a capacidade de deteção de error, através da comparação *loosely-coupled* das saídas dos núcleos de processamento. Para além disso, esta dissertação fornece uma *framework*, que adiciona ao sistema a capacidade de auto-recuperação.

De forma a validar o sistema, foi desenvolvido um mecanismo de injeção de faltas, que testa a arquitetura Lock-V. Como proteger a memoria está fora do âmbito desta dissertação, e como tal, a injeção de faltas foi aplicada apenas nos registros do processador, que normalmente são os mais vulneráveis a faltas se excluirmos as memórias. Estes testes, provam a eficiência do sistema Lock-V como um sistema tolerante a falhas. Para além disso, esta arquitetura, devido ao seu mecanismo *lockstep* é um sistema tolerante a falhas contra SEU, e também, devido à diversidade de desenho, apresenta proteção contra falhas de modo comum. Resumidamente, o sistema Lock-V tem grande cobertura de faltas tendo em conta as soluções existentes.

Palavras-chave: Diversidade de Desenho, DCLS, Redundância, Tolerância a Falhas.

## Abstract

#### A Loosely-Coupled Arm and RISC-V Locksteping Technology

Due to the technological growth during the last few years, a new market is rising, bringing a huge number of devices that interact with the human being and the environment. However, the dependability of those devices becomes more and more a concern. Furthermore, from what has been seen, in terms of performance and power consumption, these computational systems are constantly being improved due to reduced transistor's size, higher clock frequencies, and lower operating core voltages. However, this leads to a lack in the systems reliability, which turns them more susceptive to faults. For example, systems are becoming more sensitives to radiations that can trigger Single Event Upsets (SEUs) in this new technological generation.

This dissertation aims to provide a new solution for fault tolerance systems, named Lock-V, that combines two fault tolerance techniques, in order to answer the current gap. The solution is deployed under the Microsemi SmartFusion2 that includes a Microcontroller Unit (MCU) and an Field-Programmable Gate Array (FPGA) in the same platform, and the solution consists in a Dual-Core Lockstep (DCLS) combined with design diversity at Instruction Set Architecture (ISA) level. The design diversity is achieved by using two different cores, a hard-core Arm Cortex-M3 and a soft-core RISC-V-based processors. The DCLS is supported by an FPGA-based accelerator and it provides error detection capabilities to the system by comparing, in a loosely-coupled fashion, the outputs from the two cores. Moreover, this dissertation provides a friendly framework, that adds to the system recovery capabilities.

In order to validate the system, a fault injection mechanism was developed, to test the Lock-V architecture. Since protecting the memory is out of the scope of this dissertation, the fault injections are over the register files, which are usually more vulnerable to faults, excluding the memory. These tests, prove the effectiveness of the Lock-V system as a fault tolerance system. Moreover, Lock-V architecture offers fault tolerance against SEU and protection against Common-Mode Failure (CMF) by applying lockstep technique and design diversity, respectively. Summing up, the Lock-V achieved a high fault coverage taking into account the existing solutions.

Keywords: Design Diversity, DCLS, Redundancy, Fault Tolerance.

# Contents

| st of F | igures                                    |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| st of T | ables                                     |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ossar   | y                                         |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Intro   | oduction                                  | 1                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.1     | Motivat                                   | on                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.2     | Main G                                    | oal                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 1.2.1                                     | Objectives                                                                                                                                                                                                                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.3     | Disserta                                  | ation Structu                                                                                                                                                                                                                                      | ure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Bac     | kground                                   | and State                                                                                                                                                                                                                                          | e of the Art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.1     | Depend                                    | ability                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 2.1.1                                     | Dependab                                                                                                                                                                                                                                           | ility threats hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |                                           | 2.1.1.1                                                                                                                                                                                                                                            | Chain of dependability threats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |                                           | 2.1.1.2                                                                                                                                                                                                                                            | Fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |                                           | 2.1.1.3                                                                                                                                                                                                                                            | Cause of the faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |                                           | 2.1.1.4                                                                                                                                                                                                                                            | Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                           | 2.1.1.5                                                                                                                                                                                                                                            | Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 2.1.2                                     | Attributes                                                                                                                                                                                                                                         | of dependability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 2.1.3                                     | Means to a                                                                                                                                                                                                                                         | achieve dependability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.2     | Fault to                                  | lerance .                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 2.2.1                                     | Redundan                                                                                                                                                                                                                                           | юу                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 2.2.2                                     | Design div                                                                                                                                                                                                                                         | <i>r</i> ersity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 2.2.3                                     | Lockstep t                                                                                                                                                                                                                                         | technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                           | 2.2.3.1                                                                                                                                                                                                                                            | Error detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                           | 2.2.3.2                                                                                                                                                                                                                                            | System recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 2.2.4                                     | Fault tolera                                                                                                                                                                                                                                       | ance techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                           | 2.2.4.1                                                                                                                                                                                                                                            | Fault tolerance techniques overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | Intro<br>1.1<br>1.2<br>1.3<br>Back<br>2.1 | <ul> <li>1.1 Motivati</li> <li>1.2 Main Go</li> <li>1.2.1</li> <li>1.3 Disserta</li> <li>Background</li> <li>2.1 Depend</li> <li>2.1.1</li> <li>2.1.2</li> <li>2.1.3</li> <li>2.2 Fault to</li> <li>2.2.1</li> <li>2.2.2</li> <li>2.2.3</li> </ul> | St of Tables         Introduction         1.1       Motivation         1.2       Main Goal         1.3       Dissertation Structure         Background and State       2.1         2.1       Dependability         2.1.1       Dependability         2.1.1       2.1.1.1         2.1.1.2       2.1.1.3         2.1.1.4       2.1.1.5         2.1.2       Attributes         2.1.3       Means to         2.2       Fault tolerance         2.2.1       Redundan         2.2.2       Design div         2.2.3       Lockstep for         2.2.3.1       2.2.3.2         2.2.4       Fault toler | Introduction          1.1       Motivation         1.2       Main Goal         1.2.1       Objectives         1.3       Dissertation Structure         Background and State of the Art         2.1       Dependability         2.1.1       Chain of dependability threats         2.1.1       Chain of dependability threats         2.1.1.2       Fault         2.1.1.3       Cause of the faults         2.1.1.4       Error         2.1.2       Attributes of dependability         2.1.3       Means to achieve dependability         2.2.4       Fault tolerance         2.2.3       Lockstep technique         2.2.3.1       Error detection         2.2.3.2       System recovery         2.2.4       Fault tolerance techniques |

|   | 2.3  | Related    | work                                  | <br> | <br> | <br> |  | <br> | 27 |

|---|------|------------|---------------------------------------|------|------|------|--|------|----|

|   |      | 2.3.1      | Fault tolerance on memory             | <br> | <br> | <br> |  | <br> | 27 |

|   |      | 2.3.2      | Heterogeneous architecture            | <br> | <br> | <br> |  | <br> | 28 |

|   |      | 2.3.3      | Lockstep systems                      | <br> | <br> | <br> |  | <br> | 28 |

|   | 2.4  | Summa      | ry                                    | <br> | <br> | <br> |  | <br> | 30 |

| 3 | Plat | form and   | d tools                               |      |      |      |  |      | 32 |

|   | 3.1  | Reconfi    | gurable technology                    | <br> | <br> | <br> |  | <br> | 32 |

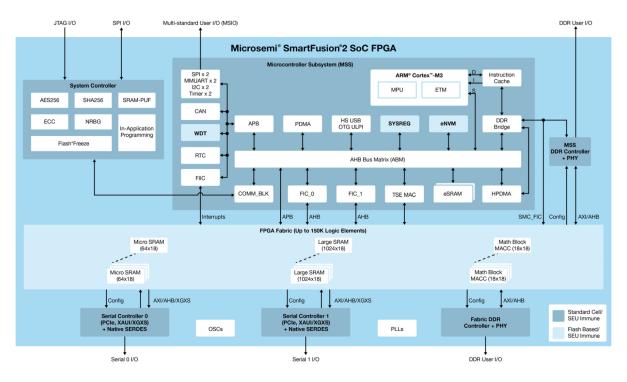

|   |      | 3.1.1      | Microsemi SmartFusion2                |      |      |      |  |      |    |

|   | 3.2  | RISC-V-I   | based soft-core solutions             | <br> | <br> | <br> |  | <br> | 34 |

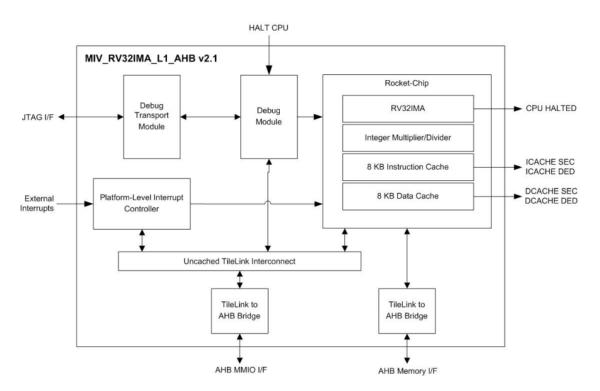

|   |      | 3.2.1      | Microsemi Mi-V                        | <br> | <br> | <br> |  | <br> | 35 |

|   | 3.3  | Summa      | ry                                    | <br> | <br> | <br> |  | <br> | 37 |

| 4 | Lock | -V Archi   | itecture                              |      |      |      |  |      | 38 |

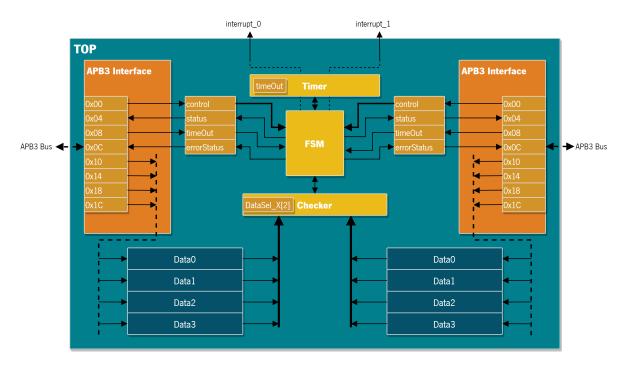

|   | 4.1  | xLockst    | <i>ep</i> architecture                | <br> | <br> | <br> |  | <br> | 39 |

|   |      | 4.1.1      | Finite State Machine Module           |      |      |      |  |      |    |

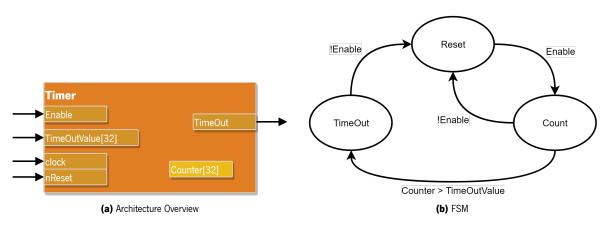

|   |      | 4.1.2      | <i>Timer</i> Module                   |      |      |      |  |      |    |

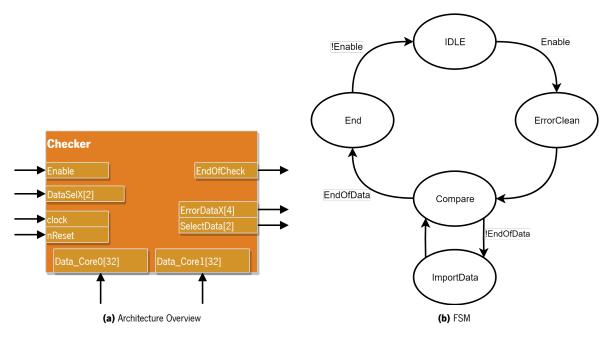

|   |      | 4.1.3      | Checker Module                        |      |      |      |  |      | 44 |

|   |      | 4.1.4      | APB3 Interface Module                 | <br> | <br> | <br> |  | <br> | 45 |

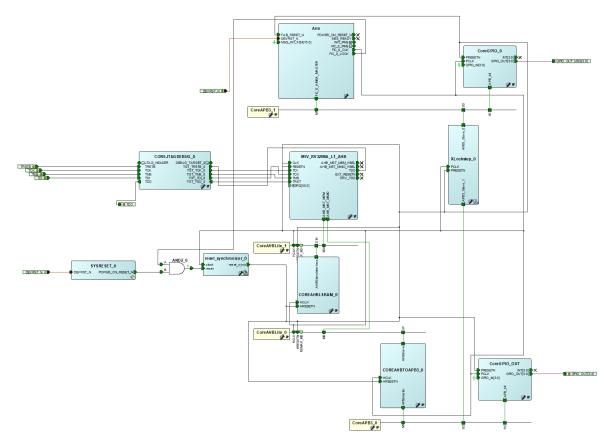

|   | 4.2  | Lock-V ł   | nardware                              | <br> | <br> | <br> |  | <br> | 46 |

|   | 4.3  | Lock-V /   | API                                   | <br> | <br> | <br> |  | <br> | 47 |

|   |      | 4.3.1      | Initialization                        | <br> | <br> | <br> |  | <br> | 48 |

|   |      | 4.3.2      | Synchronization                       | <br> | <br> | <br> |  | <br> | 48 |

|   |      | 4.3.3      | Comparison                            | <br> | <br> | <br> |  | <br> | 48 |

|   |      | 4.3.4      | Runtime duties                        | <br> | <br> | <br> |  | <br> | 49 |

|   |      | 4.3.5      | Configuration                         | <br> | <br> | <br> |  | <br> | 49 |

|   |      | 4.3.6      | Status information                    | <br> | <br> | <br> |  | <br> | 50 |

|   | 4.4  | Summa      | ry                                    | <br> | <br> | <br> |  | <br> | 50 |

| 5 | Lock | -V Fram    | ework                                 |      |      |      |  |      | 51 |

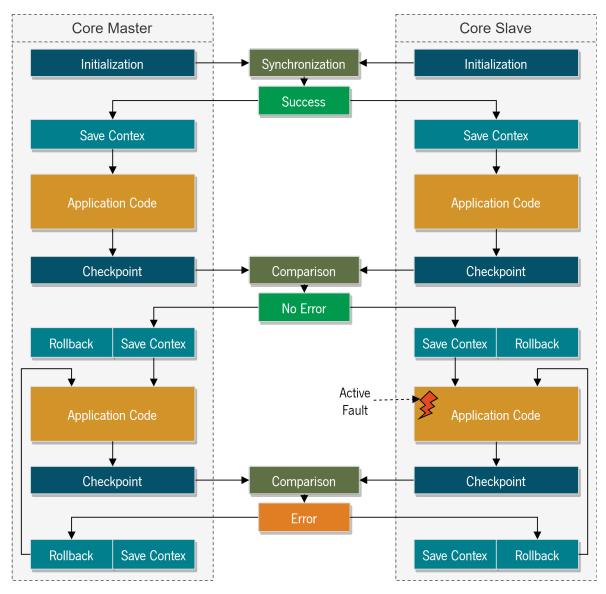

|   | 5.1  | Framew     | ork Overview                          | <br> | <br> | <br> |  | <br> | 51 |

|   | 5.2  | Initializa | tion                                  | <br> | <br> | <br> |  | <br> | 53 |

|   | 5.3  | Checkp     | oint                                  | <br> | <br> | <br> |  | <br> | 53 |

|   | 5.4  | Save Co    | ontext                                | <br> | <br> | <br> |  | <br> | 53 |

|   |      | 5.4.1      | Save Context Implementation           | <br> | <br> | <br> |  | <br> | 54 |

|   | 5.5  | Rollbacl   | · · · · · · · · · · · · · · · · · · · | <br> | <br> | <br> |  | <br> | 56 |

|   |      | 5.5.1      | ErrorFix Function                     | <br> | <br> | <br> |  | <br> | 56 |

|   | 5.6  | Summa      | ry                                    | <br> | <br> | <br> |  | <br> | 56 |

| 6  | Eval  | uation and Results                          | 58 |

|----|-------|---------------------------------------------|----|

|    | 6.1   | Lock-V Implementation Analysis              | 58 |

|    |       | 6.1.1 Fabric FPGA Resources Utilization     | 58 |

|    |       | 6.1.2 Memory Footprint                      | 60 |

|    |       | 6.1.3 Execution footprint                   | 60 |

|    |       | 6.1.3.1 System recovery execution footprint | 61 |

|    |       | 6.1.3.2 Error detection execution footprint | 61 |

|    | 6.2   | Fault Injection Case Study                  | 65 |

|    |       | 6.2.1 Results                               | 67 |

|    | 6.3   | Summary                                     | 67 |

| 7  | Con   | clusion                                     | 68 |

|    | 7.1   | Future Work                                 | 69 |

|    | 7.2   | Publications                                | 70 |

| Re | feren | ces                                         | 71 |

# **List of Figures**

| 2.1  | Dependability tree.                                                                    | 5  |

|------|----------------------------------------------------------------------------------------|----|

| 2.2  | Fault, error, and failure hierarchy.                                                   | 6  |

| 2.3  | Elementary fault classes and its eight different classifiers.                          | 7  |

| 2.4  | The classes of combined faults                                                         | 8  |

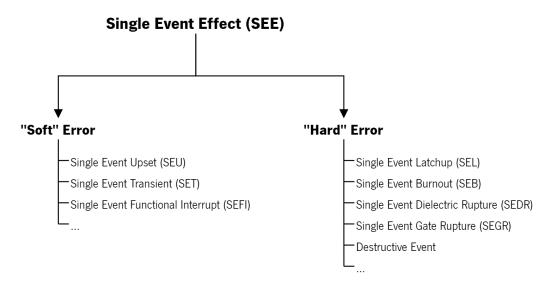

| 2.5  | Single event effect tree                                                               | 10 |

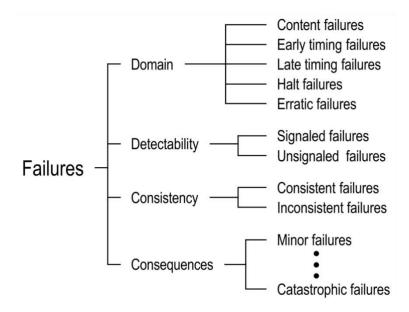

| 2.6  | Service failure modes.                                                                 | 11 |

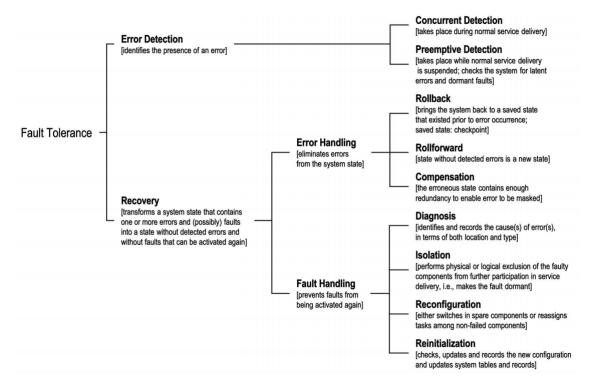

| 2.7  | Fault tolerance mechanisms.                                                            | 16 |

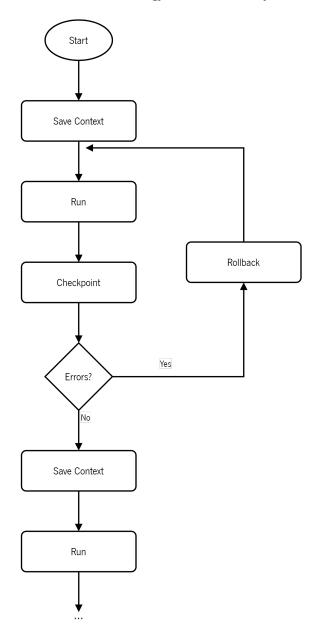

| 2.8  | Fault tolerance strategy, error detection with system rollback recovery                | 18 |

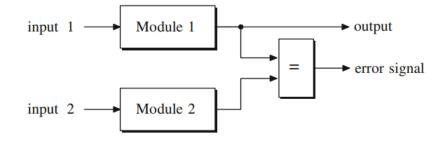

| 2.9  | Duplication with comparison.                                                           | 20 |

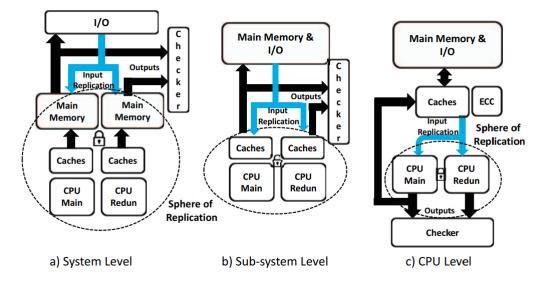

| 2.10 | Three types of lockstep in computer systems.                                           | 23 |

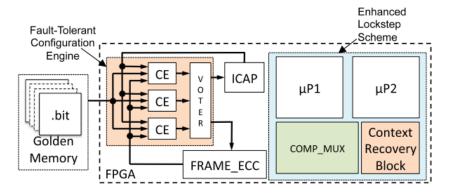

| 2.11 | Fault tolerance architecture for Field-Programmable Gate Array (FPGA) with soft-core   |    |

|      | Dual-Core Lockstep (DCLS) and Triple Modular Redundancy (TMR) in configuration engine. | 29 |

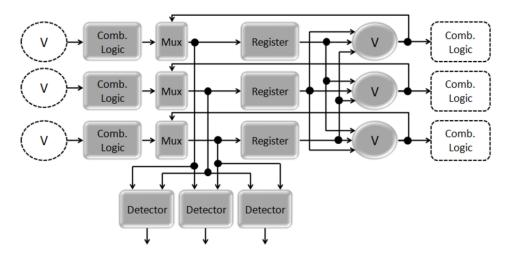

| 2.12 | Fault tolerance soft-core architecture for FPGA with triplication of all units.        | 29 |

| 3.1  | Microsemi SmartFusion2 SoC FPGA Block Diagram.                                         | 33 |

| 3.2  | -                                                                                      | 36 |

| 5.2  | MIV RV32IMA L1 AHB soft-core block diagram.                                            | 50 |

| 4.1  | Proposed DCLS architecture, Lock-V                                                     | 38 |

| 4.2  | <i>xLockstep</i> architecture overview                                                 | 39 |

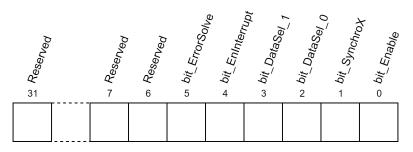

| 4.3  | Control Register.                                                                      | 40 |

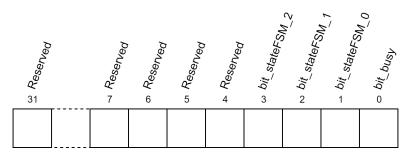

| 4.4  | Status Register                                                                        | 41 |

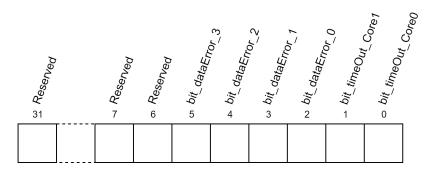

| 4.5  | Error Status Register.                                                                 | 41 |

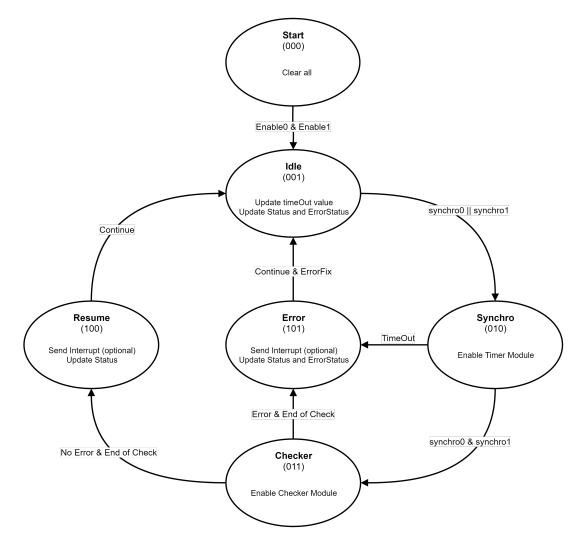

| 4.6  | Finite State Machine (FSM) to manage the <i>xLockstep</i> architecture                 | 42 |

| 4.7  | Architecture overview and FSM of the <i>Timer</i> module                               | 44 |

| 4.8  | Architecture overview and FSM of the <i>Checker</i> module                             | 45 |

| 4.9  | <i>xLockstep</i> memory-mapped address.                                                | 45 |

| 4.10 | <i>xLockstep</i> design on Microsemi SmartFusion2                                      | 46 |

| 5.1  | DCLS execution flow with rollback.                                                     | 52 |

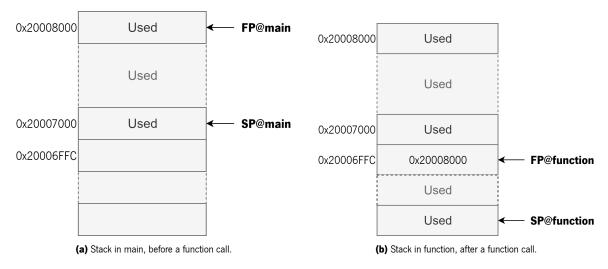

| 5.2 | Stack in Arm Cortex-M3 before and after a function call without arguments nested func-       |    |  |  |  |

|-----|----------------------------------------------------------------------------------------------|----|--|--|--|

|     | tions. The address are merely illustrative.                                                  | 55 |  |  |  |

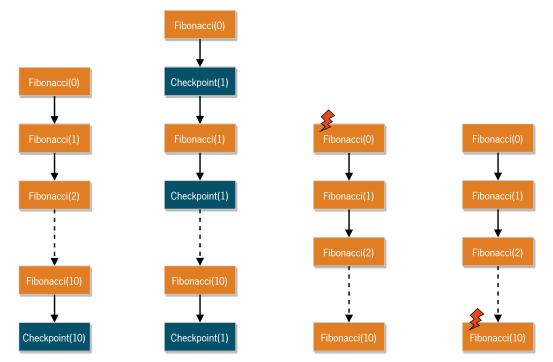

| 6.1 | Fibonacci sequence calculation with one (a) or $N$ (b) checkpoints. And <i>Fibonacci</i> se- |    |  |  |  |

|     | quence with error in the first (c) or in the last (d) element.                               | 64 |  |  |  |

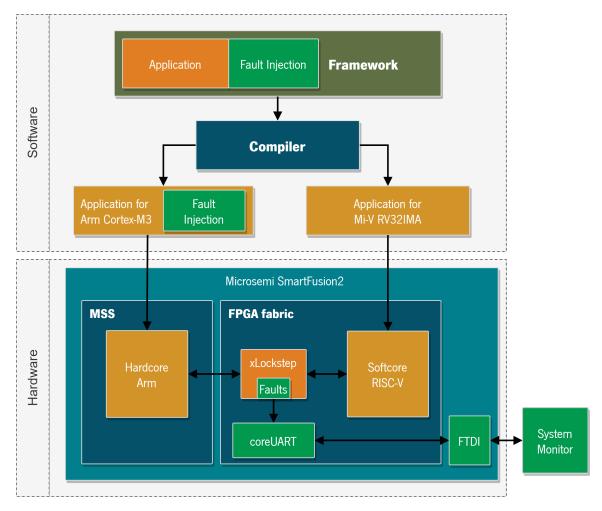

| 6.2 | Lock-V architecture with fault injection mechanism and monitor system.                       | 66 |  |  |  |

# **List of Tables**

| 2.1 | Availability of system classes and the corresponding downtime per year.                                     | 13 |

|-----|-------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Fault tolerance techniques overview                                                                         | 26 |

| 2.3 | Lockstep related work overview.                                                                             | 30 |

| 3.1 | List of RISC-V soft-core.                                                                                   | 35 |

| 4.1 | <i>bit_DataSel_X</i> selection according with number of data to compare                                     | 40 |

| 6.1 | Resource utilization of the <i>xLockstep</i> and the entire system described in section 4.2                 | 59 |

| 6.2 | Arm memory footprint (values in bytes)                                                                      | 60 |

| 6.3 | RISC-V memory footprint (values in bytes)                                                                   | 60 |

| 6.4 | <i>saveContext()</i> and <i>rollback()</i> execution footprint (the <i>main()</i> stack size was 4x4 bytes) | 61 |

| 6.5 | Checkpoint execution footprint without errors and with error in first element to compare.                   | 62 |

| 6.6 | Checkpoint execution footprint without errors and with error in last element to compare                     | 63 |

| 6.7 | Lock-V execution footprint with and without errors, using <i>Fibonacci</i> function                         | 65 |

| 6.8 | Fault injection results with and without Lock-V.                                                            | 67 |

# Glossary

4-LUT 4-Inputs Look-Up Table **ABI** Application Binary Interface AHB Advanced High-performance Bus AHB-Lite Advanced High-performance Bus Lite **AMBA** Advanced Microcontroller Bus Architecture **APB** Advanced Peripheral Bus **API** Application Programming Interface **ASIC** Application-Specific Integrated Circuits **AXI** Advanced Extensible Interface **BFM** Bus Functional Model **CMF** Common-Mode Failure **COTS** Commercial Off-The-Shelf **CPU** Central Processing Unit **DCLS** Dual-Core Lockstep **DDR** Double Data Rate **DED** Double Error Detecting **DFF** D-Type Flip-Flop **DMR** Dual-Modular Redundancy **DMT** Duplex Multiplexed in Time

| <b>DWC</b> Duplication With Comparison  |

|-----------------------------------------|

| ECC Error Correcting Code               |

| EDC Error Detecting Code                |

| FF Flip-Flop                            |

| FIC Fabric Interface Controller         |

| FP Frame Pointer                        |

| FPGA Field-Programmable Gate Array      |

| FPSoC Field-Programmable System-On-Chip |

| FSM Finite State Machine                |

| GPIO General-Purpose Input/Output       |

| GTMR Global TMR                         |

| HDL Hardware Description Language       |

| I/O Input/Output                        |

| IDE Integrated Development Environment  |

| IoT Internet of Things                  |

| IP Intellectual Property                |

| ISA Instruction Set Architecture        |

| JTAG Joint Test Action Group            |

| LE Logic Elements                       |

| LR Link Register                        |

| LSRAM Large Static Random Access Memory |

| LTMR Local TMR                          |

| MBU Multiple Bit Upset                  |

| MCU Microcontroller Unit                |

| MMIO Memory-Mapped Input/Output         |

- **MMR** Multiple-Modular Redundancy

- **MSS** Microcontroller Subsystem

- **NVM** Non-Volatile Memory

- PC Program Counter

- PCI Peripheral Component Interconnect

- **PSR** Program Status Register

- **RAM** Random Access Memory

- **RISC** Reduced Instruction Set Computer

- **RTL** Register-Transfer Level

- SBU Single Bit Upset

- **SEB** Single Event Burnout

- **SEC** Single Error Correction

- SEDR Single Event Dieletric Rupture

- **SEE** Single Event Effect

- **SEFI** Single Event Functional Interrupt

- **SEGR** Single Event Gate Rupture

- **SEL** Single Event Latchup

- **SET** Single Event Transient

- **SEU** Single Event Upset

- SoC System-on-Chip

- SP Stack Pointer

- SPI Serial Peripheral Interface

- TCLS Triple-Core Lockstep

- **TMR** Triple Modular Redundancy

- **UART** Universal Asynchronous Receiver Transmitter

# **1. Introduction**

Nowadays, we are more and more surrounded by a vast number of technological devices, such as personal computers, smartphones, gadgets, smart devices, and much more. Despite this kind of technology not being developed for critical or safety proposes, it is required the support for some reliability features.

Yet for critical and safety applications, such as a car brake system, as well a medical devices, or even a nuclear reactor system control, the use of reliable technology is a must. It is not desired such critical and safety systems to fail at any time.

Due to human and environment interactions with the technology mentioned above, the research and development of reliable systems with fault tolerance capabilities is a concern, that has been getting particular attention, both from academia and industry. This dissertation explores the integration of a new Instruction Set Architecture (ISA), RISC-V with a fault tolerance technique, the Dual-Core Lockstep (DCLS) over a heterogeneous architecture, adding to the state of the art a new fault tolerance solution in order to achieve reliable technology.

### 1.1 Motivation

Since the beginning of computing science, the electronic systems face reliability problems. First, because the use of components that presents unreliable characteristics, such as vacuum tubes and relays [1, 2], but later, due to the increased systems' complexity, new types of unreliable systems appear even with the introduction of reliable semiconductors.

Recently, the new generation of components use reduced transistor's size, higher clock frequencies, and lower operating core voltages. If, in one hand, the systems are more efficient in power consumption and in performance, on the other hand, they present new dependability problems. For example, at ground level, these systems are more susceptive to Single Event Upset (SEU) induced by radiations that can cause bit-flips [3]. These issues are widely present in the aerospace environment, but now it is also a concern in daily basis systems, such as [4, 5, 6, 7, 8, 9].

Normally, reliability capability applied to daily basis systems do not include fault tolerance techniques, mainly, due to the rising of complexity and development cost. Moreover, with the complexity of the systems in the current days its harder to achieve dependability with simple methods, demanding for new methodologies that can help to meet the mentioned requirements.

In particular, the combination of design diversity at hardware level with lockstep techniques is a open question in the current state of the art. This alliance between the two concepts can provide to systems a fault tolerance against both SEU and Common-Mode Failure (CMF).

### 1.2 Main Goal

In order to follow the technologic evolution, and answer the issue that the new systems generation has a lack in dependability, the main goal of this dissertation goes towards developing a fault tolerance system that uses DCLS in a heterogeneous architecture at core level combining different techniques to provide tolerance to a new range of fault, SEU and CMF.

At the same time, it is important to develop the system with focus on low-end devices and to use the new and emerging RISC-V ISA in one of the cores during the implementation.

#### 1.2.1 Objectives

These objectives are divided in three parts and they derived predominantly from the main goal. They are the key to realize the main goal with success.

The first objective is the development of the Lock-V architecture which includes the two cores, a hardcore Arm Cortex-M and a soft-core RISC-V-based, and also an accelerator that supports the heterogeneous architecture. The objective is to provide system synchronization and error detection between cores.

This objective is carried out through several tasks:

- Deploying a soft-core RISC-V-based in a platform that combines a hard-core Microcontroller Unit (MCU) and an Field-Programmable Gate Array (FPGA), in order to provide a dual-core system with heterogeneous architecture at core level;

- Developing *xLockstep* accelerator in the FPGA to provide the system with DCLS capabilities on different core architectures;

- Connecting both cores with the xLockstep accelerator in the platform, in order to deploy the Lock-V hardware architecture;

- Developing an Application Programming Interface (API) that explains and details the use of the

accelerator while developing a library based on the API, to allow the use of the accelerator in an

agnostic way;

- Testing and verifying the synchronization and error capabilities of the Lock-V architecture.

This second objective consists in the development of the Lock-V framework that provides a simple interface to promote in a friendly way the addition of fault tolerance capabilities in a system.

Due to the lack of recovery capabilities on the Lock-V architecture, the framework has the task to implement the system recovery in software.

This objective is performed through the next tasks:

- Writing functions into the framework to apply cores initialization and the synchronization capabilities between them;

- Writing functions to offer the system recovery capabilities, including saving the processor context and restoring the system to the saved processor context, also known as rollback.

The third objective consists in developing a fault injection system to test the system against faults, while verifying and validating the Lock-V as a fault tolerance system.

This is carried out through the following tasks:

- Adapting the main system with a debugging interface, in order to monitoring the system during the verification phase;

- Developing a injection fault mechanism to emulate SEU on the register files in random register through a random time interrupt.

Despite being important, this dissertation does not focus on memory protection mechanisms, thus, the fault injection test system only concerns the register file.

### **1.3 Dissertation Structure**

After this chapter, that includes a brief context, the motivation, and the goals of this dissertation, the chapter 2 overviews the concepts of dependability in section 2.1. Also, it includes different techniques and methodologies to achieve fault tolerance systems, in section 2.2. The chapter 2 ends with the current state of the art for fault tolerance techniques based in lockstep technique in section 2.3. The chapter 3 explains the platform and the soft-core RISC-V-based choice for this dissertation.

Chapter 4 explains the development of the Lock-V architecture by detailing the *xLockstep* accelerator in section 4.1, and how the Lock-V was integrated with the hardware platform in section 4.2. Moreover, in section 4.3 includes the API definition and the library developed to support the *xLockstep* accelerator. The chapter 5, in order to accomplish the second set of tasks mentioned in the objectives, includes in detail the functions provided by the framework for initialization and synchronization purposes in sections 5.2 and 5.3, respectively. It also includes how the system achieves the system recovery using rollback in sections 5.4 and 5.5. The last set of tasks is described in the chapter 6, that also includes resources utilization as well the cost (memory and execution footprint) of the system Lock-V.

Last but not least, the chapter 7 provides a summary and highlights important consideration about this dissertation while mentioning future improvements.

## 2. Background and State of the Art

This chapter addresses the main concepts of dependability in the section 2.1, which covers attributes, threats, and the means to achieve it. Then, in the section 2.2, it presents fault tolerance techniques as one of the primary ways to achieve dependability. Finally, section 2.3, shows a literature review about fault tolerance techniques.

### 2.1 Dependability

Nowadays the search for reliance systems is in expansion due to the emergence and increase of safetycritical applications, ranging from daily basis systems such as a braking system in a car, or a financial transaction through an automated teller machine, to medical devices, airplanes, nuclear power plants or even aerospace applications [8, 10, 11, 12].

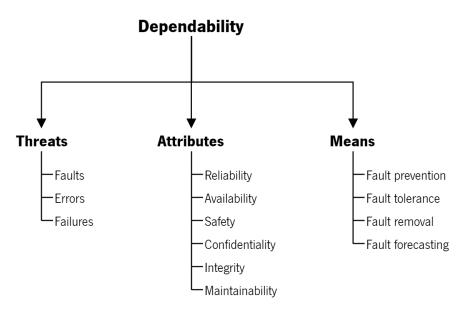

One of the main properties of the computing systems is dependability [10], and Laprie adapted the dependability definition from the primary definition to computer systems as "the quality of the delivered service such that reliance can justifiably be placed on this service" [13]. To understand the previous definition, it is necessary to look for the delivered service meaning, which is the system behavior that the user can observe. A delivered service can be one of the two options: (1) a correct service if the system behavior satisfies the functional specifications previously defined for a concrete system to provide the specified service; or (2) an incorrect service when the system behavior does not match with the expected, i.e., when the delivered service is different from the specified service. The transition from a correct service to an incorrect service is due to failure occurrence, and the reverse transition is named by service restoration [10, 13, 14]. After the dependability definition from Laprie, Avizienis formulated an alternative concept for dependability, taking into account the definition of system failure in order to complement the first definition [10]: "the ability of a system to avoid failures that are more frequent or more severe, and outage durations that are longer, than is acceptable to the user(s).". These definitions lead to the emergence of topics to support the main one since Avizienis et al. wrote the "Fundamental Concepts of Dependability" [10] where, in addition to the dependability definition, they structured the concepts around the main term dependability, and divided into three classes, as shown in Figure 2.1 (adapted from [10, 15]): (1) the threats to dependability, (2) the attributes of dependability, and (3) the means to achieve dependability.

Figure 2.1: Dependability tree.

Faults, errors, and failures are threats to dependability that share a relationship between them. There are six dependability attributes: (1) availability, (2) reliability, (3) safety, (4) confidentiality, (5) integrity, and (6) maintainability. The last class is the means to achieve dependability and they are divided into four main topics: (1) fault prevention, (2) fault tolerance, (3) fault removal, and (4) fault forecasting.

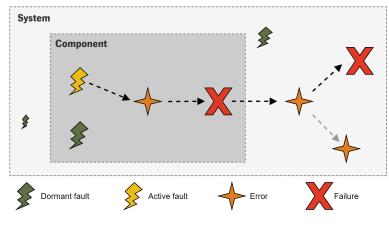

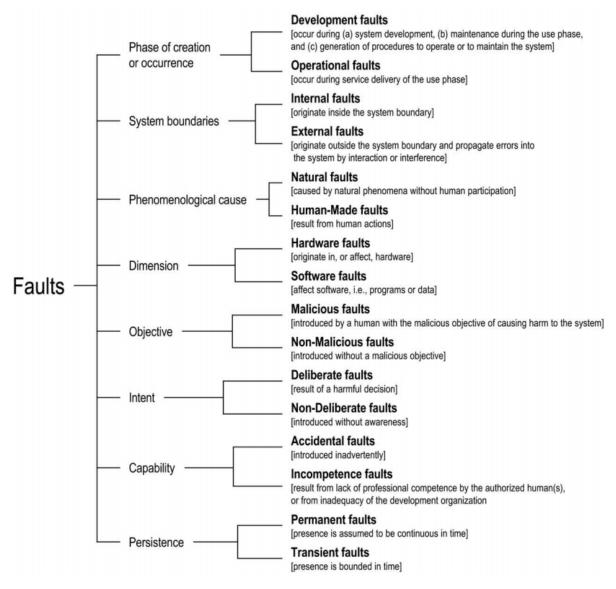

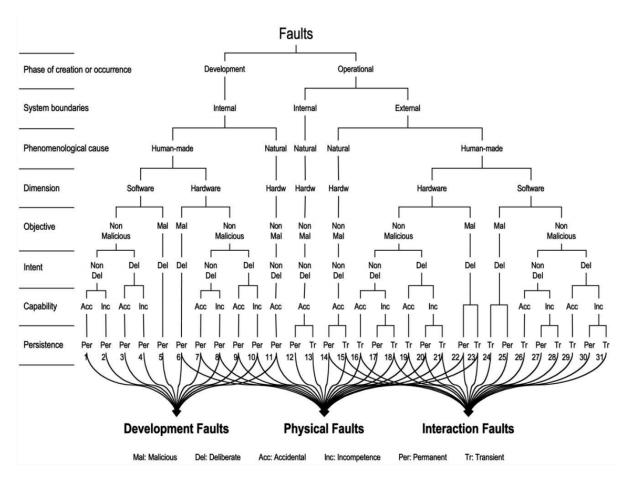

#### 2.1.1 Dependability threats hierarchy