#### Universidade do Minho

Escola de Engenharia

Pedro Alexandre Costa Lobo

**Desenho e Teste de Sistemas Resilientes**

Docombo o Torto do Cirtomas Docillontos

.

### **Universidade do Minho**

Escola de Engenharia

### Pedro Alexandre Costa Lobo

### **Desenho e Teste de Sistemas Resilientes**

Dissertação de Mestrado Mestrado em Engenharia Eletrónica Industrial e Computadores Sistemas Embebidos e Computadores

Trabalho efetuado sob a orientação do **Professor Doutor Jorge Cabral**

DIREITOS DE AUTOR E CONDIÇÕES DE UTILIZAÇÃO DO TRABALHO POR TERCEIROS

Este é um trabalho académico que pode ser utilizado por terceiros desde que respeitadas as re-

gras e boas práticas internacionalmente aceites, no que concerne aos direitos de autor e direitos

conexos.

Assim, o presente trabalho pode ser utilizado nos termos previstos na licença abaixo indicada.

Caso o utilizador necessite de permissão para poder fazer um uso do trabalho em condições

não previstas no licenciamento indicado, deverá contactar o autor, através do RepositóriUM da

Universidade do Minho.

Atribuição-NãoComercial-Compartilhalgual

**CC BY-NC-SA**

https://creativecommons.org/licenses/by-nc-sa/4.0/

iii

## **Agradecimentos**

"Em primeiro lugar, gostaria de agradecer ao meu orientador, doutor Jorge Cabral, por todo o conhecimento transmitido ao longo deste projeto. Um especial agradecimento aos Engenheiros Luís Novais e Nelson Naia por todo o apoio prestado e pela enorme dísponibilidade. Ainda no âmbito académico, gostaria de agradecer ao João Carvalho por toda a ajuda e suporte prestado neste esforço de engenharia.

Não poderia deixar de agradecer aos meus colegas de laboratório, Rui Almeida e Luís Vale, assim como aos meus amigos mais chegados, que me acompanharam desde o ínicio desta longa caminhada, agradeço pelo suporte, alegria e por todos os momento de descontração.

Por fim, endereço um especial agradecimento aos meus pais por todo o suporte emocional e financeiro que me permitiu frequentar e finalizar um curso superior.

A todos que me ajudaram neste percurso, o meu maior obrigado."

This work is supported by: European Structural and Investment Funds in the FEDER component, through the Operational Competitiveness and Internationalization Programme (COMPETE 2020) [Project n° 037902; Funding Reference: POCI-01-0247-FEDER-037902].

### **DECLARAÇÃO DE INTEGRIDADE**

Declaro ter atuado com integridade na elaboração do presente trabalho académico e confirmo que não recorri à prática de plágio nem a qualquer forma de utilização indevida ou falsificação de informações ou resultados em nenhuma das etapas conducente à sua elaboração.

Mais declaro que conheço e que respeitei o Código de Conduta Ética da Universidade do Minho.

### Resumo

#### Desenho e Teste de Sistemas Resilientes

A introdução da condução autónoma no setor automóvel, aumentou a necessidade de sistemas elétricos/eletrónicos (E/E). Como a falha destes sistemas pode resultar na perda do controlo do veículo, a necessidade por sistemas resilientes têm aumentado neste setor. Sistemas resilientes garantem uma baixa probabilidade de falha ao longo da sua vida. Esta baixa probabilidade de falha é alcançada através do uso de redundância e de boas práticas. Apesar de redundância aumentar a resiliência de um sistema, este aumento não é objetivamente quantificável. Tradicionalmente, modelação de resiliência e testes acelerados são utilizados para estimar a probabilidade de falha do sistema ao longo da sua vida.

Esta dissertação visou estudar a eficiência dos métodos tradicionais de estimação de resiliência no contexto dos atuais sistemas automóvel. Para alcançar este objetivo, inicialmente foi desenvolvida uma arquitetura resiliente de hardware para um sensor automóvel. Para estimar a resiliência desta arquitetura e auxiliar o seu desenho, foi desenvolvido um modelo de resiliência com base em Cadeias de Markov, o qual foi simulado recorrendo a métodos de Monte Carlo. Após a implementação da arquitetura desenvolvida, uma amostra com 10 sistemas foi submetida a testes acelerados, os quais recorreram a temperatura como fator de aceleração. Para realizar estes testes, foi previamente desenvolvido um *setup* de testes *online*.

A partir da aplicação dos métodos tradicionais de estimação foi possível concluir que, atualmente, estes métodos não são eficientes para estimar sistemas resilientes no contexto de sistemas automóvel. Por um lado, os fornecedores de componentes não fornecem informação suficiente para realizar estimativas de resiliência fiáveis através de modelos de resiliência. Por outro lado, os fatores de aceleração alcançados durante os testes acelerados não são suficiente para alcançar a fase final da vida de um sistema e assim obter a sua distribuição de falhas, num período que não comprometa o *time-to-market*.

**Palavras-chave**: desenvolvimento de hardware resiliente, redundância, modelação de resiliência, testes acelerados, simulação de Monte Carlo

### **Abstract**

#### **Design and Testing for Reliability**

The introduction of autonomous driving in the automotive sector has increased the necessity of electrical/electronic (E/E) systems. Given that the failure of these systems can result in the loss of control of a vehicle, the necessity for resilient systems has also increased over the years. Resilient systems guarantee the low probability of failure over its lifespan. This low probability of failure is achieved through redundancy and best practices. Although, the redundancy of a given system can promote the system's resilience, it is not objectively quantifiable. Traditionally, the modulation of resiliency and empirical methods are used to estimate the probability of failure of a system during its lifespan.

This dissertation addresses the study of efficiency of these traditional methods used for the estimate of the resiliency but focused on contemporary automotive systems. In order achieve this objective, a development of a hardware resilient architecture was initially made for an automotive sensor. To estimate the resiliency of the architecture and its design, a model of resiliency was developed, based in Markov chain, and simulated using a Monte Carlo method. After the implementation of the developed architecture, a sample of 10 systems were submitted to accelerated tests, which resource to temperature as a factor of acceleration. To accomplish these tests, a pre-emptive development was made of setup for online tests.

The application of traditional methods of estimation, it was possible to conclude that at this moment, these methods are insufficient to estimate resilient systems for an automotive application. On the hand, manufactures of components do not provide sufficient information to make appraisals of their resiliency using the mentioned models of resiliency. Still, the acceleration factors achieved during the accelerated tests were not sufficient to reach wear-out and, thus, obtain a distributed failure of a given system, at least within a timeline that does not compromise the time-to-market.

**Keywords:** resilient hardware development, redundancy, resiliency modulation, accelerated testing, Monte Carlo simulations

# Índice

| 1 | Intro | odução  |                                                  | 1  |

|---|-------|---------|--------------------------------------------------|----|

|   | 1.1   | Motiva  | ção e Objetivos                                  | 2  |

|   | 1.2   | Estrutu | ıra da Dissertação                               | 4  |

| 2 | Esta  | do da A | urte                                             | 5  |

|   | 2.1   | Sistem  | as Embebidos                                     | 5  |

|   |       | 2.1.1   | Fases do Desenvolvimento de um Sistema Embebido  | 6  |

|   |       | 2.1.2   | Desenho de PCBs                                  | 8  |

|   | 2.2   | Sistem  | as Resilientes                                   | 11 |

|   |       | 2.2.1   | Faltas, Erros e Falhas                           | 12 |

|   |       | 2.2.2   | Distribuição de Falhas                           | 13 |

|   |       |         | Curva da Banheira                                | 15 |

|   |       | 2.2.3   | Taxa de Falha, MTBF and MTTF                     | 17 |

|   |       | 2.2.4   | Redundância                                      | 18 |

|   |       |         | Redundância de Hardware                          | 18 |

|   |       |         | Redundância de Software                          | 21 |

|   |       |         | Redundância de Informação                        | 22 |

|   |       |         | Redundância Temporal                             | 22 |

|   |       |         | Redundância e Diversidade                        | 23 |

|   |       | 2.2.5   | Métodos para Estimar a Resiliência de um Sistema | 23 |

|   |       | 2.2.6   | Métodos Analíticos: Modelação de Resiliência     | 25 |

|   |       |         | Probabilidade Convencional                       | 26 |

|   |       |         | Tabela de Verdade                                | 27 |

|   |       |         | Diagramas lógicos                                | 29 |

|   |       |         | Cadeias de Markov                                | 29 |

|   |       |         | Simulação de Monte Carlo                         | 31 |

|   |      | 2.2.7    | Testes Acelerados                                      | 32 |

|---|------|----------|--------------------------------------------------------|----|

|   |      |          | Testes Quantitativos <i>versus</i> Testes Qualitativos | 32 |

|   |      |          | Relações Entre Vida Acelerada e Vida Normal            | 33 |

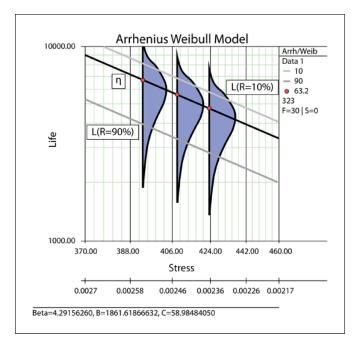

|   |      |          | Modelo de Arrhenius                                    | 33 |

| 3 | Simi | ılação e | e Testes Acelerados para Hardware Resiliente           | 36 |

|   | 3.1  | Simula   | ções de Resiliência do Sistema                         | 40 |

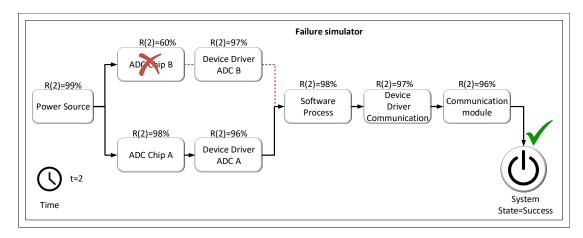

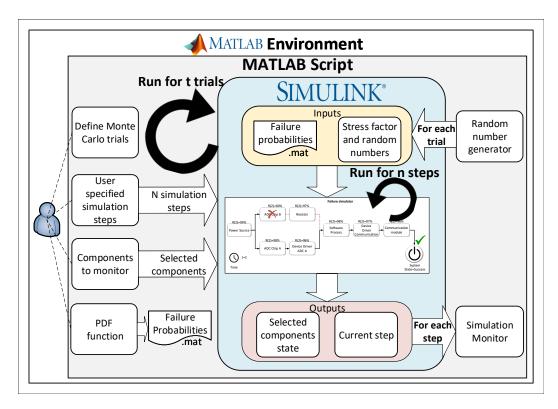

|   |      | 3.1.1    | Ecossistema do <i>Failure Simulator</i>                | 41 |

|   |      | 3.1.2    | Modelação e Interligação dos Componentes               | 44 |

|   | 3.2  | Setup p  | para Testes Acelerados                                 | 46 |

|   |      | 3.2.1    | Overview do Setup para Testes Acelerados               | 47 |

|   |      | 3.2.2    | DUT Interface PCB                                      | 47 |

|   |      | 3.2.3    | Serviços de Software                                   | 49 |

|   |      |          | Data Collection Service                                | 50 |

|   |      |          | Aplicação Gráfica                                      | 52 |

|   | 3.3  | Sumári   | 0                                                      | 56 |

| 4 | Case | de Est   | udo                                                    | 57 |

|   | 4.1  | Steering | g Angle Sensor                                         | 57 |

|   |      | 4.1.1    | Conceito para o SAS                                    | 59 |

|   |      | 4.1.2    | Arquitetura do Sistema                                 | 61 |

|   |      | 4.1.3    | Escolha da Plataforma                                  | 66 |

|   |      | 4.1.4    | Seleção de Componentes                                 | 66 |

|   |      | 4.1.5    | Desenho dos Circuitos                                  | 68 |

|   |      | 4.1.6    | Layout                                                 | 70 |

|   | 4.2  | Estimaç  | ção da Resiliência do SAS                              | 70 |

|   |      | 4.2.1    | Simulações de Resiliência da Arquitetura do SAS        | 71 |

|   |      |          | Resultados das Simulações de Resiliência               | 72 |

|   |      | 4.2.2    | Testes Acelerados ao SAS                               | 75 |

|   |      |          | Testes Realizados                                      | 78 |

|   |      |          | Resultados dos Testes Acelerados ao SAS                | 79 |

|   | 4.3  | Sumário  | 0                                                      | 79 |

| 5 | Conclusões |                                                          | 81  |

|---|------------|----------------------------------------------------------|-----|

|   | 5.1        | Conclusões Sobre o Desenho de Sistemas Resilientes       | 82  |

|   | 5.2        | Trabalho Futuro                                          | 83  |

| A | Setu       | p para Testes Acelerados Material Auxiliar               | 90  |

|   | A.1        | Esquemáticos e <i>Layout</i> da <i>DUT Interface PCB</i> | 90  |

|   | A.2        | Diagramas Auxiliares do Data Collection Service          | 94  |

|   | A.3        | Diagramas Auxiliares da Aplicação Gráfica                | 96  |

| В | Des        | envolvimento do Steering Angle Sensor Material Auxiliar  | 99  |

|   | B.1        | Diagrama de Máquina de Estados                           | 99  |

|   | B.2        | SAS Esquemáticos e <i>Layout</i>                         | 101 |

|   | B.3        | Modelo de Simulação do SAS                               | 104 |

|   | B.4        | Testes acelerados do SAS                                 | 105 |

# Lista de Figuras

| 2.1  | rases do desenvolvimento de um sistema empedido                                | C  |

|------|--------------------------------------------------------------------------------|----|

| 2.2  | Placas de circuito impresso (PCB) com quatro <i>layers</i>                     | 8  |

| 2.3  | Multilayer PCB                                                                 | 9  |

| 2.4  | Exemplo de uma função função densidade de probabilidade (PDF)                  | 13 |

| 2.5  | Relação entre as funções PDF (t), função distribuição de probabilidade acumu-  |    |

|      | lada (CDF) (t), resiliência (R) (t) e taxa de falha ( $\lambda$ ) (t)          | 14 |

| 2.6  | Curva da banheira                                                              | 15 |

| 2.7  | Arquitetura NMR                                                                | 19 |

| 2.8  | Arquitetura Duplication with comparison.                                       | 19 |

| 2.9  | Exemplos de arquiteturas que exploram redundância dinâmica, a) hot standby,    |    |

|      | b) cold standby                                                                | 20 |

| 2.10 | Exemplos de arquiteturas que exploram redundância híbrida, a) self-purging, b) |    |

|      | duo-duplex                                                                     | 21 |

| 2.11 | Modelação e estimação de resiliência                                           | 24 |

| 2.12 | Exemplo de um modelo de resiliência do sistema                                 | 25 |

| 2.13 | Exemplo de um modelo com dois componentes em Paralelo                          | 26 |

| 2.14 | Exemplo de um modelo com dois componentes em série                             | 27 |

| 2.15 | Exemplo de um modelo com configurações série e paralelo                        | 27 |

| 2.16 | Tabela de verdade para o modelo com configurações série e paralelo             | 28 |

| 2.17 | Diagramas lógicos para o modelo com configurações série e paralelo             | 29 |

| 2.18 | Exemplo de um sistema composto apenas por um componente                        | 30 |

| 2.19 | Exemplo de um sistema composto apenas por um componente                        | 34 |

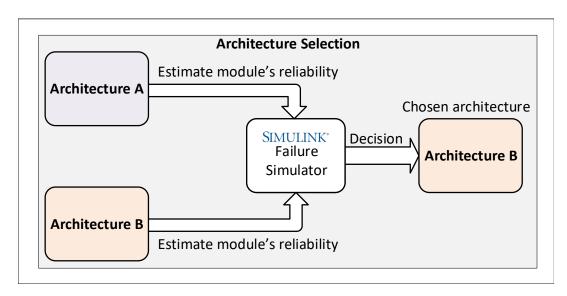

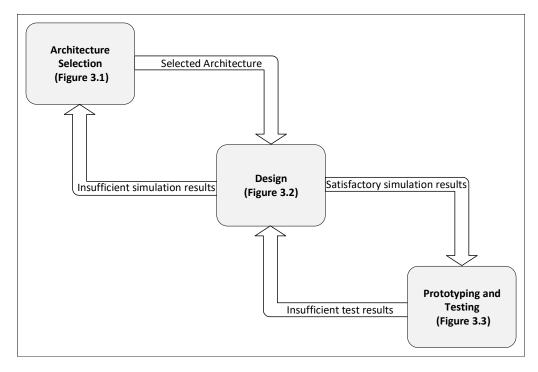

| 3.1  | Fase1: seleção da arquitetura do sistema                                       | 37 |

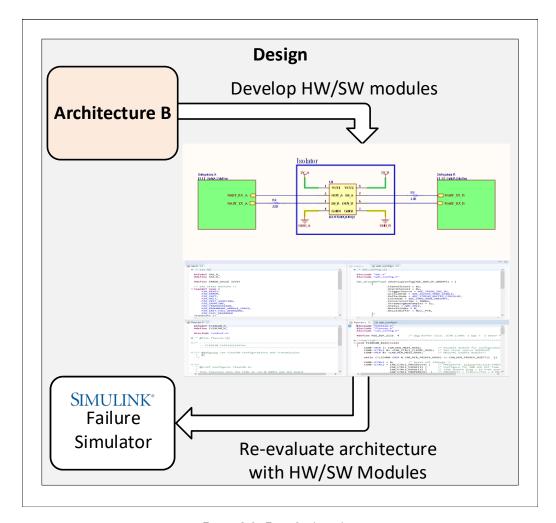

| 3.2  | Fase 2: desenho                                                                | 38 |

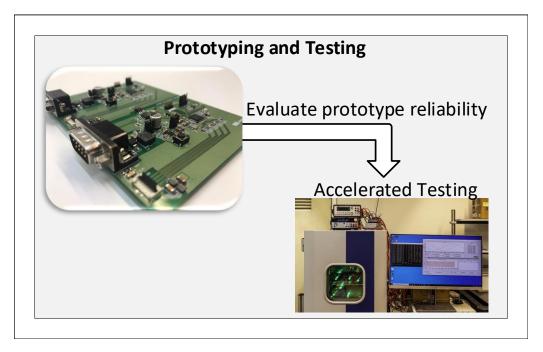

| 3.3  | Fase 3:Prototipagem e teste                                                    | 39 |

| 3 4  | Interações entre as diversas fases do desenvolvimento do sistema               | 40 |

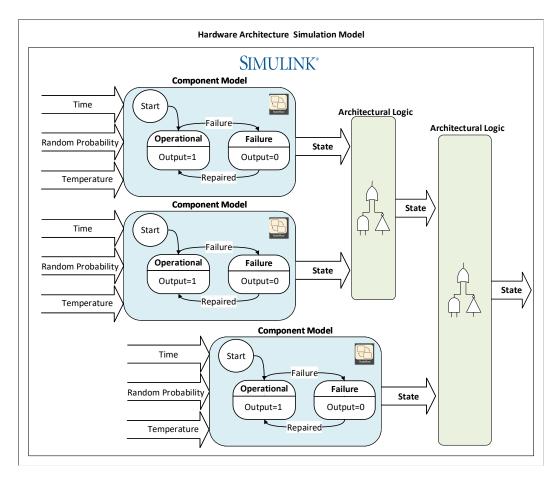

| 3.5  | Simulações de resiliência, <i>overview</i> conceptual                                   | 41 |

|------|-----------------------------------------------------------------------------------------|----|

| 3.6  | Ambiente de Simulação.                                                                  | 41 |

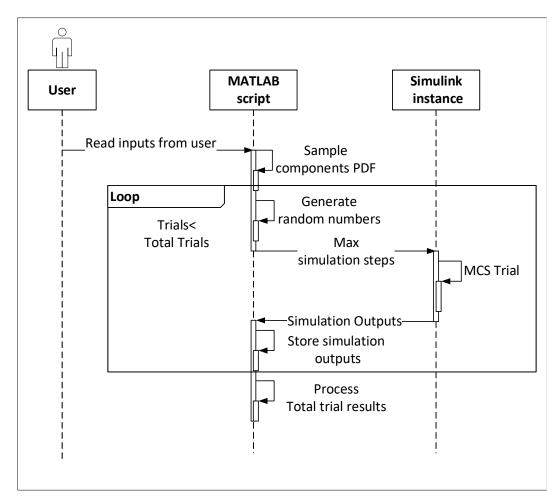

| 3.7  | Diagrama de sequência das simulações                                                    | 42 |

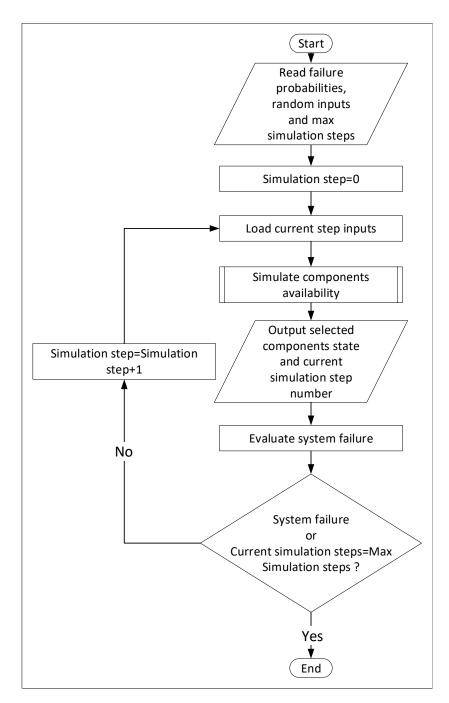

| 3.8  | Fluxograma de um Monte Carlo <i>trial.</i>                                              | 43 |

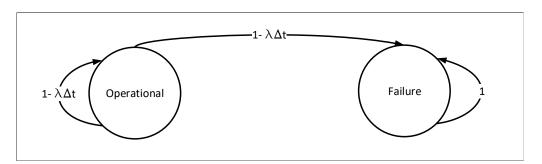

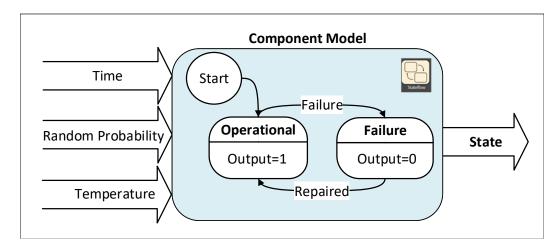

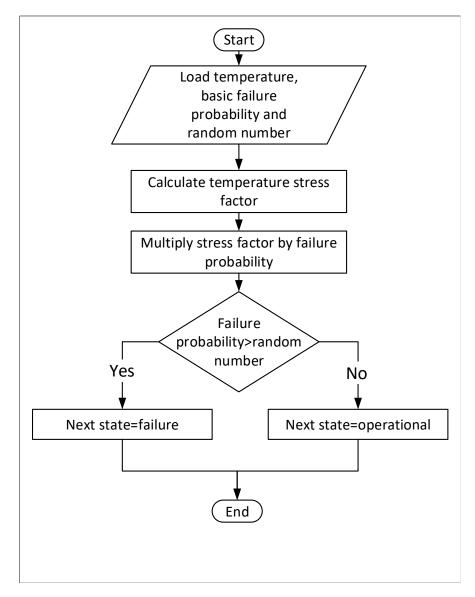

| 3.9  | Máquina de estados de um componente                                                     | 44 |

| 3.10 | Fluxograma do estado <i>operational</i>                                                 | 45 |

| 3.11 | Overview de um módulo                                                                   | 46 |

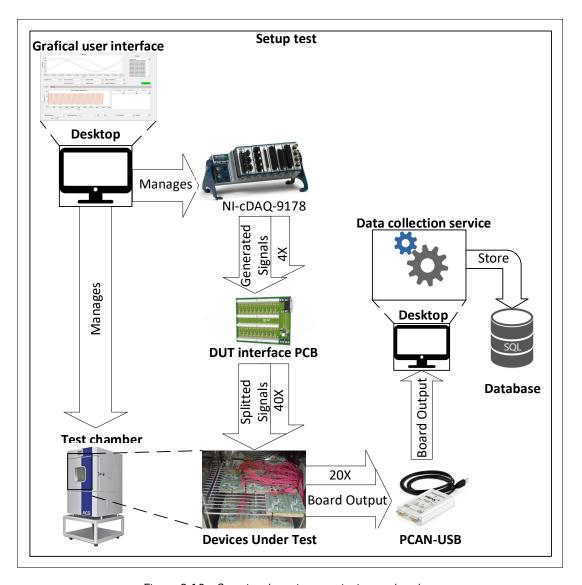

| 3.12 | Overview do setup para testes acelerados                                                | 48 |

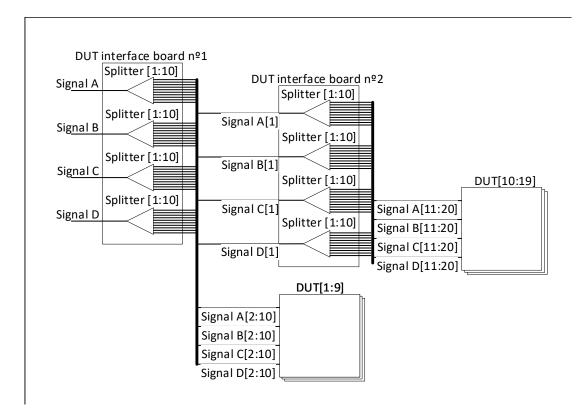

| 3.13 | Daisy chaining com 2 boards                                                             | 49 |

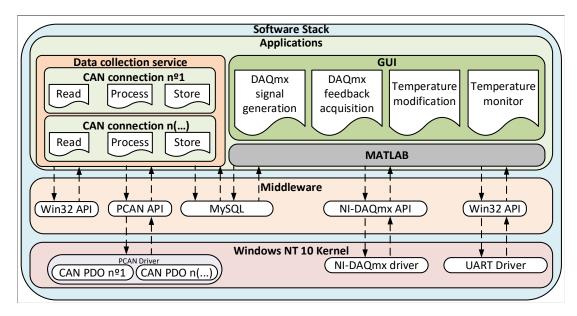

| 3.14 | Software <i>stack</i> do <i>setup</i> para testes acelerados                            | 50 |

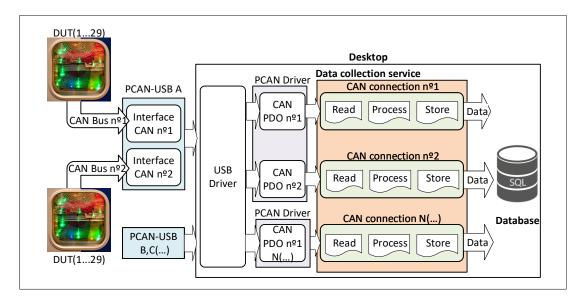

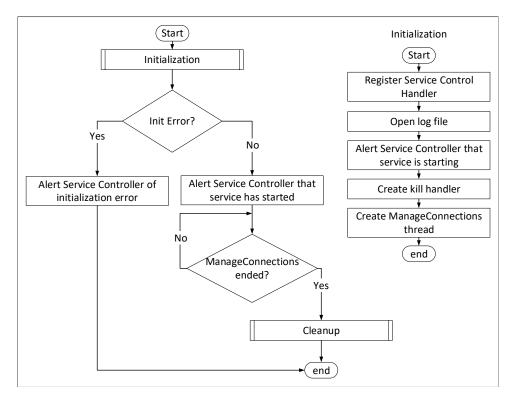

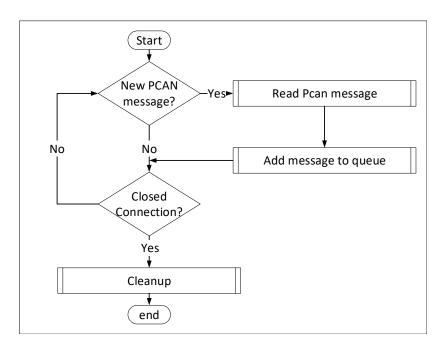

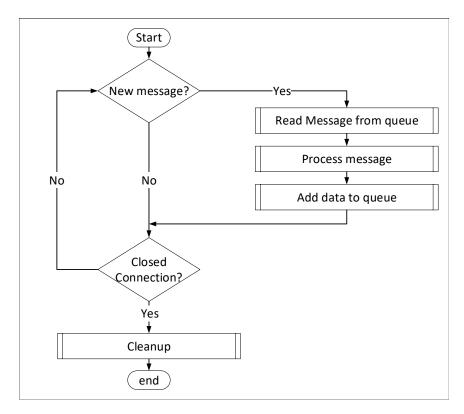

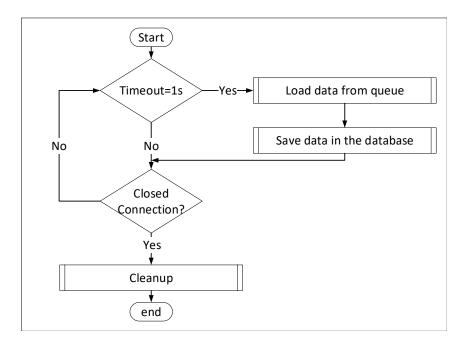

| 3.15 | Overview do data collection service                                                     | 51 |

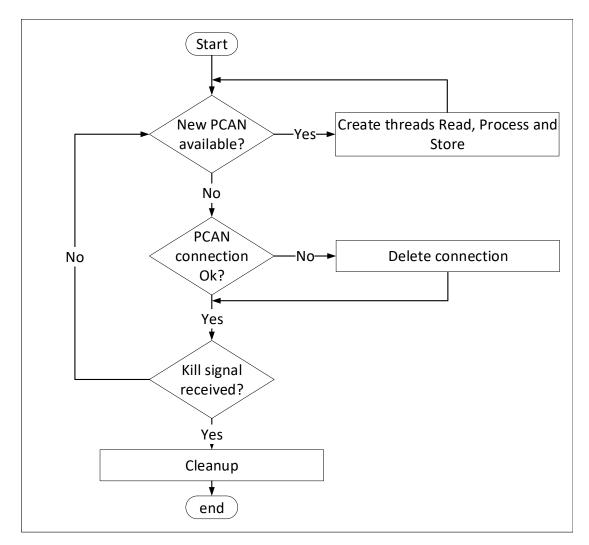

| 3.16 | Fluxograma da <i>manage connection task</i>                                             | 52 |

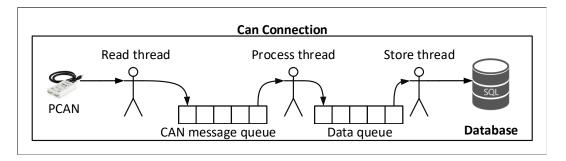

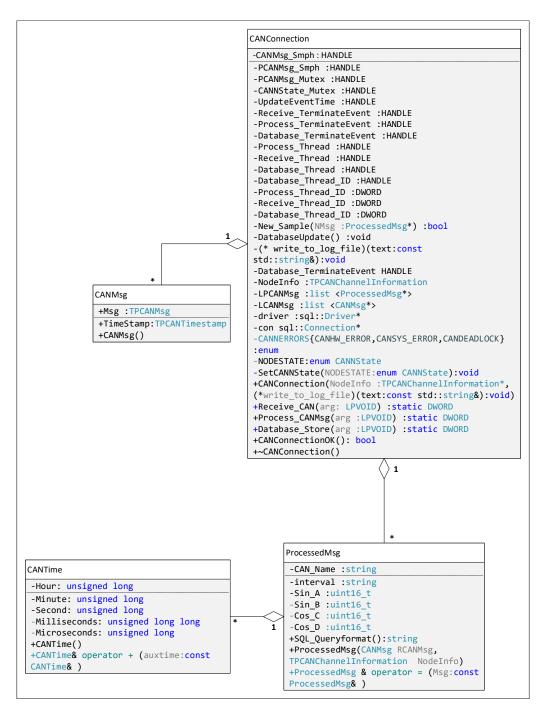

| 3.17 | Interações entre as <i>threads</i> de cada conexão <i>controller area network</i> (CAN) | 52 |

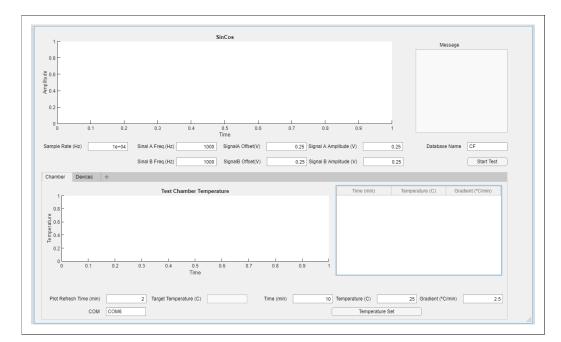

| 3.18 | Frontend da aplicação gráfica                                                           | 53 |

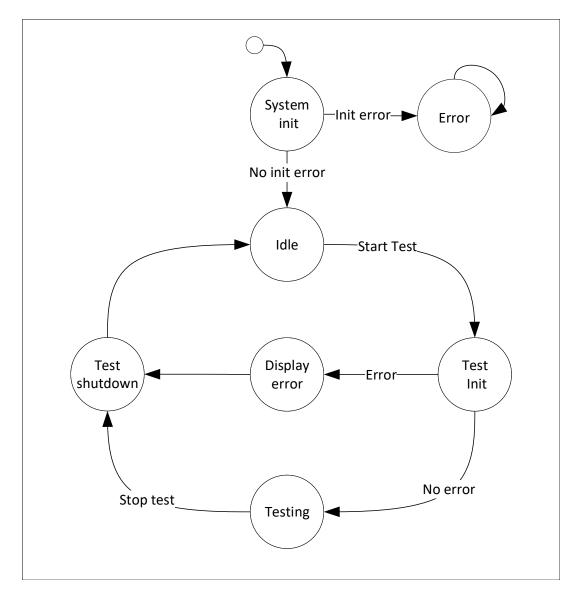

| 3.19 | Máquina de estados do <i>backend</i>                                                    | 54 |

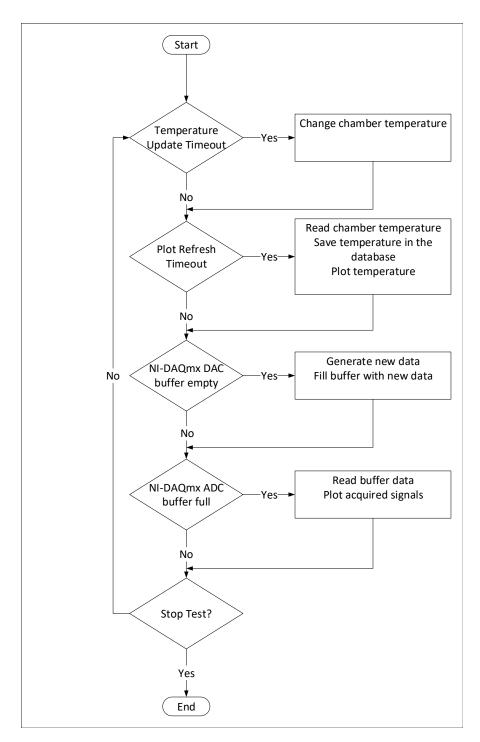

| 3.20 | Fluxograma do estado <i>testing</i>                                                     | 55 |

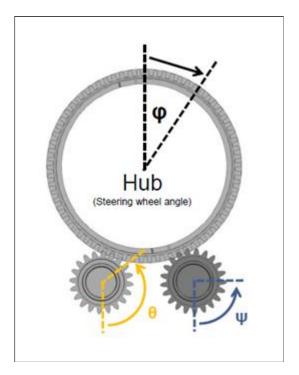

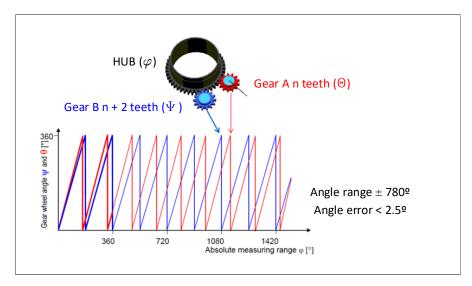

| 4.1  | Transmissão do movimento do volante (HUB + Gears)                                       | 58 |

| 4.2  | Relação entre as <i>gears</i> e o ângulo absoluto                                       | 58 |

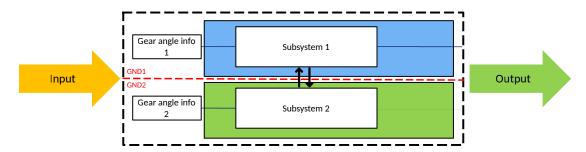

| 4.3  | Diagrama de blocos do conceito do SAS.                                                  | 60 |

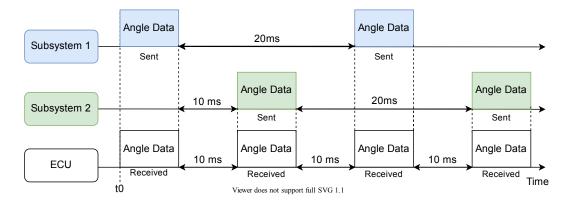

| 4.4  | Diagrama temporal do SAS                                                                | 60 |

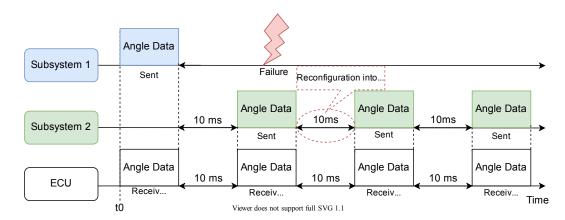

| 4.5  | Diagrama temporal do SAS após a falha de um dos módulos                                 | 60 |

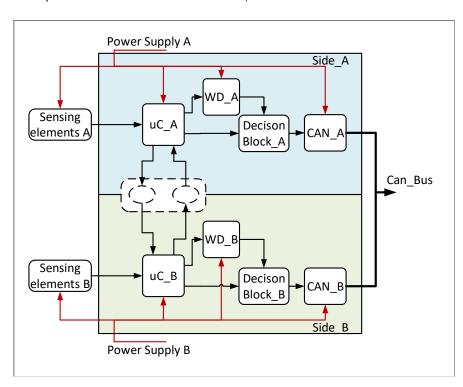

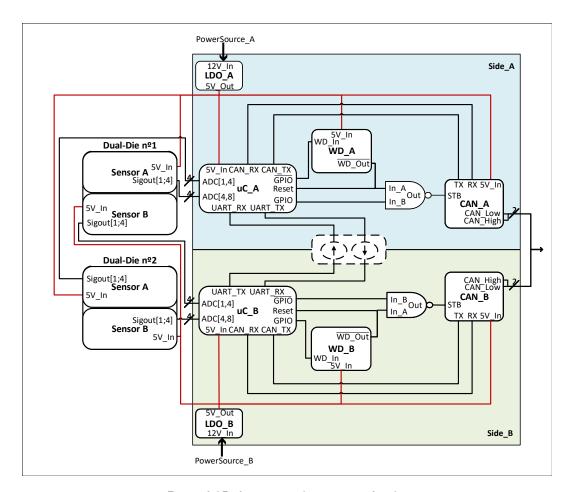

| 4.6  | Arquitetura do sistema                                                                  | 61 |

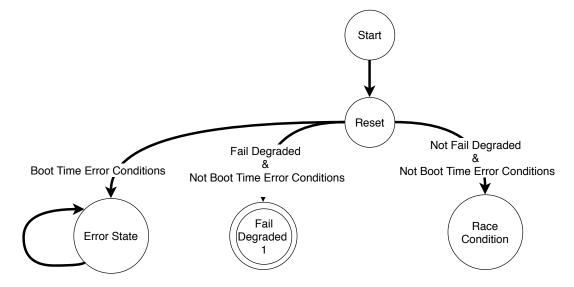

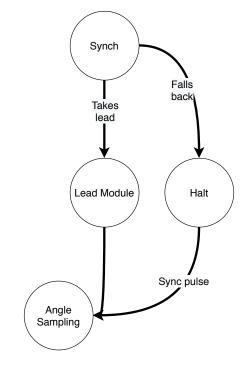

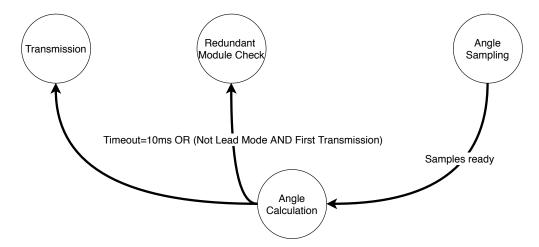

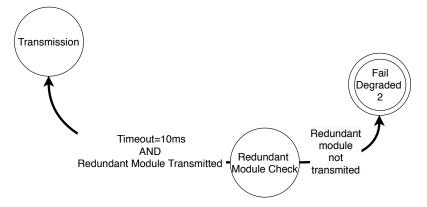

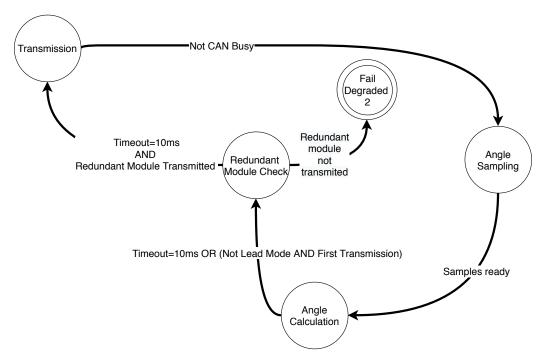

| 4.7  | Máquina de estados (1).                                                                 | 63 |

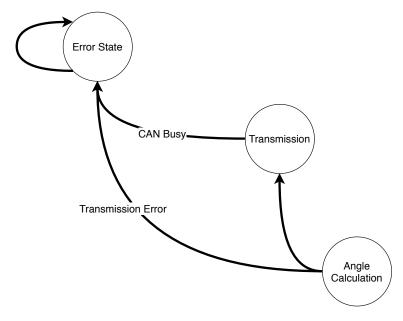

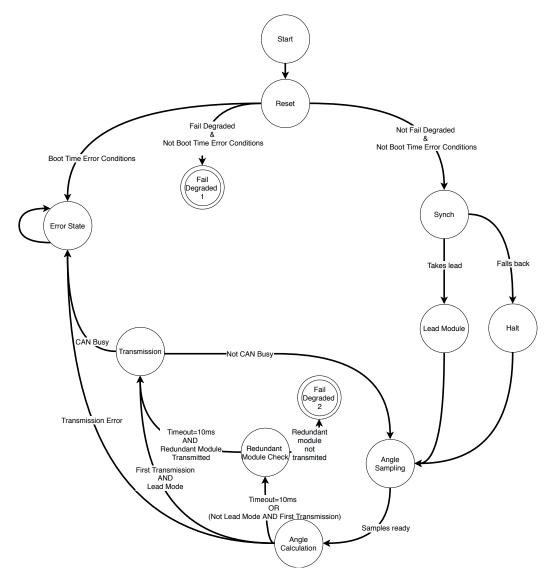

| 4.8  | Máquina de estados (2).                                                                 | 63 |

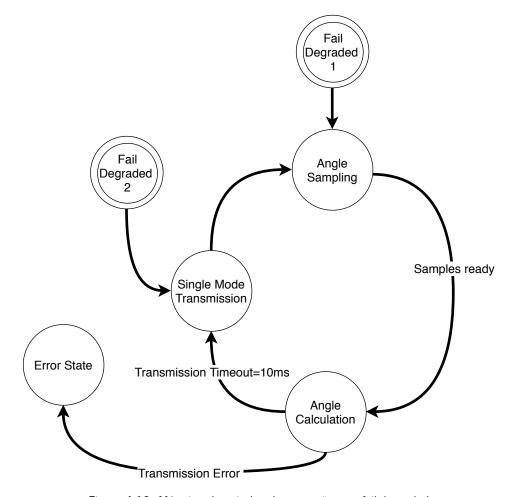

| 4.9  | Máquina de estados (3).                                                                 | 64 |

| 4.10 | Máquina de estados (4).                                                                 | 64 |

| 4.11 | Máquina de estados da operação normal                                                   | 65 |

| 4.12 | Máquina de estados (5).                                                                 | 65 |

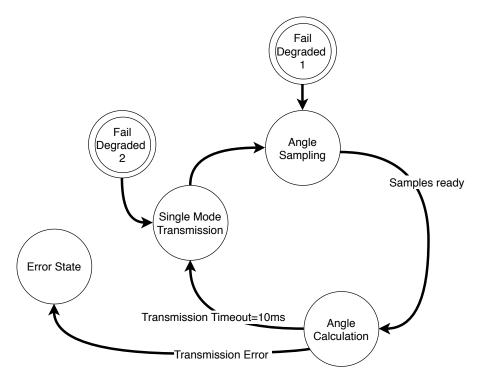

| 4.13 | Máquina de estados da operação em <i>fail-degraded</i>                                  | 66 |

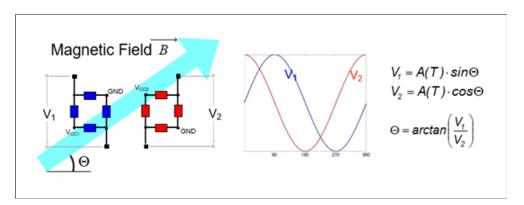

| 4.14 | Resposta dos sensores magnéticos                                                        | 67 |

| 4 15 | Arquitetura do sistema refinada                                                         | 69 |

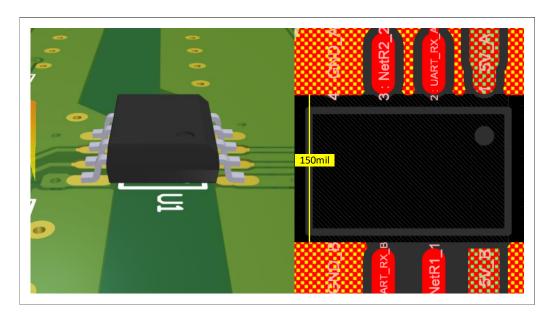

| 4.16 | Clearance entre os planos de massa dos dois módulos redundantes                     | /0 |

|------|-------------------------------------------------------------------------------------|----|

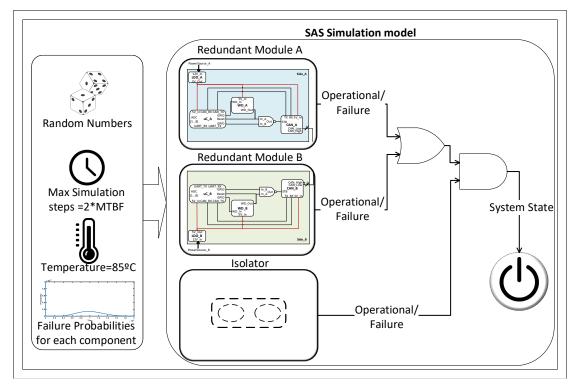

| 4.17 | Overview do modelo de simulação do SAS                                              | 71 |

| 4.18 | Exemplo de uma função PDF, gerada a partir do tempo médio entre falhas              |    |

|      | (MTBF) do $\it watchdog$ , de valor $10^6$ , e das assunções realizadas             | 72 |

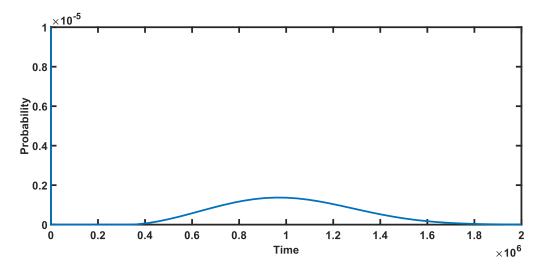

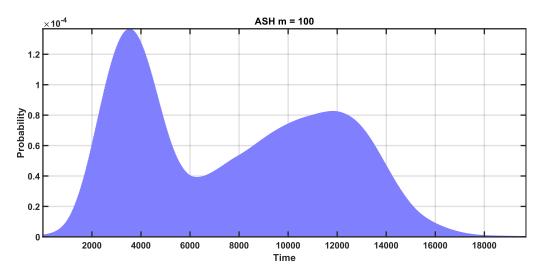

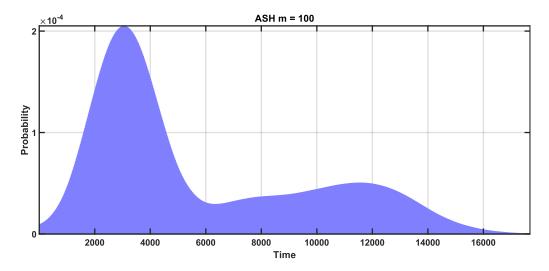

| 4.19 | Função PDF resultante das simulações da arquitetura de hardware do SAS              | 73 |

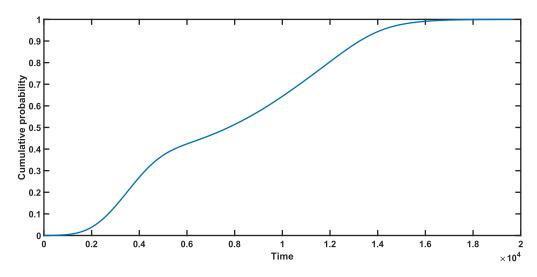

| 4.20 | Função CDF resultante das simulações da arquitetura de hardware do SAS              | 73 |

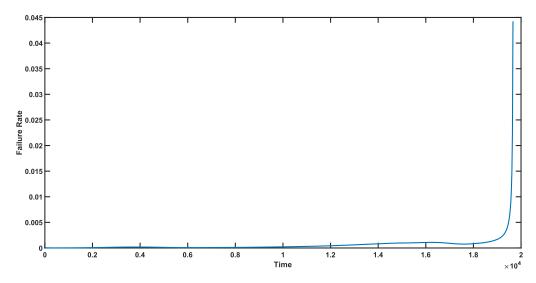

| 4.21 | Função $\lambda$ resultante das simulações da arquitetura de hardware do SAS        | 74 |

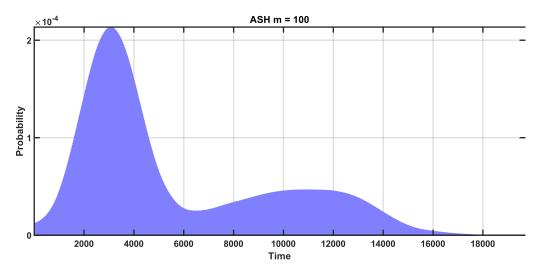

| 4.22 | Função PDF do módulo redundante A                                                   | 74 |

| 4.23 | Função PDF do módulo redundante B                                                   | 75 |

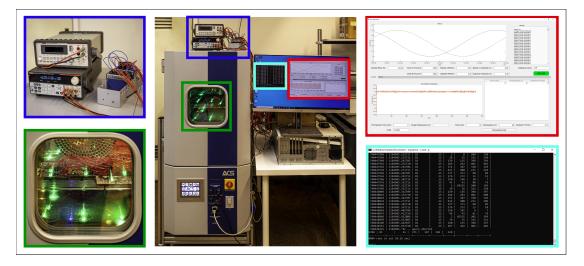

| 4.24 | Overview do <i>setup</i> para os testes acelerados: (1) Azul escuro: NI-cDAQ-9178 e |    |

|      | fontes de alimentação; (2) Azul claro: dados armazenados na base de dados;          |    |

|      | (3) Verde: protótipos na câmara climática; (4) Vermelho: Aplicação Gráfica; .       | 75 |

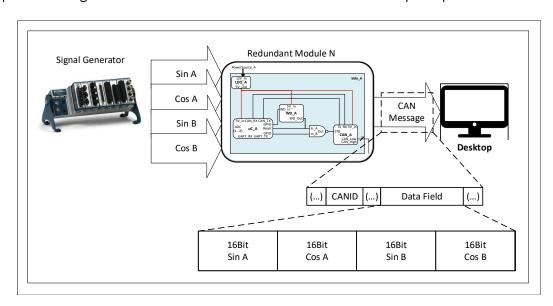

| 4.25 | Overview do <i>setup</i> para os testes acelerados de um módulo de um protótipo     | 76 |

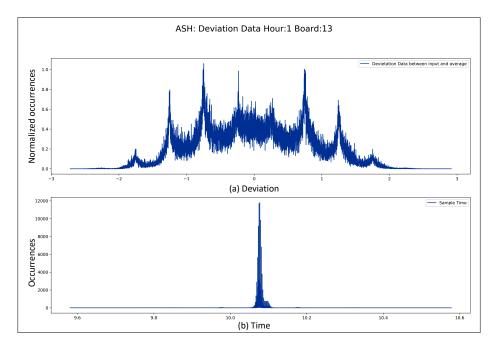

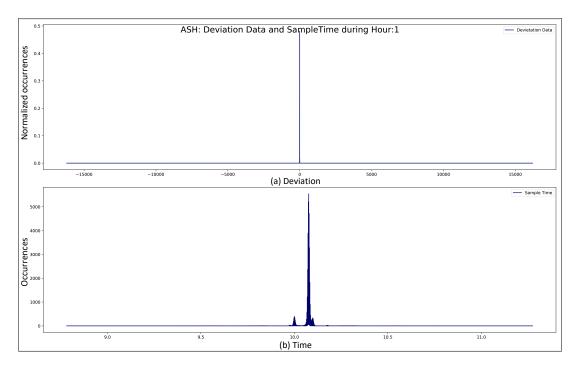

| 4.26 | Averaged shifted histogram (ASH) com os desvios entre os sinais amostrados e        |    |

|      | um sinal médio (a), e períodos entre transmissão (b) de um protótipo em teste,      |    |

|      | durante 1 hora                                                                      | 77 |

| 4.27 | ASH com os desvios entre sinais amostrados e um sinal médio (a), e períodos         |    |

|      | de transmissão (b) de todos os protótipo em teste, durante 1 hora                   | 78 |

| A.1  | Overview dos esquemáticos da DUT interface                                          | 91 |

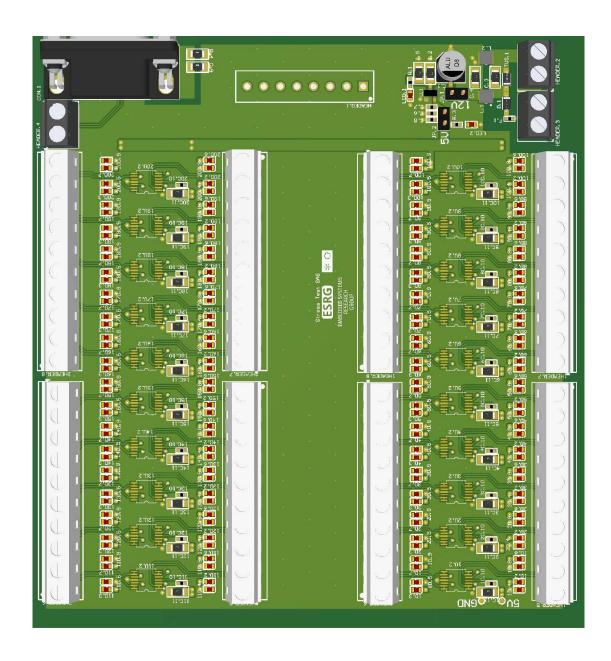

| A.2  | PCB da <i>DUT interface</i> vista de cima                                           | 92 |

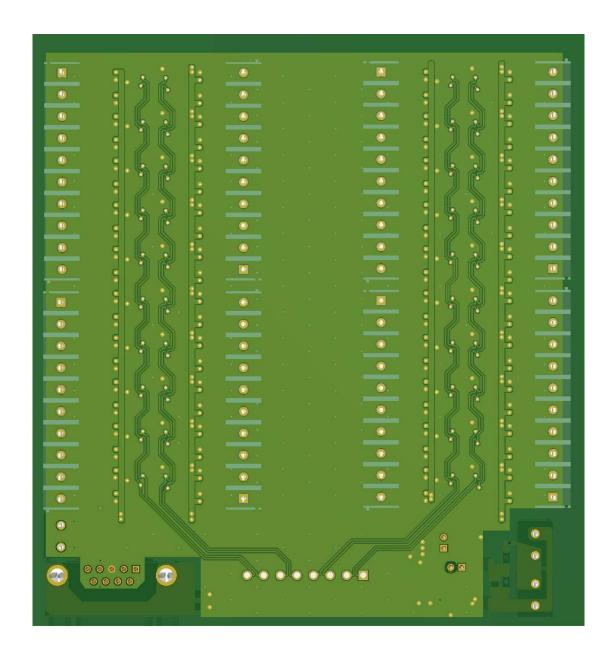

| A.3  | PCB da <i>DUT interface</i> vista de baixo                                          | 93 |

| A.4  | Fluxograma da <i>main task.</i>                                                     | 94 |

| A.5  | Fluxograma da <i>read task</i>                                                      | 94 |

| A.6  | Fluxograma da <i>process task</i>                                                   | 95 |

| A.7  | Fluxograma da <i>store task.</i>                                                    | 95 |

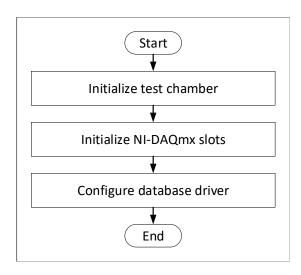

| A.8  | Fluxograma do estado <i>initialization</i>                                          | 96 |

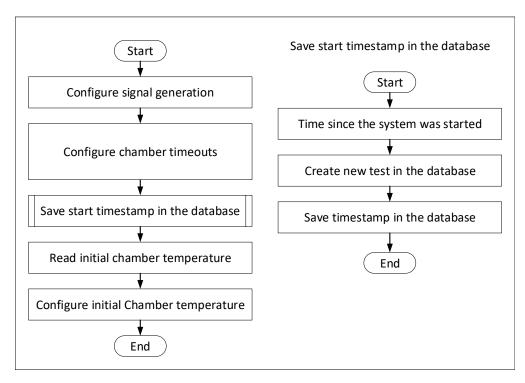

| A.9  | Fluxograma do estado <i>test initialization</i>                                     | 96 |

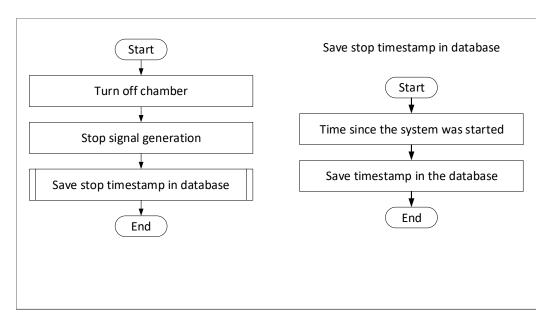

| A.10 | Fluxograma do estado <i>test shutdown</i>                                           | 97 |

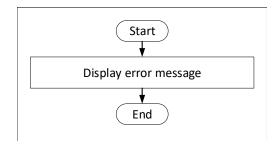

| A.11 | Fluxograma do estado <i>aborting test</i>                                           | 97 |

| A.12 | Fluxograma do estado <i>initialization error</i>                                    | 97 |

| A.13 | Diagrama de classes de uma conexão CAN                                              | 98 |

| B.1 | Máquina de estados do SAS operação em fail-degraded                        | 99  |

|-----|----------------------------------------------------------------------------|-----|

| B.2 | Máquina de estados do SAS operação normal                                  | 100 |

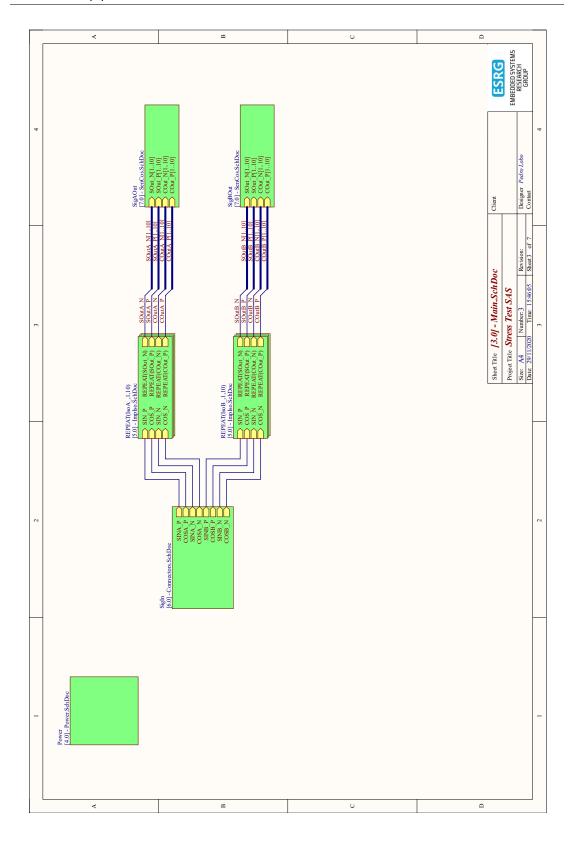

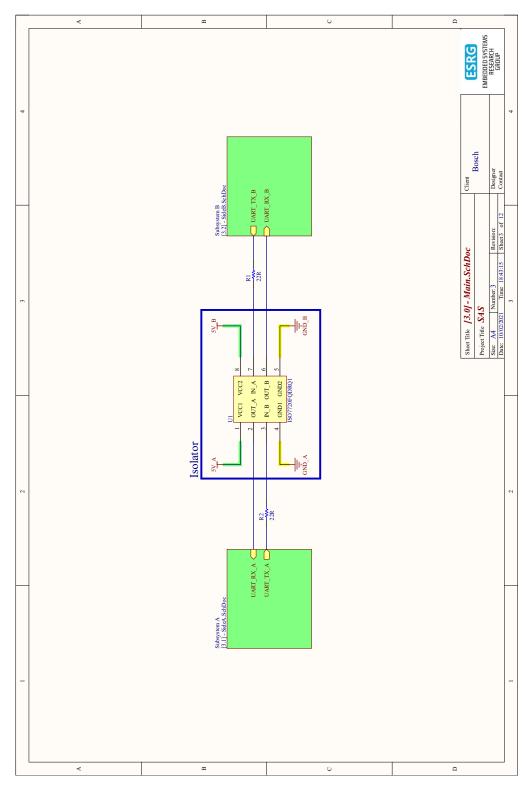

| B.3 | Overview dos esquemáticos do steering angle sensor (SAS)                   | 101 |

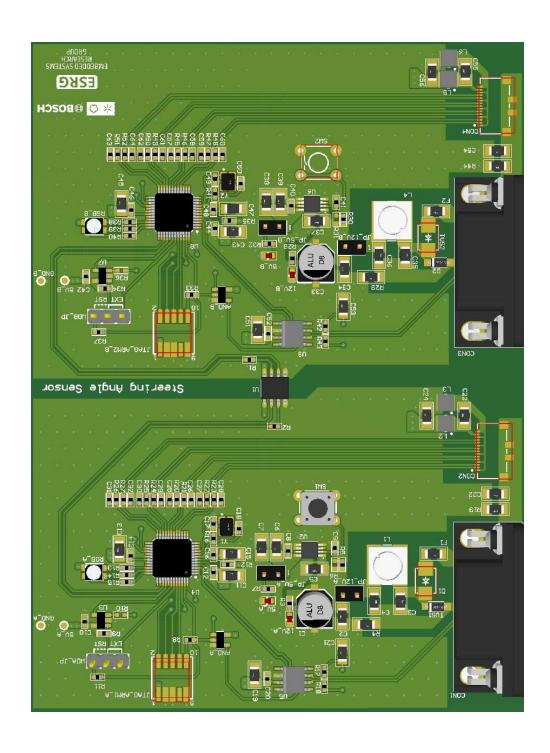

| B.4 | PCB do SAS vista de cima.                                                  | 102 |

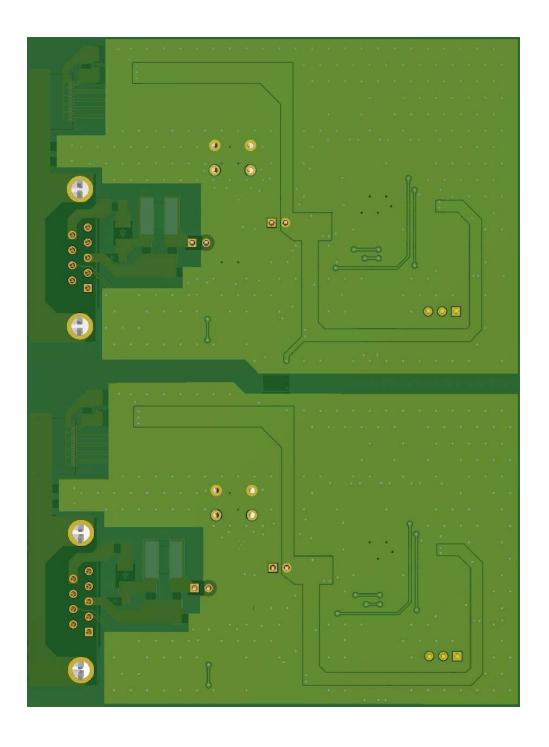

| B.5 | PCB do SAS vista de baixo                                                  | 103 |

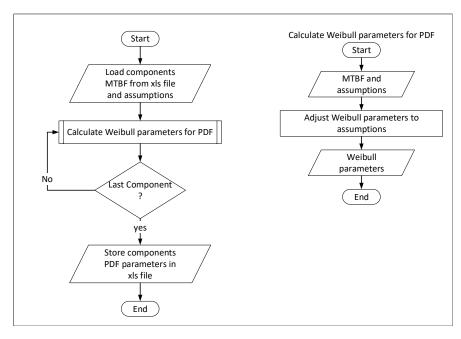

| B.6 | Fluxograma do cálculo da função PDF                                        | 104 |

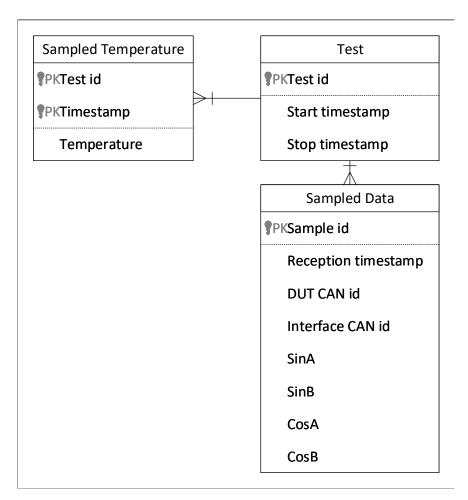

| B.7 | Diagrama entidade relacionamento da base de dados utilizada para armazena- |     |

|     | mento dos dados recolhidos durante o teste aos 10 protótipos do SAS        | 105 |

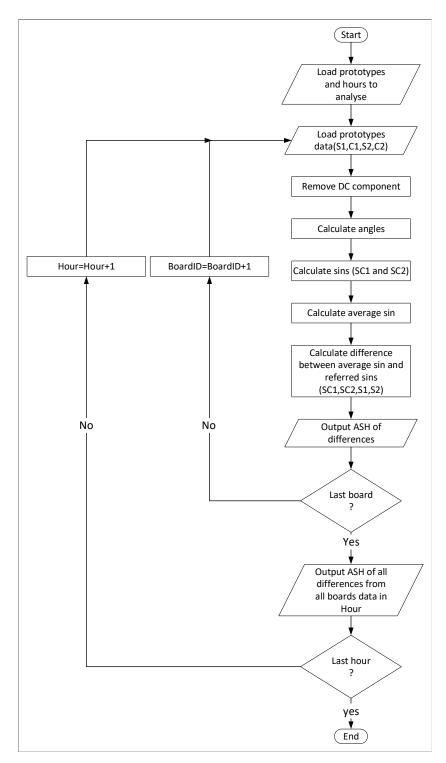

| B.8 | Processamento dos dados dos testes acelerados                              | 106 |

# Lista de Tabelas

| 3.1 | Comparação entre componentes                                      | 49  |

|-----|-------------------------------------------------------------------|-----|

| 4.1 | Comparação entre isoladores que recorrem a diferentes tecnologias | 68  |

| 4.2 | Tabela de verdade do <i>decision block</i>                        | 68  |

| B.1 | MTBFs dos componentes usados para o modelo do SAS.                | 104 |

### Lista de Acrónimos

$\lambda$  Taxa De Falha

**ADC** Conversor Analógico-Digital

**AEC** Automotive Electronics Council

API Interface De Programação De Aplicações

**AQEC** Aerospace Qualified Electronic Component

**ASH** Averaged Shifted Histogram

ASIL Automotive Safety Integrity Level

**BbW** Break-by-Wire

**CAN** Controller Area Network

CDF Função Distribuição De Probabilidade Acumulada

**COTS** Commercial off-the-Shelf

CRC Cyclic Redundancy Check

**E/E** Elétricos/eletrónicos

Ea Energia De Ativação

**EMC** Compatibilidade Eletromagnética

EMI Interferência Eletromagnética

ESD Descarga Electrostática

FSM Máquina De Estados Finita

**GPIO** General Purpouse Input/ output

**HALT** Highly Accelerated Life Test

IC Circuito Integrado

LDO Regulador De Tensão

MIL-PRF Military Performance Specification

MTBF Tempo Médio Entre Falhas

MTTF Tempo Médio Até À Falha

NMR N-Modular Redundancy

**OPAMP** Amplificador Operacional

PC Computador Pessoal

**PCB** Placas De Circuito Impresso

PDF Função Densidade De Probabilidade

PDO Physical Device Object

R Resiliência

**RF** Radiofrequência

**SAS** Steering Angle Sensor

SbW Steer-by-Wire

**SMT** Surface-Mount Technology

**TbW** Throttle-by-Wire

**UART** Universal Asynchronous Receiver Transmitter

**XbW** X-by-Wire

# Capítulo 1

## Introdução

Sistemas resilientes tornaram-se populares em aplicações militares em meados do século XX [1]. Desde então, estes sistemas são aplicados nos setores nuclear, aeroespacial, aeronáutico, suporte de vida, e mais recentemente, na indústria automóvel. A resiliência é uma propriedade que está diretamente relacionada com a probabilidade de falha do sistema. Desta forma, um sistema que apresente uma elevada resiliência possui uma baixa probabilidade de falha. Sistemas resilientes são pretendidos em aplicações onde uma falha pode ter consequências severas.

A baixa probabilidade de falha de um sistema pode ser alcançada através da utilização de um conjunto de boas práticas e do uso de técnicas de tolerância a faltas. Nesta dissertação, o foco será no desenvolvimento e teste de uma solução de hardware resiliente.

A utilização de boas práticas no desenvolvimento destes sistemas minimiza a introdução de faltas de desenvolvimento. O conjunto de boas práticas utilizadas no desenvolvimento destes sistemas, estão reunidas em dispendiosos *standards* de diferentes setores como o ISO:26262 no caso do setor automóvel, ou em documentos privados de empresas com experiência no desenvolvimento destes sistemas. Contudo, existem alguns autores que fornecem algumas diretrizes para o desenho, modelação e estimação destes sistemas [1], [2].

Relativamente às técnicas de tolerância a faltas, a mais utilizada para aumentar a resiliência de sistemas é a redundância. Redundância pode ser aplicada tanto a hardware como a software e consiste em fornecer múltiplas alternativas a um sistema para o cumprimento de uma função, reduzindo assim a probabilidade de falha do sistema. É um facto que a utilização de redundância aumenta drasticamente a resiliência de um sistema. Contudo, a mesma também aumenta: os custos, o tempo de desenvolvimento, a complexidade, os custos de manutenção e o seu tamanho [3]. Na literatura de setores onde o fator custo não é uma limitação, existem um conjunto de arquiteturas altamente sofisticadas e resilientes [4] .

Apesar da utilização de técnicas de tolerância a faltas e de boas práticas de desenho aumentar a resiliência dos sistemas, este aumento não é objetivamente quantificável. Tradicionalmente, técnicas de modelação de resiliência e testes acelerados são utilizados para quantificar a resiliência de um sistema [1], [2], [5], [6].

A modelação de resiliência é uma técnica analítica que permite estimar a probabilidade de falha de um sistema, com base na probabilidade de falha dos seus componentes e das suas interligações. Esta, é usualmente utilizada em paralelo com o desenho, possibilitando a comparação entre arquiteturas e auxiliando a escolha de componentes.

Testes acelerados são técnicas empíricas, os quais, através do envelhecimento acelerado e da recolha de dados de N sistemas, permitem estimar a resiliência e obter uma distribuição de falhas de um sistema. O envelhecimento acelerado é alcançado à custa do uso de fatores de aceleração, fatores estes que consistem na utilização de condições de operação, como temperatura e humidade, mais exigentes do que aquelas a que o sistema está sujeito durante a sua operação normal.

Atualmente, arquiteturas cada vez mais complexas e resilientes, bem como componentes com maior qualidade e resiliência, têm sido utilizados para aumentar a longevidade dos sistemas. Apesar disto, testes acelerados são utilizados à décadas para estimar e testar a resiliência dos sistemas [7], [8].

### 1.1 Motivação e Objetivos

A introdução da condução autónoma no setor automóvel, aumentou a necessidade de sistemas E/E que a suportem. Neste sentido, sistemas tipicamente mecânicos têm vindo a ser substituídos por sistemas E/E, os sistemas *x-by-Wire* (XbW) como o *steer-by-wire* (SbW), o *throttle-by-wire* (TbW) e o *break-by-wire* (BbW) são alguns exemplos desta tendência. Uma vez que a falha destes sistemas pode ter como consequência a perda do controlo do veículo, e consequentemente perdas monetárias, ou até mesmo a perda de vidas humanas, a necessidade por sistemas e subsistemas resilientes têm aumentado nos últimos anos neste setor. Sensores automóvel como o *steering angle sensor* (SAS), atuadores e sistemas de controlo com requisitos de resiliência são alguns exemplos de sistemas necessários neste setor [9].

A literatura de sistemas resilientes para setores, onde o custo do sistema não é uma limitação, apresenta um conjunto de arquiteturas com baixa probabilidade de falha [4]. Porém, no setor automóvel o baixo custo é um dos requisitos dos sistemas. Assim, a utilização de arquiteturas sugeridas pela literatura no contexto do setor automóvel apresenta um desafio.

Outro aspeto interessante e abordado nesta dissertação, são os métodos de estimação de resiliência, os quais são utilizados à décadas, apesar da evolução da resiliência e complexidade das arquiteturas.

Modelações de resiliência necessitam de uma distribuição que caraterize as falhas dos componentes de um sistema e, deste modo, realizar projeções fiáveis sobre a resiliência de um sistema.

Testes acelerados utilizam condições de operação mais exigentes que aquelas a que o sistema está sujeito durante a sua normal operação, de modo a reduzir o tempo de teste. Estes testes são muito utilizados para determinar a distribuição que carateriza a vida de um sistema durante o período de garantia. Porém, é desconhecida a eficiência da sua utilização para estimar sistemas com uma vida superior a 10 ou 15 anos, num período que não comprometa o *time-to-market* do projeto.

Esta dissertação tem como principal objetivo estudar a eficiência dos métodos tradicionais de estimação de resiliência. Para alcançar este objetivo, estes métodos serão utilizados para estimar a resiliência do hardware de um sensor automóvel, o SAS, o qual será utilizado como caso de estudo desta dissertação.

Inicialmente, será desenvolvida uma arquitetura de hardware resiliente para o SAS com base nas técnicas descritas no estado da arte. Em paralelo com o desenho do caso de estudo, será construído um modelo de resiliência do mesmo, a simulação deste modelo possibilitará uma estimativa da resiliência do desenho de hardware. Para avaliar a fiabilidade da estimativa obtida com a abordagem analítica, será posteriormente obtida uma nova estimativa utilizando uma abordagem empírica, abordagem esta que recorrerá a testes acelerados para mais rapidamente obter a resiliência do caso de estudo.

Para possibilitar a realização dos testes acelerados ao caso de estudo, será desenvolvido um *setup* para testes *online*. Este *setup* irá permitir realizar testes acelerados, recorrendo a temperatura como fator de aceleração, e também recolher as falhas de protótipos ao longo do teste.

### 1.2 Estrutura da Dissertação

Este documento começa por apresentar uma breve introdução sobre sistemas resilientes e pela definição dos objetivos deste trabalho, ambos são realizados neste capítulo. De seguida, o capítulo 2 apresenta uma introdução aos fundamentos teóricos e aos conceitos que suportam este trabalho. Este capítulo começa por introduzir sistemas embebidos e sistemas confiáveis, passando depois a abordar uma das propriedades de sistemas confiáveis, a resiliência. Dentro de sistemas resilientes, são apresentadas algumas técnicas utilizadas para alcançar uma baixa probabilidade de falha e são introduzidos os métodos tradicionais para estimar a resiliência de um sistema.

O capítulo 3 começa por apresentar os métodos tradicionais que serão utilizados para estimar a resiliência do caso de estudo, bem como estes métodos irão ser utilizados ao longo do desenvolvimento do caso de estudo. Ainda dentro deste capítulo, são apresentados o modelo de resiliência do caso de estudo e o *setup* que irá suportar a realização dos testes acelerados.

O capítulo 4 apresenta o desenvolvimento do caso de estudo. Este capítulo começa por introduzir a problemática relacionada com o caso de estudo, passando depois para os seus requisitos e o seu desenvolvimento. No final deste capítulo são apresentados os resultados da simulação do modelo de resiliência do caso de estudo e dos testes acelerados.

Finalmente, o capítulo 5 apresenta as conclusões retiradas da aplicação dos métodos tradicionais de estimação de resiliência e sugestões de melhoria ao trabalho desenvolvido.

# Capítulo 2

### Estado da Arte

### 2.1 Sistemas Embebidos

Atualmente, sistemas embebidos apresentam uma vasta variedade de aplicações em diferentes setores, tais como: consumidor final, indústria aeroespacial, indústria médica, militar, aeronáutica e automação industrial. No caso do consumidor final, estes sistemas estão completamente diluídos no seu quotidiano, assumindo diversos tamanhos e formatos. Os *smartphones*, *smartwatches*, MP3, detetores de incêndio e os alarmes, são exemplos de sistemas embebidos que são utilizados diariamente por todos nós.

Apesar de não existir uma definição clara de sistemas embebidos, usualmente, estes são descritos como sendo sistemas constituídos por hardware, software, e por vezes partes mecânicas, os quais são desenhados com o propósito de uma aplicação específica [10]. Sistemas embebidos interagem com o mundo através de sensores e atuadores, e possuem interfaces dedicadas com o utilizador. Dependendo da aplicação, estes sistemas podem possuir requisitos como pouco peso, baixo consumo energético, pequenas dimensões, tempo real, elevado desempenho e confiabilidade. Devido à grande diversidade de aplicações, o hardware e software destes sistemas é desenhado em função da necessidade de cada aplicação. Normalmente, o desenho de hardware e software ocorre em paralelo e é realizado por equipas diferentes.

Sistemas embebidos também podem possuir requisitos de tempo real, os quais representam uma classe diferente de sistemas embebidos. Estes possuem restrições temporais, ou seja, o correto cumprimento da sua funcionalidade está também relacionado com o tempo que demoram a responder a um estímulo. Esta classe de sistemas pode ser dividida em *soft real-time systems* e *hard real-time systems*. Os segundos distinguem-se dos primeiros, pois apresentam consequências muito mais severas, no caso do incumprimento das suas restrições temporais.

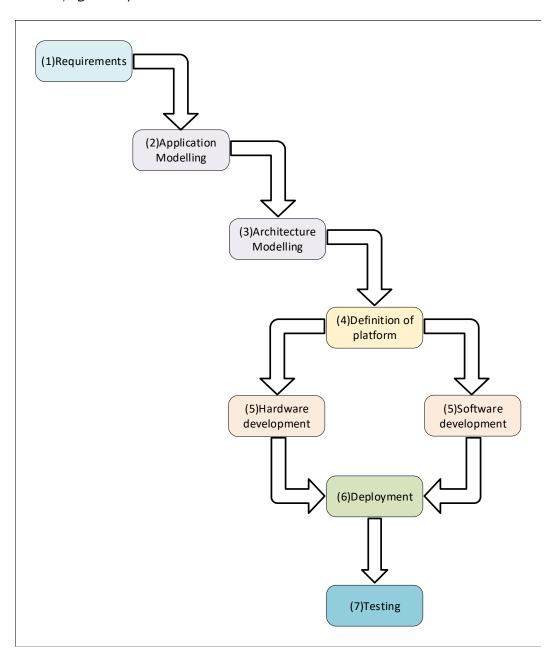

### 2.1.1 Fases do Desenvolvimento de um Sistema Embebido

Usualmente, o desenvolvimento de um novo sistema embebido passa por diversas fases até ser alcançado um produto final. Este desenvolvimento nem sempre é um processo direto, sendo por vezes necessárias várias reiterações até que seja alcançado um protótipo. A figura 2.1 apresenta as diferentes fases do desenvolvimento de um sistema embebido. Para gerir as diversas fases do desenvolvimento de um sistema embebido, são utilizadas metodologias como o *Waterfall, Agile* ou *Spider*.

Figura 2.1: Fases do desenvolvimento de um sistema embebido.

No desenvolvimento de um sistema embebido, inicialmente, são recolhidos os requisitos funcionais e não funcionais, e as restrições do sistema a desenvolver. Após uma redefinição destes requisitos, é desenhado um conceito do sistema. Para avaliar como o conceito desenhado irá cumprir os requisitos do sistema, as suas tarefas são conceptualizadas em software, sendo este software utilizado validar o conceito desenvolvido.

Depois de validado o conceito do sistema, é iniciada a modelação da arquitetura do sistema. Nesta etapa, são identificados os diversos subsistemas que irão auxiliar a arquitetura a alcançar os seus requisitos, por exemplo: microcontrolador, conversor analógico-digital (ADC), CAN transceiver, etc. Durante a definição da arquitetura ainda não são conhecidos os constituintes de cada um dos subsistemas utilizados na arquitetura. O comportamento da arquitetura conceptualizada, pode ser modulado através de máquina de estados finitas (FSM), as quais podem ser simuladas recorrendo por exemplo a uma abordagem software-only. Nesta abordagem, as FSMs são implementadas recorrendo a software, tendo os seus estados e as suas transições validadas. O software utilizado nesta abordagem, pode posteriormente ser utilizado na versão final.

Após a modelação e validação da arquitetura do sistema, é iniciada a alocação dos recursos em software e hardware, e escolhida a plataforma alvo. A decisão de desenhar uma nova plataforma, especificamente moldada para o sistema, ou a utilização de recursos *commercial off-the-shelf* (COTS) é um compromisso entre o tempo de desenvolvimento, e os recursos financeiros disponibilizados para o projeto. Dependendo da decisão, diferentes recursos serão alocados em hardware e software. Com a alocação dos recursos concluída, é iniciado o desenvolvimento desacoplado de hardware e software, significando isto que tanto software como hardware serão desenvolvidos em paralelo. No desenho de software, é definida a arquitetura, as interfaces, as classes e os módulos que suportam a aplicação, sendo esta aplicação ser validada através do uso de *development kit*.

No desenvolvimento de hardware, inicialmente, é definida uma arquitetura e são escolhidos os seus componentes. Dependendo da complexidade da arquitetura e do tempo de desenvolvimento, pode ser optado por: (1) Inicialmente, apenas desenhar uma extensão para uma plataforma já existente, a qual permita validar a arquitetura conceptualizada para o hardware; (2) Desenhar a plataforma de hardware específica para o sistema. Após esta decisão é iniciado o desenho dos circuitos.

No desenho de circuitos, simuladores de circuitos como o LTspice ou TINA podem ser utilizados para validar os circuitos desenhados. Após ser alcançada uma versão estável do esquemáticos, é iniciado o desenho do *layout* do circuito/sistema. Depois da implementação e fabrico do hardware, o mesmo deve ser testado, antes do *deployment* da versão final de software e dos testes globais do sistema.

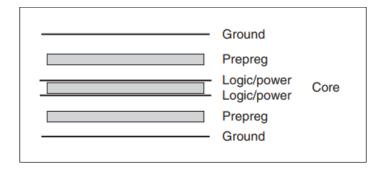

#### 2.1.2 Desenho de PCBs

Inicialmente, as primeiras *boards* eram similares às *protoboards*, nas quais eram utilizados apenas componentes *through-hole*. Estes componentes eram interligados recorrendo a pistas de solda, ou então, quando o número de conexões tornava o uso de pistas impossível, através de fios. Apesar de alguns problemas relacionados com *cross talk* entre sinais e com *overshoot*, esta abordagem funcionava devido às baixas frequências utilizadas pelos componentes. Em consequência da evolução da tecnologia do processo de fabrico de circuitos integrados (IC), aumento das frequências de *clock* e do número de pinos, esta abordagem tornou-se obsoleta, surgindo assim as *multilayer boards* [11].

Uma *multilayer board* é constituída por uma camada de dielétrico (core), por diversas camadas condutoras (*layers*), e por camadas de um material conhecido como *prepreg* [11]. A figura 2.2, retirada de [11], ilustra as diferentes camadas de uma *board* com quatro *layers*. As *layers*, permitem gravar caminhos de cobre (*traces*), os quais interligam os componentes. Além disto, para interligar as *traces* e os pinos dos componentes (*surface-mount technology* (SMT)), através de soldadura, são gravados *pads* nas *layers*. As camadas de *prepreg*, quando submetidas a temperatura e pressão, "colam"às camadas condutoras, mantendo assim um espaçamento entre *layers* e evitando curto-circuitos.

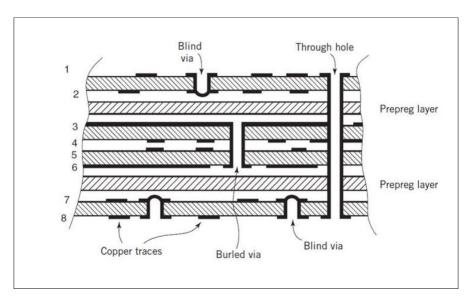

Figura 2.2: PCB com quatro layers.

Para interligar as diferentes *layers*, são utilizadas *vias*, as quais são furos preenchidos por cobre (condutor). *Through-hole vias*, podem ser utilizadas para atravessar todas as *layers* da *printed* PCB e conectar diversas *layers*. Apesar desta abordagem poder à primeira vista parecer a mais lógica, por vezes, é apenas necessário conectar duas ou três *layers*, podendo ser utilizadas *buried vias* ou *blind vias*. *Buried vias* são utilizadas para conectar uma ou mais *layers* interiores, enquanto *blind vias* são utilizadas para conectar a *bottom layer* ou *top layer* a uma camada interior. A utilização de *buried vias* ou *blind vias* ao invés de *through-hole vias*, reduz o acoplamento entre os campos gerados pelos sinais que percorrem as *vias* e as *layers* da PCB. A figura 2.3, retirada de [11], ilustra os diferentes tipos de *vias*.

Figura 2.3: Multilayer PCB.

Durante os últimos anos, o tamanho do transístor tem vindo a reduzir, o que deixou espaço para aumentar o número de funcionalidades que cada circuito integrado (IC) pode realizar, consequentemente levando ao aumento do número de transístores e comutações nos ICs [11]. O aumento do número de funcionalidades, levou a um aumento do número de pinos de cada *IC*, o que do ponto de vista da PCB, significa um aumento do número de *traces* e dos possíveis cruzamentos entre *traces*. Em resposta ao aumento do número de *traces*, a largura das mesmas tem vindo a reduzir, bem como o espaço entre elas, e o número de *layers* têm vindo a aumentar, sendo possível recorrer a PCBs com 70 *layers* [11], [12].

O aumento do número de transístores levou a um aumento do número de comutações, e o aumento da frequência de comutação levou a uma redução do *rise* e *fall time* do sinais. Isto, juntamente com a redução na distância entre *traces*, levaram a um aumento do *cross talk* e da

radiação eletromagnética emitida pelas *traces* que interconectam estes sinais [11]. Além disto, o maior número de comutações em consequência do maior número de transístores e o maior declive na comutação dos sinais levaram a uma maior necessidade de energia. Se esta energia não estiver imediatamente disponível, provoca oscilações nos *traces* da tensões de alimentação dos ICs.

A introdução de um plano de massa, para frequências acima dos 100KHz, demonstrouse uma solução muito útil para confinar campos elétricos e reduzir problemas de impedâncias [11]. O uso destes planos para intercalar *layers* de sinal ou *layers* de alimentação e sinal, é uma das principais técnicas para assegurar a compatibilidade eletromagnética (EMC) no desenho de PCBs. Apesar disto, a utilização do plano de massa para PCBs de duas *layers* pode acarretar problemas. Quando nestas PCBs existe *routing* em ambas as *layers*, não é possível desenhar um plano de massa sem descontinuidades, levando a variações na impedância do plano de massa, ao longo da PCB. Desta forma, só é possível tirar total partido da utilização de um plano de massa para PCBs com um número de *layers* superior a duas.

Tal como o plano de massa, a utilização de "planos de tensão de alimentação" também apresenta mais valias para a PCB. Esta abordagem em conjunto com o plano de massa, funciona como um condensador de *decouple*, impedindo que ruído se propague entre circuitos através das *traces* de tensões de alimentação dos ICs. Além disto, a utilização de "planos de tensão de alimentação" encurta o caminho de retorno, que por sua vez aumenta a EMC da PCB. Quando não existe a possibilidade de utilizar planos de alimentação em conjunto com planos de massa, é preferível a utilização de um plano de massa [13].

Como anteriormente referido, a utilização de planos de massa sem descontinuidades em PCBs de duas *layers* nem sempre é possível. Apesar disto, existem algumas boas práticas que podem ser utilizadas nestas PCBs para aumentar a sua EMC [11].

Para minimizar o acoplamento entre *traces*, deve ser evitado o uso de *traces* adjacentes em paralelo. Caso não seja possível, estas devem existir *traces* de massa intercaladas. Outra boa prática, é a colocação de condensadores de *decouple* e de ilhas de massa e de *power* junto dos ICs. Esta prática ajuda a minimizar o efeito das comutações dos transístores nas linhas de alimentação.

Além do já mencionado, normalmente PCBs trocam energia com outras PCBs. Estes sinais que viajam entre PCBs, estão sujeitos a EMIs provocadas por campos oriundos de fontes de

alimentação e transmissores radiofrequência (RF) ou televisão. Estes campos provocam tanto o aparecimento de ruído de modo comum, como de ruído normal. Caso este ruído não seja removido à entrada, o mesmo irá afetar a EMC da PCB. Ruído de modo comum acontece quando um campo afeta de igual forma um par de sinais balanceados ( $V_1$  e  $G_1$ ,  $S_1^+$  e  $S_1^-$ ), enquanto ruído normal acontece quando campos afetam de forma diferente os pares de sinais [11]. Uma boa estratégia para resolver estes problemas é a utilização de isolamento galvânico. Acoplamento capacitivo, ótico ou indutivo podem ser utilizados para isolar sinais digitais, enquanto o acoplamento indutivo pode ser utilizado para isolar alimentações. Além disto, o uso de filtros também é uma boa solução. Filtros passo-baixo e passa-banda podem ser utilizados para remover ruído normal, enquanto *common mode chokes* e amplificadores diferenciais podem ser utilizados para remover ruído de modo comum.

### 2.2 Sistemas Resilientes

Nos últimos anos, o rápido crescimento da complexidade dos sistemas e o aumento de custos associados com a sua perda de funcionalidade, revelaram a importância de aspetos ligados à resiliência dos sistemas [2]. Usualmente, a resiliência de um sistema é expressada através da probabilidade de um sistema executar a sua função (R), em determinadas condições de operação, e durante um período específico.

A resiliência de um sistema é um atributo expetável em qualquer aplicação, sendo que, o consumidor final espera que um produto não deixe de cumprir a sua função, durante o tempo garantido pelo fabricante. Todavia, em alguns casos o não funcionamento de um sistema pode ter consequências mais severas. Um exemplo é a falha de um subsistema de uma sonda espacial, que ao deixar de cumprir a sua funcionalidade está a comprometer o sucesso da missão desta sonda. O incumprimento da missão por parte da sonda, compromete longos períodos de desenvolvimento e elevados custos monetários. Outro exemplo é a falha de um subsistema de um avião, o qual por não ser capaz de cumprir a sua funcionalidade pode colocar em risco a vida dos passageiros. Os dois últimos exemplos apresentados, são classificados como sistemas críticos.

Sistemas críticos podem ser divididos em duas classes, *mission critical systems* e *safety critical systems* [14], [15]. *Mission critical systems* são sistemas onde o seu não funcionamento

ou o seu mau funcionamento podem comprometer o sucesso de uma tarefa que é crucial para uma missão. *Safety critical systems* são sistemas onde o seu não funcionamento, ou o seu mau funcionamento podem causar danos físicos ao utilizador, ou a quem o rodeia.

No contexto do setor automóvel, a classificação *Automotive Safety Integrity Level* (ASIL) é fornecida pelo *standard* ISO 26262 para classificar a criticidade de um sistema automóvel [15]. Esta classificação tem por base uma análise de riscos e eventos de perigo para o utilizador, definida pela ISO 26262, a qual assenta em três pilares [16]:

- Severity (S) Define a gravidade dos danos para a vida das pessoas, em que S1 diz respeito ao grau mais leve de lesões e o S3 ao pior grau.

- Exposure (E) Determina o risco de exposição a uma situação perigosa, em que E1 representa a probabilidade de exposição mais baixa e E4 representa a probabilidade de exposição mais alta.

- Controllability (C) Explora o grau de controlo do condutor sobre o veículo em caso de falha de algum sistema, a menor perda de controlo sobre o veículo é dado por C1 e a maior perda por C3.

A classificação ASIL tem quatro estágios, ASIL A, ASIL B, ASIL C e ASIL D, sendo que o ASIL D representa o nível mais alto de criticidade.

#### 2.2.1 Faltas, Erros e Falhas

A falta é uma condição anormal que pode causar a falha de um elemento [17]. Tipicamente faltas causam erros, os quais correspondem à diferença entre o valor medido e o valor real [17]. A propagação do erro leva à falha do sistema. A falha de um sistema é a não execução, ou a execução errada, da sua funcionalidade [17]. Dependendo do ponto de vista, faltas, erros e falhas podem possuir significados diferentes. Por exemplo, do ponto de vista do sistema, uma falta é uma falha num componente, sendo ele hardware ou software, o qual leva ao aparecimento dum erro no sistema, este erro por sua vez pode causar a falha do sistema.

Faltas podem ser classificadas de acordo com diferentes critérios. Segundo [17], a origem das faltas podem ser resumidas em três grandes grupos: faltas de desenvolvimento, faltas físicas e faltas de interação. Faltas de desenvolvimento englobam todas as faltas introduzidas

durante o desenvolvimento do sistema, por exemplo: faltas introduzidas na especificação, faltas de desenho, etc. Faltas físicas englobam todas as faltas que afetam o hardware, por exemplo: defeitos introduzidos no fabrico, envelhecimento dos componentes, etc. Faltas de interação englobam todas as faltas causadas por fatores externos, por exemplo: condições de operação, utilizador, etc.

Relativamente às faltas que afetam o hardware, as mesmas podem apresentar diferentes durações. Dependendo da sua duração, as faltas de hardware podem ser classificadas como faltas permanentes, temporárias, ou intermitentes [18]. Faltas temporárias ficam ativas durante pequenos períodos de tempo. Estas faltas tornam-se intermitentes quando apresentam um caráter repetitivo. Faltas permanentes mantêm-se ativas até que ações sejam tomadas.

### 2.2.2 Distribuição de Falhas

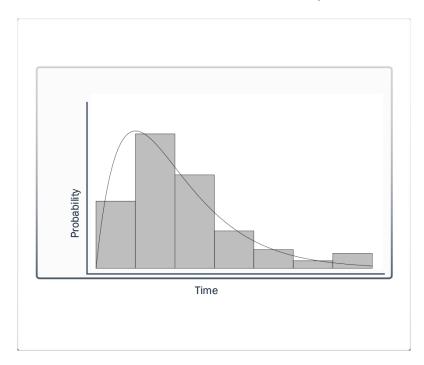

Usualmente em sistemas resilientes, são utilizadas funções para descrever as probabilidades de falha de uma amostra de sistemas durante um determinado período de funcionamento. A

Figura 2.4: Exemplo de uma função PDF.

função densidade de probabilidade (PDF) (t) é uma representação contínua, que demonstra como a probabilidade de falha de uma amostra de sistemas ou componentes está distribuída no tempo [19]. Esta função pode ser obtida através dos resultados de testes acelerados, ou de simulações

de uma dada população. A figura 2.4 ilustra um exemplo de uma função PDF. A função PDF tem de respeitar a seguinte condição:

$$\int_{0}^{\infty} PDF(t)dt = 1 \tag{2.1}$$

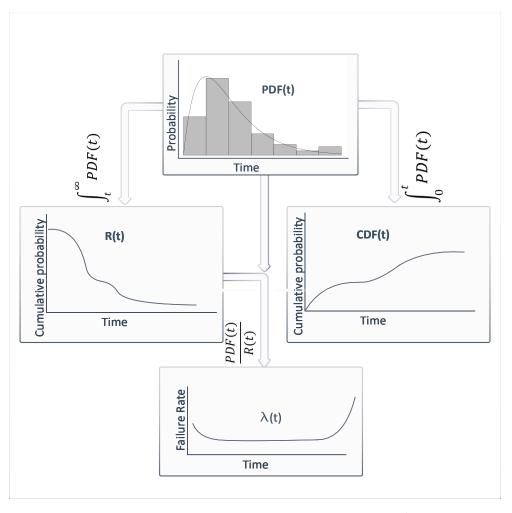

A partir da função PDF é possível calcular as funções distribuição de probabilidade acumulada (CDF) (t) e a função resiliência (R) (t). A partir das funções PDF (t) e R (t) é possível calcular a função  $\lambda$  (t) [19]. A figura 2.5 ilustra as relações entre estas funções.

Figura 2.5: Relação entre as funções PDF (t), CDF (t), R (t) e  $\lambda$  (t).

A função CDF (t) exprime a não resiliência ou a probabilidade de falha acumulada de uma amostra de sistemas ou componentes ao longo do tempo [19]. Enquanto, a função R (t) exprime a resiliência ou a probabilidade acumulada de sobrevivência, de uma amostra de sistemas ou componentes ao longo do tempo [19]. Por último, a função taxa de falha ( $\lambda$ ) (t), também conhecida como curva da banheira, exprime a evolução da taxa de falha de uma amostra de sistemas

ou componentes ao longo do tempo [19].

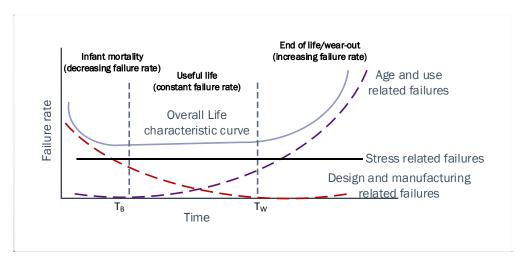

#### Curva da Banheira

Usualmente a função  $\lambda$ (t) dos componentes ou sistemas, durante a sua vida, segue o formato de uma curva da banheira. Esta curva, tipicamente apresenta 3 fases : mortalidade infantil, vida útil e desgaste ou mortalidade senil [1], [2]. Um exemplo desta curva pode ser visualizado na figura 2.6.

Figura 2.6: Curva da banheira.

A primeira fase é caraterizada por uma elevado  $\lambda$ , decrescendo à medida que o tempo avança. O elevado número de falhas nesta fase (falhas prematuras) deve-se principalmente a faltas de desenho, imperfeições nos componentes e a defeitos de fabrico.

Para mitigar as imperfeições nos componentes, uma boa prática é a escolha de componentes certificados. Componentes com certificados, por exemplo *Automotive Electronics Council* (AEC), *Military Performance Specification* (MIL-PRF) e *Aerospace Qualified Electronic Component* (AQEC) são testados de acordo com *standards*, garantindo um determinado nível de resiliência e qualidade. Alguns exemplos de *standards* são [20], [21], [22]: (1) AEC-Q10x e AEC-Q200-00x, no caso da indústria automóvel; (2) MIL-PRF 38535, no caso do setor militar; (3) AQEC, no caso do setor aeroespacial.

Outra forma de reduzir as imperfeições nos componentes, defeitos de fabrico, e as faltas de desenvolvimento, é através testes acelerados. A utilização de testes qualitativos pretende avaliar de que forma o sistema falha, com o intuito de determinar as possíveis causas destas falhas e corrigi-las através de uma nova reiteração do desenho ou através da melhoria do processo de

fabrico. Quando já não é possível eliminar faltas através do redesenho, estes testes podem ser utilizados para envelhecer o sistema, fazendo com que este avance para a fase seguinte da curva da banheira [1], [23].

A segunda fase é caraterizada por um  $\lambda$  constante. Nesta fase, usualmente os sistemas falham de forma aleatória, sendo estas falhas causadas, principalmente, por faltas de iteração. Condições de operação como temperatura, vibração, ou radiação causam *stress* nos componentes, o que excessivamente pode levar ao aparecimento de faltas aleatórias. Para prevenir este tipo de faltas, uma boa seleção de componentes é fundamental. Na escolha dos componentes, é necessário tomar em consideração se os limites de operação dos componentes vão de encontro aos limites de operação do sistema. Uma técnica utilizada nesta escolha é o *derating*, a qual consiste em escolher componentes com os limites de operação superiores aos limites do sistema, aumentando assim a sua tolerância ao *stress* causado por estes elementos [2]. Outro fator relacionado com as condições de operação são as descarga electrostática (ESD). Estas podem surgir no sistema com diferentes tempos e com diferentes intensidades causando a falha do hardware. Para prevenir o seu efeito, técnicas como isolamento galvânico podem ser utilizadas para isolar os *inputs* do sistema, ou, para isolar subsistemas, prevenindo assim, a propagação de uma ESD [2].

A terceira fase é caracterizada por um rápido crescimento do  $\lambda$ . Este rápido crescimento deve-se ao desgaste ou envelhecimento dos componentes do sistema. Esta fase de vida do sistema não pode ser evitada, apenas pode ser prevenida pela manutenção. Para prever quando um componente ou sistema irá atingir o seu fim de vida, testes acelerados (quantitativos) ou simulações podem ser utilizadas para determinar a distribuição de falhas do sistema e consequentemente a sua longevidade. Neste sentido, a manutenção deve ser aplicada antes dos componentes ou sistemas atingirem a fase de mortalidade senil [1].

Para descrever o comportamento das falhas das diferentes fases da curva da banheira, são utilizadas diferentes distribuições [1], [24], [25]. Para a mortalidade infantil, são sugeridas as distribuições de gamma, Weibull ou log-normal. Para a vida útil são sugeridas a distribuição exponencial ou de Weibull. Para o desgaste ou mortalidade senil são sugeridas as distribuições de Weibull, gama ou Gauss. Por vezes, para descrever os padrões de falhas de alguns componentes ou sistemas, poderá ser necessário sobrepor distribuições.

### 2.2.3 Taxa de Falha, MTBF and MTTF

A taxa de falha ( $\lambda$ ), o tempo médio entre falhas (MTBF) e o tempo médio até à falha (MTTF), são métricas utilizadas em resiliência. O  $\lambda$  representa a frequência de falhas de uma amostra de sistemas ou componentes, por unidade de tempo, usualmente expresso em horas [1]. O MTBF representa o tempo médio entre falhas de uma amostra de sistemas ou componentes, sendo esta métrica usualmente utilizada para sistemas reparáveis [1]. O MTTF representa o tempo médio até à falha de uma amostra de sistemas ou componentes. Em oposição ao MTBF, o MTTF é utilizado para sistemas não reparáveis [1].

O MTBF e MTTF podem ser obtidos a partir da função PDF do sistema pela equação [24]:

$$MTTF(t) = \int_0^\infty t * PDF(t)dt$$

(2.2)

Na distribuição exponencial o MTBF pode ser calculado a partir do  $\lambda$ , utilizando a equação (2.3) [1]. O valor de MTBF é muito útil para realizar comparações entre componentes, porém, o mesmo não fornece informação suficiente para determinar a longevidade de um componente [26], [27]. Um bom exemplo das limitações apresentadas por este dado estatístico é apresentado em [28]. Neste exemplo, é apresentada uma amostra de 500000 seres humanos com 25 anos de idade. Durante um ano, foram recolhidos dados sobre as falhas (morte) destes seres humanos. Ao longo de um ano, morreram 625 pessoas, o que corresponde a um  $\lambda$  de 0.125%. Como visto anteriormente na distribuição exponencial, o MTBF pode ser obtido a partir do inverso do  $\lambda$ , o que neste caso corresponde a um MTBF de 800 anos. Como é possível constatar, 800 anos não correspondem ao tempo de vida expetável para um ser humano. Tal como neste exemplo, o valor de MTBF não exprime o tempo de vida expetável para um competente, porém componentes com maior MTBF possuem maior resiliência.

$$MTTF = 1/\lambda \tag{2.3}$$

O  $\lambda$  é o valor da função  $\lambda$  (t) para a vida útil do componente ou sistema, o que corresponde ao valor da função  $\lambda$  (t) quando esta é aproximadamente constante [24].

#### 2.2.4 Redundância

Sistemas recorrem a redundância para aumentar a sua probabilidade de sucesso e alcançar a tolerância a faltas. A redundância consiste em fornecer mais do que um meio ao sistema para alcançar uma determinada função [29]. É um facto que a utilização de redundância aumenta drasticamente a resiliência de um sistema. Contudo, a mesma também aumenta: os custos, o tempo de desenvolvimento, a complexidade, os custos de manutenção e o seu tamanho [3]. A utilização de redundância ao nível do sistema pode ser dividido nas 4 seguintes categorias [18], [30]: (1) redundância de hardware; (2) redundância de software; (3) redundância de informação; (4) redundância temporal.

#### Redundância de Hardware

Redundância de hardware consiste na replicação de componentes ou subsistemas, aos quais, o sistema recorre quando as suas contrapartes falham. Esta categoria de redundância tem 3 tipos: estática, dinâmica e híbrida.

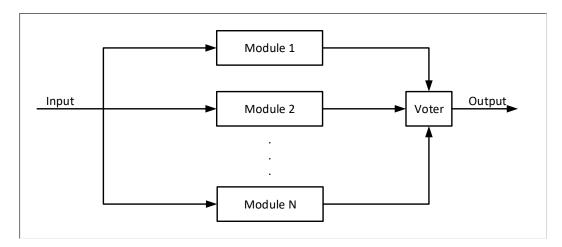

Na redundância estática, quando um componente falha, este é substituído pela sua contraparte, sem que o sistema fique ciente da sua falha (fault-masking). As arquiteturas n-modular redundancy (NMR), figura 2.7, são exemplos da utilização deste tipo de redundância [31]. Neste exemplo, uma arquitetura é constituída por N módulos redundantes, e por um único voter. O voter arbitra a saída dos módulos redundantes. Como esta arquitetura apresenta apenas um voter, o mesmo representa um ponto único de falha. Porém, a complexidade do voter é menor do que a dos restantes módulos, possibilitando que o ponto único de falha seja tolerado. O número de faltas que uma arquitetura NMR pode tolerar segue a equação N=2k+1, em que N representa o número de módulos redundantes e K o número de faltas.

Na redundância ativa ou dinâmica, inicialmente, as faltas são identificadas e localizadas, e posteriormente o sistema é reconfigurado de forma a retomar a sua operacionalidade. Exemplos de arquiteturas que exploram o uso de redundância ativa temos: *duplication with comparison* e *standby*.

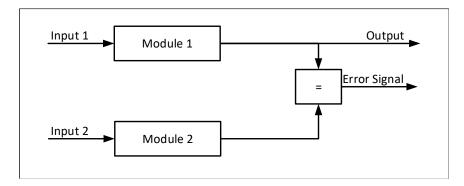

A figura 2.8 apresenta uma arquitetura *duplication with comparison* [18]. Esta arquitetura é constituída por dois módulos redundantes. O resultado de ambos os módulos é avaliado por um comparador, e em caso de discrepâncias é gerado um sinal de erro. Esta arquitetura possibilita a deteção de erros, porém, a mesma não permite a recuperação de faltas.

Figura 2.7: Arquitetura NMR.

Figura 2.8: Arquitetura *Duplication with comparison*.

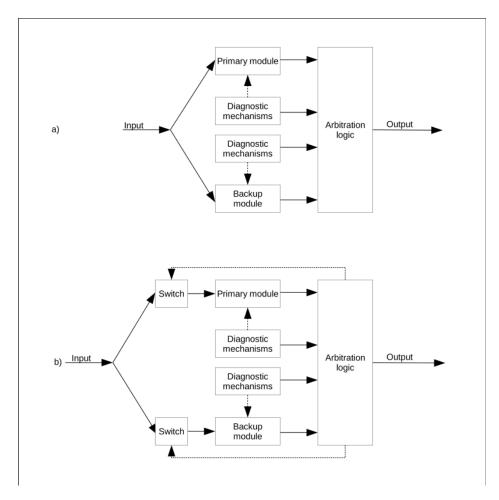

Relativamente às arquiteturas *standby*, as mesmas utilizam os módulos redundantes como *backup*. Na figura 2.9, retirada de [31], é possível visualizar dois exemplos [31]. Cada uma das arquiteturas dos exemplos é constituída por um módulo primário e um de *backup*. Ambos os módulos são monitorizados pelos módulos de diagnóstico de faltas. Caso surja uma falta, os módulos de diagnóstico reportam ao módulo de lógica arbitral.

No exemplo a), ambos os módulos, primário e *backup*, encontram-se em operação, em caso de falha de um módulo, o módulo de lógica arbitral desativa o módulo em falha (*hot standby*). No exemplo b), apenas o módulo primário encontra-se em funcionamento, em caso de falha, este módulo é desativado pelo módulo de lógica arbitral, sendo substituído pelo módulo de *backup* (*cold standby*). Pelo facto da arquitetura (*cold standby*) apenas ativar o módulo de *backup* em caso de falha do primário, a mesma reduz o desgaste causado ao módulo de *backup*, e o consumo energético do sistema. Contudo, para ativar o módulo de *backup* é necessário reconfigurar o sistema, sendo que durante esse período o mesmo está inoperacional. Estas arquiteturas podem tolerar até N-1 faltas, em que N é o número de módulos redundantes.

Figura 2.9: Exemplos de arquiteturas que exploram redundância dinâmica, a) *hot standby*, b) *cold standby*

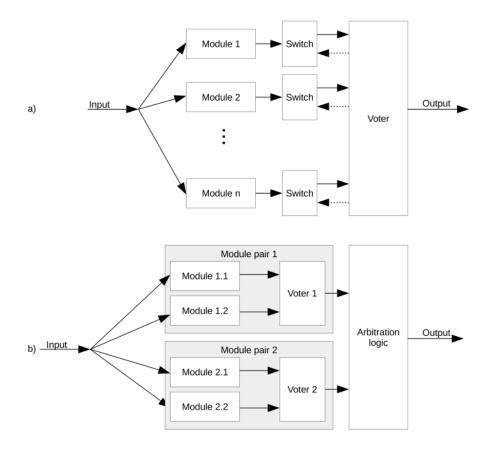

A redundância híbrida combina a utilização de redundância estática e dinâmica, tirando partido das vantagens de cada uma. Na ocorrência de uma falta, para prevenir erros momentâneos, técnicas de redundância passiva são utilizadas para mascarar faltas. Recorrendo a técnicas de redundância ativa, as faltas são localizadas e removidas, e o sistema é reconfigurado, retomando assim a sua operacionalidade. As arquiteturas *self-purging* e *duo-duplex* são exemplos de arquiteturas que exploram o uso deste tipo de redundância, figura 2.10 ([31]).

A arquitetura *self-purging* é uma arquitetura NMR, à qual são acrescentados interruptores. Estes permitem desativar os módulo redundantes. Dependendo do resultado da votação, o *voter* desativa o módulo em falha, e reconfigura-se diminuindo o número de entradas. Esta arquitetura pode tolerar até N-2 faltas, sendo que N representa o número de módulos redundantes.

A arquitetura *duo-duplex* é baseada na arquitetura *hot standby*, porém os mecanismos de deteção de faltas são substituídos por dois *duo-duplex*. Cada *duo-duplex* é constituído por dois

Figura 2.10: Exemplos de arquiteturas que exploram redundância híbrida, a) self-purging, b) duo-duplex

módulos redundantes, e um *voter*. A comparação das saídas de ambos os módulos redundantes, permite ao *voter* identificar faltas. Inicialmente, tal como na arquitetura *hot standby*, apenas, o módulo primário está ativo. No caso de ser detetada uma falta, o mó dulo de lógica arbitral desativa o *duo-duplex* primário, sendo substituído pelo *duo-duplex* de *backup*. Comparando esta arquitetura com a arquitetura *hot standby*, esta arquitetura apresenta mecanismos de deteção de faltas mais simples, contudo, a mesma necessita de um número maior de módulos. Arquiteturas *duo-duplex* podem apenas tolerar uma falta.

#### Redundância de Software

Redundância de software apresenta dois tipos de técnicas: *single version* ou *multi version*. As técnicas *single version* pretendem aumentar a tolerância a faltas de uma versão de software. As técnicas *multi version* recorrem a diferentes versões do mesmo software para alcançar a tolerância a faltas. É importante salientar que ambas as técnicas podem ser aplicadas aos diferentes

níveis do sistema de software [32]: procedimento, processo, aplicação, sistema operativo, etc.

As técnicas *single version* introduzem mecanismos que permitem a deteção, contenção e remoção de erros originados por faltas de desenho. Alguns exemplos de técnicas de tolerância a faltas são [18], [32]: *timing checks, coding checks, partitioning, modularization, error detection, error handling, checkpoint and restart, process pairs* e *data diversity*.

As técnicas *multi version* recorrem a múltiplas versões do mesmo software, executadas em paralelo ou sequência. O princípio de utilização destas técnicas assenta no princípio da diversidade, onde diferentes componentes (diferentes algoritmos), produzidos por diferentes equipas (diferentes ferramentas, diferentes desenhos), falham de forma diferente [32]. As múltiplas versões de software podem ser estruturalmente utilizadas como: (1) alternativas, permitindo meios alternativos para deteção de faltas; (2) pares, permitindo a deteção de faltas através da comparação; (3) em grupos, permitindo mascarar faltas através de votação. Alguns exemplos destas técnicas são [18], [32]: *recovery blocks, N-Version Programming* e *N Self-Checking Programming*.

## Redundância de Informação

A redundância de informação é utilizada como meio para alcançar tolerância a faltas nos dados a transmitir, ou a armazenar. A forma mais comum deste tipo de redundância é a codificação. Esta, através da introdução de *check bits* aos dados possibilita a deteção de faltas e em certos casos a correção de alguns *data bits*. Alguns exemplos de esquemas de codificação usados em redundância de informação são [31]: *parity codes, double-inverted coding, cyclic redundancy check* (CRC)s e *AN-codes*.

#### Redundância Temporal

Redundância temporal consiste na repetição de uma determinada computação, a comparação entre os resultados das diferentes computações permite detetar discrepâncias. A discrepância entre resultados, indica a existência de faltas temporárias. Em relação à redundância de hardware e à redundância de informação, a redundância temporal não necessita da adição de recursos extras, quer lógicos ou físicos. Contudo, a mesma aumenta o tempo necessário para realizar o processamento.

Redundância temporal apenas permite a deteção de faltas temporárias [5], [31]. Na ocorrência de faltas permanentes, as diferentes repetições irão produzir resultados iguais, o que impossibilita a deteção de discrepâncias. Porém, através da combinação de redundância temporal com redundância de informação é possível detetar faltas permanentes. Exemplos de técnicas que combinam redundância de informação com redundância temporal são [18]: *alternating logic, recomputing with shifted operands, recomputing with swapped operands* e *recomputing with duplication with comparison*.

#### Redundância e Diversidade

A utilização do mesmo hardware e software, redundância homogénea, desenvolvido pela mesma equipa, pode resultar em faltas de modo comum. Faltas de modo comum são faltas que podem ocorrer em dois ou mais componentes/subsistemas ao mesmo tempo [18]. Para colmatar esta lacuna, surge o termo diversidade que consiste na utilização de diferentes meios, técnicas ou tecnologias, na execução da mesma tarefa [31]. A utilização de diversidade irá prevenir a falha comum dos diversos componentes.

A diversidade pode ser usada em todas as formas de redundância, como redundância de hardware, software, etc, podendo ser classificada como redundância heterogénea. Exemplos de técnicas que fornecem diversidade ao nível do software são [15]: *N-version (Multiversion) programming* e *recovery blocks*. Relativamente à diversidade ao nível do hardware, um possível exemplo é a utilização de sensores diferentes para adquirir a mesma variável, por exemplo diferentes sensores de posição angular (magneto-resistivos e óticos) colocados na mesma localização física.

# 2.2.5 Métodos para Estimar a Resiliência de um Sistema

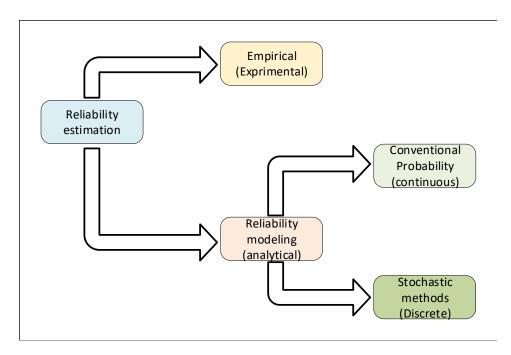

Para estimar a resiliência de um sistema existem duas possíveis abordagens [1], [2], [5], [6]: experimental ou analítica. A figura 2.11 ilustra ambas as opções.

Na abordagem empírica ou experimental, é utilizada uma amostra com N sistemas para recolher dados sobre as falhas destes sistemas. A percentagem de falhas em relação ao número de sistemas permite obter uma indicação sobre a resiliência dum sistema, com uma determinada precisão. Por exemplo, 1000 protótipos de um sistema foram testados durante N horas, onde

Figura 2.11: Modelação e estimação de resiliência.

ocorreram 100 falhas. Deste exemplo é possível concluir que durante N horas de funcionamento, o sistema testado apresenta uma resiliência de 90%.

As desvantagens das abordagens experimentais consistem no tamanho da amostra, na logística necessária para realizar experiências com este tipo de amostras, e na duração que estas experiências podem alcançar. Por exemplo, para estimar a resiliência de um isolador capacitivo a Texas Instruments utilizou uma amostra com 66423 componentes [33]. Nestas experiências, o elevado tamanho das amostras está interligado com a precisão que é pretendida no resultado desta abordagem. Relativamente à duração da experiência, componentes resilientes podem demorar longos períodos de tempo até falharem. Utilizando o exemplo anterior, a amostra foi testada durante 1000 horas sem que nenhuma falha ocorresse. Uma técnica muito utilizada para reduzir o tempo do processo experimental são os testes acelerados, esta técnica é descrita no capítulo 2 (2.2.7).

A abordagem analítica consiste na modelação de um sistema, e no uso de probabilidade de falha de cada um dos seus componente para determinar a probabilidade de falha do sistema. Nesta alternativa, a probabilidade de falha de um sistema depende também da forma como os seus componentes estão interligados. Segundo [6], esta alternativa é útil para auxiliar a escolha de componentes e para fornecer valores quantitativos para comparação entre arquiteturas do estado da arte. Este autor também evidencia que a estimativa obtida a partir desta alternativa

é pouco exata, sendo isto devido à dificuldade de incorporar no modelo do sistema, todos os fatores que levam ao aparecimento de faltas no sistema.

# 2.2.6 Métodos Analíticos: Modelação de Resiliência

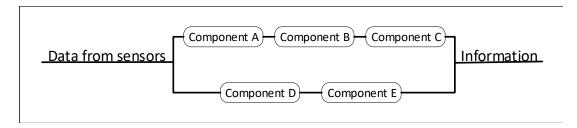

Nesta abordagem, um modelo matemático de resiliência de um sistema é deduzido a partir de um modelo de resiliência de um sistema. O modelo de resiliência de um sistema é um diagrama de blocos, que demonstra as diferentes alternativas que o sistema possui para alcançar a sua função. Cada uma destas alternativas corresponde a uma cadeia de componentes. A figura 2.12 demonstra um exemplo de um modelo de resiliência de um sistema. O modelo matemático de resiliência de um sistema, permite calcular a probabilidade de falha de um sistema, com base nas probabilidades de falha dos seus componentes e das interligação entre estes componentes.

Figura 2.12: Exemplo de um modelo de resiliência do sistema.

Para deduzir o modelo matemático de resiliência de um sistema existem duas alternativas, uma que recorre aos teoremas convencionais de probabilidade e uma que recorre a métodos estocásticos. Relativamente à primeira alternativa, existem 3 métodos que podem ser utilizados para a dedução de um modelo matemático, o primeiro consiste na aplicação direta dos teoremas de probabilidade convencional, a segunda consiste na utilização de tabelas de verdade e a terceira consiste na utilização de diagramas lógicos [1], [29]. Na alternativa que recorre a métodos estocásticos, podem ser utilizados métodos como por exemplo cadeias de Markov ou processos regenerativos, para deduzir um modelo matemático do sistema [2]. Nesta dissertação, apenas serão abordadas as cadeias de Markov e o método de Monte Carlo. Os métodos de Markov podem ser utilizados para sistemas onde a probabilidade de falha dos seus componentes é independente do tempo, ou seja, a mesma é constante. Para sistemas onde a probabilidade de falha dos componentes é independente do tempo, ou a sua complexidade não permite a dedução de um modelo matemático, usualmente, são utilizados métodos de Monte Carlo, também conhecidos como simulações de Monte Carlo.

Nesta secção, inicialmente, serão apresentados os três métodos utilizados para deduzir um modelo matemático recorrendo aos teoremas convencionais de probabilidade, e posteriormente, as cadeias de Markov e o método de Monte Carlo. Os exemplos apresentados para os métodos utilizados para deduzir um modelo matemático recorrendo aos teoremas convencionais de probabilidade, foram retirados de [29].

#### **Probabilidade Convencional**

Neste método, os teoremas convencionais de probabilidade são aplicados diretamente às diferentes configurações dos componentes (séries, paralelos ou séries-paralelos), de forma a sintetizar o modelo matemático de resiliência de um sistema.

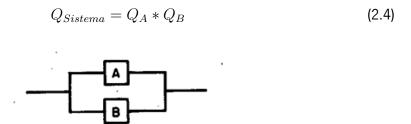

Para um paralelo de dois componentes, figura 2.13, retirada de [29], com probabilidades de falha  $Q_A$  e  $Q_B$ , o sistema falha quando ambos os componentes falharem. A probabilidade de falha do sistema ( $Q_{Sistema}$ ) pode ser calculada a partir da probabilidade de dois eventos arbitrários ocorrerem em simultâneo, equação 2.4.

Figura 2.13: Exemplo de um modelo com dois componentes em Paralelo.

Num sistema composto por dois componentes em série com probabilidades de sucesso  $P_A$  e  $P_B$ , figura 2.14, retirada de [29], o sistema falha quando um dos componentes falhar. A probabilidade de falha do sistema ( $Q_{Sistema}$ ), pode ser calculada a partir da probabilidade de um dos eventos ocorrer, equação 2.5.

$$Q_{Sistema} = 1 - P_{Sistema} = 1 - P_A * P_B$$

(2.5)

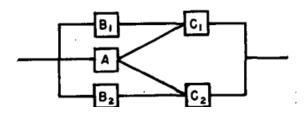

Aumentando a complexidade, para um sistema composto por um conjunto de componentes em série e paralelo, figura 2.15, retirada de [29]. Neste sistema existem 4 alternativas para o sistema atingir o sucesso ( $P_{Sistema}$ ), sendo elas: (1)  $B_1$  e  $C_1$ ; (2)  $B_2$  e  $C_2$ ; (3)  $A_1$  e  $C_1$ ; (4)

Figura 2.14: Exemplo de um modelo com dois componentes em série.

$A_1$  e  $C_2$ . Considerando a probabilidade de sucesso dos componentes  $P_{C1}$ ,  $P_{C2}$ ,  $P_{B1}$ ,  $P_{B2}$ ,  $P_{A}$  e sendo  $P_{C1} = P_{C2}$  e  $P_{B1} = P_{B2}$ , a probabilidade de falha do sistema ( $Q_{Sistema}$ ) pode ser calculada a partir das equações 2.6.

$$Q_{Sistema} = 1 - P_{Sistema}$$

$$P_{Sistema} = P(sucesso\ do\ sistema\ com\ A\ a\ funcionar) * P_A$$

$$+P(sucesso\ do\ sistema\ com\ a\ falha\ do\ componente\ A) * (1 - P_A)$$

$$P(sucesso\ do\ sistema\ com\ A\ a\ funcionar) = (2P_C - P_C^2)$$

$$P(sucesso\ do\ sistema\ com\ a\ falha\ do\ componente\ A) = 2P_B * P_C - (P_B * P_C)^2$$

Figura 2.15: Exemplo de um modelo com configurações série e paralelo.

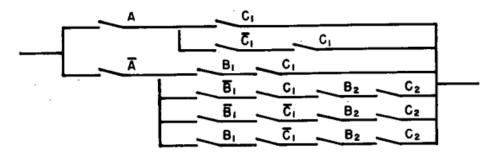

#### Tabela de Verdade

Neste método, uma tabela de verdade é utilizada para sintetizar a resiliência de um sistema. Na aplicação deste método, tal como em qualquer tabela de verdade, inicialmente são preenchidas as combinações possíveis para o número máximo de entradas da tabela de verdade. Neste método, o número máximo de entradas possíveis corresponde a  $2^{NComponentes}$ . A figura 2.16, retirada de [29], representa a tabela de verdade para o exemplo do modelo de resiliência com combinações série e paralelo, apresentado anteriormente. Como é possível visualizar na figura 2.16, cada um das preposições da tabela de verdade corresponde a um componente. O estado de um componente, para uma determinada entrada, corresponde ao valor lógico da preposição para essa entrada.

| Entry No.   | B <sub>1</sub> | В2  | c <sub>1</sub> | c <sub>2</sub> | A     | Success<br>or Failure | PS       |

|-------------|----------------|-----|----------------|----------------|-------|-----------------------|----------|

| 1<br>2<br>3 | 0              | 0   | 0              | 0              | 0     | F                     |          |

| 2           | 0 .            | 0 - | 0              | 0              | 1     | F                     | -        |

|             | 0              | 0   | 0              | 1              | 0     | F                     | -        |

| 4           | 0              | 0   | 0              | , 1            | 1     | S                     | .03888   |

| 5           | 0              | 0   | 1              | 0              | 0     | . F                   | -        |

| 6           | 0              | 0   | 1              | 0              | 1     | S                     | .03888   |

| 7           | 0              | 0   | . 1            | 1              | 0     | F                     | _        |

| 8           | 0              | 0   | 1              | 1 ′            | 1     | . <b>S</b>            | .00972   |

| 9           | 0              | 1   | 0              | 0              | 0     | F                     | -        |

| 10          | 0              | 1   | 0              | 0              | 1     | P                     | -        |

| . 11        | 0              | 1   | 0              | 1              | 0     | S                     | .01008   |

| 12          | 0              | 1   | 0              | 1              | 1     | S                     | .00432   |

| 13          | 0              | 1   | 1              | 0              | 0     | F                     | _        |

| 14          | 0              | 1   | 1              | 0              | 1     | s<br>s                | .00432   |

| 15          | 0              | 1   | 1              | 1              | 0     | S                     | .00252   |

| 16          | 0              | 1   | 1              | 1              | 1     | S                     | .00108   |

| 17          | 1              | 0   | 0              | 0              | 0     | F                     | -        |