### ON-CHIP ARRAY OF THERMOELECTRIC PELTIER MICROCOOLERS

L.M. Goncalves<sup>1</sup>, J.G. Rocha<sup>1</sup>, C. Couto<sup>1</sup>, P. Alpuim<sup>2</sup>, J.H. Correia<sup>1</sup>

<sup>1</sup>University of Minho, Department of Industrial Electronics, Guimarães, Portugal (Tel: +351-253510190, E-mail: lgoncalves@dei.uminho.pt)

<sup>2</sup>University of Minho, Department of Physics, Guimarães, Portugal

**Abstract:** This article reports on the theoretical modelling, the Finite Element Modelling (FEM) simulation, the fabrication process and preliminary results of the first on-chip thermoelectric microcooler array (64 pixels arranged in a 8×8 array), with each pixel independently controlled. This microcooler array uses co-evaporated V–VI compounds of Bi<sub>2</sub>Te<sub>3</sub> and Sb<sub>2</sub>Te<sub>3</sub> as thermoelectric layers, and can be fabricated using planar thin-film technology, lithography and wet etching on top of a silicon wafer, where the CMOS electronic circuits were previously made.

Keywords: Telluride Peltier microcooler array.

# 1. INTRODUCTION

Integration of efficient solid state thermoelectric microdevices with microelectronics is desirable for local cooling and thermoelectric microgeneration [1-3], since they can be used to stabilize the temperature of devices, decrease noise levels and increase operation speed. An array of such devices can also be used for lab-on-chip application.

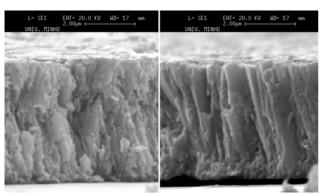

Due to silicon fabrication compatibility, polycrystalline SiGe alloys and polycrystalline Si are commonly used in thermopile applications. Their use in microcoolers has been attempted [4] but the performance is very low compared with that of tellurium compounds, which have been used for many years in conventional large area Peltier devices. Thin films of n-type Bi<sub>2</sub>Te<sub>3</sub> and ptype Sb<sub>2</sub>Te<sub>3</sub> (Figure 6) with absolute value of Seebeck coefficient in the range 150-250 μV.K<sup>-1</sup>, in-plane electrical resistivity of 7-15  $\mu\Omega$ .m, carrier concentration  $3\times10^{19}$ - $20\times10^{19}$  cm<sup>-3</sup> and Hall mobility 80-170 cm<sup>2</sup>.V<sup>-1</sup>.s<sup>-1</sup> were obtained by the authors [5]. The thermoelectric figure of merit (ZT) for these films is near unity for n-type and 0.6 for p-type. These values are comparable to the best found in literature for the bulk materials. It is demonstrated that 15°C cooling bellow room temperature is possible to achieve using such thinfilm materials in microcoolers.

# 2. DESIGN OF MICROCOOLER ARRAY

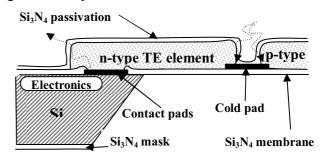

The array of microcooler was designed to accommodate 64 pixels (organized in 8×8 structure) of microcoolers. Each pixel can be controlled independently. Figure 1 represents a single pixel cross section. When a current flows from the n-type thermoelectric element (TE) to the metal cold pad and from this to the p-type TE, heat is absorbed in the metal - TE element junctions, by Peltier effect. The same applies to contact pads on electronics, where heating is generated by Peltier effect.

Figure 1: Drawing of a pixel of the microcooling array (not on scale).

A CMOS microchip was designed, with the electronics to address and control each pixel of the array, memorizing the state of microcooler

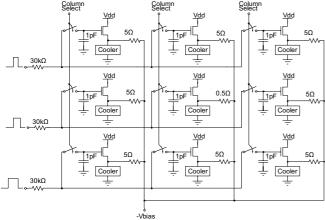

Figure 2 shows the circuit repeated for 9 (of the 64) pixels. Its working principle is the following: For producing the maximum cold, the voltage at the 30 k $\Omega$  resistors must be zero. In this case, the MOSFETs are not conducting and the current

circulates from the coolers trough the  $5\Omega$  resistors to -V<sub>bias</sub>, which must be in the order of 0.5V. The power dissipated in the  $5\Omega$  resistors is below 1mW, which is an acceptable value for the application.

Figure 2: Electronic circuit showing 9 of the 64 pixels of the device.

When a pulse is applied to a  $30k\Omega$  resistor, the 1 pF capacitor selected by the Column selector will charge with a voltage that depends on the width of the pulse. In this case, the corresponding MOSFET will conduct, producing simultaneous phenomena: the current in the  $5\Omega$  and the current in the MOSFET will increase dissipating more power; the current in the cooler will decrease, decreasing cooling. All these will lower the efficiency of the cooler. In this way, it is possible to control each pixel independently.

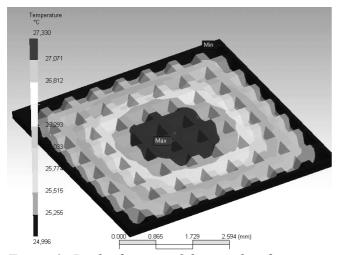

Figure 3: Backside view of the simulated structure that supports the pixels showing that maximal heating is 2.3°C above room temperature, with all pixels turned on at full power.

Figure 3 shows the overall expected heating of the backside of the chip due to the control electronics, Peltier effect and Joule heating. A power dissipation of 1mW was considered in each  $5\Omega$ resistor and a current of 14mA is supplied to each microcooler. A 500 µm thick silicon wafer was used, and the borders of the array were bounded to a fixed temperature of 25°C. A maximum temperature of 27.4 °C was obtained on the silicon wafer.

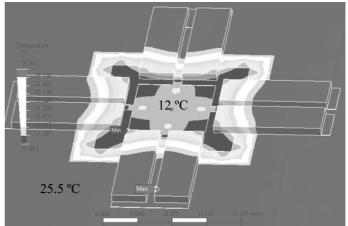

Figure 4: Single pixel microcooler simulation shows the possibility to obtain 15°C of cooling at the centre of the pixel.

FEM simulation was also used to calculate the expected temperature drop on each pixel. A drop of 15°C, bellow room temperature temperature was obtained (Figure 4). To obtain this cooling capacity, a membrane (200 nm thick) of silicon nitride supports 4 pairs of TE elements  $(40\mu m \times 100\mu m \times 10\mu m)$ , powered with 14 mA current. Contact resistivity of  $10^{-10} \Omega \cdot \text{m}^2$  was used on simulations. Radiation and convection was considered on the cooled surface (10 Wm<sup>-2</sup>K<sup>-1</sup>). Thermoelectric properties of n-type and p-type elements were considered as achieved on previous experimental results [5]. Results obtained from FEM simulation on a single pixel microcooler agree with theoretical calculations [8].

### 3. FABRICATION STEPS

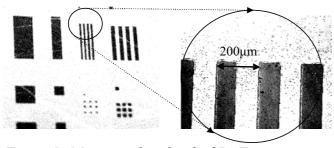

The Si wafer with control electronics is covered with a Si<sub>3</sub>N<sub>4</sub> layer where two vias are opened to access the metallic pads on top that will provide connection to the thermoelectric elements (Figure 1). The n-type thermoelectric material is deposited by co-evaporation [6,7] and patterned by photolithography on top of the wafer (Figure 5). An etchant based on nitric acid can be used to etch telluride films without etching the metal contact pads [9]. Without removing the photoresist used to pattern the n-type material, p-type material is deposited on top of the wafer. This layer is also patterned using photolithography and wet etching on nitric acid based etchant.

Figure 5: Micrographs of etched Bi<sub>2</sub>Te<sub>3</sub> structures

Photoresists are then removed (from n-type and p-type materials) and a passivation layer of Si<sub>3</sub>N<sub>4</sub> is used to avoid degradation of the thermoelectric films in contact with atmospheric oxygen. The last step of fabrication is the etching of the back side of the Si wafer using KOH, to fabricate a membrane of Si<sub>3</sub>N<sub>4</sub> on each pixel, that supports This the microcooler elements. membrane reduction of achieves significant thermal conduction between the cold and the hot sides of the Peltier device. Electronic circuits in the wafer are confined to the regions between the microcoolers to prevent damage during the last KOH fabrication step. Moreover, the back side of the wafer is covered with another patterned Si<sub>3</sub>N<sub>4</sub> layer which will act as a mask during the etch step to release the membrane.

Figure 6: SEM photo of  $Bi_2Te_3$  (left) and  $Sb_2Te_3$  (right) thin films.

### 4. DISCUSSION AND RESULTS

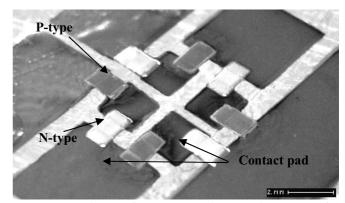

An enlarged microcooler individual pixel was fabricated and tested on top of a polyimide substrate that emulates the  $Si_3N_4$  membrane (Figure 7). The fabrication of these enlarged microcooler (using shadow masks during deposition of thermoelectric materials) allowed a rapid fabrication of a demonstration prototype, without all the steps required to fabricate the microcooler as previous referred. The working principle of the microcooler and the quality of materials were demonstrated and evaluated.

Figure 7: Photo of a microcooler pixel, on top of a polyimide substrate.

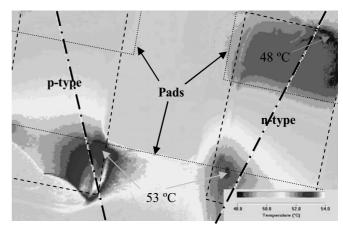

The performance of the microcooler was analyzed by use of a thermal image map generated with an infrared microscope. An image was obtained with a 4 mA current through the device and cold and hot sides are clearly identified (Figure 8).

Figure 8: Thermal image of n-type and p-type thermoelectric elements presented on figure 7, powered with 4mA current, under vacuum.

A temperature difference of 5 °C was measured between the hot and the cold sides, under vacuum. The distance from expected results is due too high contact resistances between metal pads and thermoelectric elements. A contact resistance of  $10^{-6} \,\Omega.\text{m}^2$  was measured. This value is expected to be reduced to less than  $10^{-9} \Omega m^2$  using a layered fabrication process [2]. The high temperature achieved on the hot side of the device results from the low dissipation capability due to the low thermal conductivity of the substrate used in the prototype (polyimide) compared with the substrate used in simulation (silicon covered with silicon nitride). The low thermal conductivity in contact pads also contributes for this higher temperature on the hot side of the device.

## 5. CONCLUSIONS

An array of microcoolers, with 64 pixels, with each pixel controlled independently to cool or heat was designed and simulated, and the respective fabrication process was described. A temperature difference of  $\pm 15^{\circ}$ C could be achieved in each pixel. Thermoelectric thin-films with high figure of merit were obtained by co-evaporation, suitable for fabrication of such microcoolers, and lithographic pattern techniques were applied on these films.

A large area pixel of the microcooler was fabricated and its performance analysed under microscopic infrared imaging. A temperature difference of 5°C was obtained. Differences from expected performance are due to high electrical resistance and low thermal conductance obtained in the pad - thermoelectric material interface. Efforts are being made to reduce contact resistance and fabricate thermoelectric elements with lower dimensions.

## **ACKNOWLEDGMENTS**

This work was supported by ADI (MPYROM) and Portuguese Foundation for Science and Technology (SFRH/BD/18142/2004). First author also would like to thank Gao Min and D.M. Rowe for help in fabrication of thin films and F. Volklein for thermal conductivity measurements.

#### REFERENCES

- [1] Harald Böttner, Joachim Nurnus, et. Al., "New thermoelectric components using microsystem technologies", J. Microelectromechanical Systems, 13, pp. 414-420, 2004.

- [2] Luciana Wasnievski da Silva, Massoud Kaviany, "Fabrication and measured performance of a first-generation microthermoelectric cooler", Journal of MEMS, vol. 14, 5, pp. 1110, 2005.

- [3] G. Jeffrey Snyder, James R. Lim, Chen-Kuo Huang and J.P. Fleurial, "Thermoelectric microdevice fabricated by a MEMS-like electrochemical process", Nature Materials Letters, 2, pp.528-531, 2003.

- [4] Wijngaards D.D.L, S.H. Kong, M. Bartek, R.F. Wolffenbuttel, "Design and fabrication of on-chip integrated polySiGe and polySi Peltier devices", Sensors & actuators A. Physical, 85, pp. 316-323, 2000.

- [5] L.M. Goncalves, C.Couto, J.H. Correia, P.Alpuim, Gao Min and D.M. Rowe, "Optimization of thermoelectric thin-films deposited by co-evaporation on plastic substrates", ECT'06, Cardiff, UK, 2006.

- [6] L.M. Goncalves, C. Couto, J.H. Correia, P. Alpuim, Gao Min, D.M. Rowe, "Flexible thin-film planar Peltier microcooler" Proc. ICT'06, Vienna, Austria, 2006

- [7] L.M. Goncalves, J. G. Rocha, J. H. Correia and C. Couto, "Control of the Deposition Ratio of Bi<sub>2</sub>Te<sub>3</sub> and Sb<sub>2</sub>Te<sub>3</sub> in a Vacuum Evaporator for fabrication of Peltier Elements" Proc. ISIE 2006, Montreal, Canada, 9-13 July, 2006.

- [8] F. Volklein, Gao Min , D.M. Rowe, "Modelling of a microelectromechanical thermoelectric cooler", Sensors and Actuators 75 pp. 95–101, 1999.

- [9] L.M. Goncalves, J.G. Rocha, C. Couto, P. Alpuim, Gao Min, D.M. Rowe and J.H. Correia, "Fabrication of flexible thermoelectric microcoolers using planar thin-film technologies", J. Micromechanics & Microengineering, in press, 2006.