**Universidade do Minho** Escola de Engenharia

André Antunes Oliveira

Multicore Embedded Virtualization Architecture Exploiting ARM TrustZone

**Universidade do Minho** Escola de Engenharia

#### André Antunes Oliveira

# **Multicore Embedded Virtualization Architecture Exploiting ARM TrustZone**

Dissertação de Mestrado em Engenharia Eletrónica Industrial e Computadores

Trabalho efectuado sob a orientação do Professor Doutor Adriano Tavares Professor Doutor Sandro Pinto

## Declaração do Autor

Nome: André Antunes Oliveira

Correio Eletrónico: a65319@alunos.uminho.pt

Cartão de Cidadão: 14243023

Titulo da dissertação: Multicore Embedded Virtualization Architecture Ex-

ploiting ARM TrustZone Ano de conclusão: 2017

Orientador: Professor Doutor Adriano Tavares

Designação do Mestrado: Ciclo de Estudos Integrados Conducentes ao Grau

de Mestre em Engenharia Eletrónica Industrial e Computadores

Área de Especialização: Sistemas Embebidos

Escola de Engenharia

Departamento de Eletrónica Industrial

De acordo com a legislação em vigor, não é permitida a reprodução de qualquer parte desta dissertação.

Universidade do Minho, 27/04/2017

Assinatura: André Antunes Oliveira

## Agradecimentos

Faço uso desta secção da minha dissertação para agradecer a todos os que nela tiveram influência, direta ou indiretamente. Assim como aos que tiveram influência no meu percurso académico que culminou nesta dissertação.

Quero agradecer a todos os meus orientadores, pois sem eles não conseguiria terminar esta dissertação, pelo menos com o mesmo nível.

Ao meu co-orientador, o Professor [e dentro de dias] Doutor Sandro Pinto, queria agradecer a orientação, profissionalismo e ética de trabalho, sempre incontestáveis, fazendo tudo para encontrar tempo para me ajudar. Pelos conhecimentos e principalmente metodologia que me transmitiste, são incalculáveis. A minha vontade de querer sempre fazer bem e fazer melhor foi me transmitida por ti. Além da orientação, nunca hei de esquecer a amizade, o companheirismo, a hospitalidade, as brincadeiras e tudo o mais nas horas em que as mesmas podiam ser feitas. Hás de ser sempre uma pessoa que marcará a minha vida como uma inspiração, um exemplo a seguir, e como uma pessoa extraordinária em todos os aspetos. Todo o meu trabalho nesta dissertação e a minha evolução nos últimos 3 anos, devo-o a ti.

Ao meu orientador, orientador do meu co-orientador, Professor Doutor Adriano Tavares, por me encaminhar na direção certa, ainda que esta parecesse in-alcançável, querendo sempre que trabalhássemos para nós e por nós, para que o nosso nome como engenheiro fosse merecido. Por estar sempre atento às necessidades de cada um de nós apesar de todo o seu trabalho, alunos e projetos sobre a sua orientação.

Um especial obrigado aos meus dois orientadores por me darem a oportunidade de evoluir como pessoa e como futuro engenheiro. A sua colaboração para me orientarem no caminho certo foi certamente o melhor que alguma vez poderia pedir. Agradeço ainda a oportunidade concedida, oportunidade de uma vida, de poder realizar Erasmus na Tailândia, onde a nível pessoal e profissional considero que tive uma evolução brutal.

Aos meus amigos Eduardo Mendes e João "Jony" Silva por todo o apoio demonstrado ao longo destes 6 anos (já são 12 para o Eduardo). Ao Eduardo por conseguir decifrar ou pelo menos tentar o meu pensamento emaranhado e muitas vezes conseguir que este fizesse sentido, até para mim. Pela amizade que muito

aprecio e por todos os conselhos que me deste, que nunca deixes de os dar. Ao Jony pela companhia naquele laboratório até ao nascer do dia seguinte, por me ouvires quando precisava e principalmente pela amizade e companheirismo que nunca hei de esquecer.

À minha namorada, Ana Guimarães, pela paciência que teve de me aturar enquanto trabalhava na dissertação. Por esperar por mim 6 meses, por me aturar quando estava mal disposto ou até com a cabeça noutro lado, pela companhia, pelo apoio incondicional e por no fim de tudo ainda ter a disponibilidade de me ajudar. Sabes que te amo!

Quero agradecer aos meus pais e aos meus irmãos por sempre me apoiarem independentemente do desafio, dificuldade ou problema. Ainda que não tivesse dado o devido valor, sinto que o apoio incondicional que eles me dão todos os dias foi fundamental para que pudesse chegar onde cheguei.

O meu último agradecimento vai para todos os meus colegas de laboratório que sempre se mostraram disponíveis para me ajudar e para me ouvir, quer numa fase inicial quer na fase final da dissertação, ao Carlos, ao Rapha, ao Monte e ao Filipe o meu obrigado. Um especial obrigado ao tMR. Gomes, pelo companheirismo, pelas piadas, pelas viagens e principalmente pelo desbloqueio de que precisava naquela hora em Zhuhai. Outro agradecimento especial não pode deixar de ir para o Jorge Pereira, sempre disponível para me co-orientar nas alturas que necessitava, obrigado pelo divertimento e amizade que me proporcionaste, nunca o esquecerei.

A todas os meus amigos que mesmo indiretamente me ajudaram nesta dissertação e percurso académico

O meu sincero Obrigado!

### Resumo

O mercado e a própria aplicabilidade de sistemas embebidos têm-se expandido exponencialmente nos últimos anos, levando a uma crescente complexidade e sofisticação dos mesmos. A estes é agora cada vez mais exigido que integrem características próprias de diferentes classes de sistemas operativos — o cariz de tempo-real dos sistemas operativos de Tempo-Real (RTOS) e as interfaces gráficas dos sistemas operativos de Propósito Geral (GPOS). Uma das soluções que permite a coexistência de ambientes heterogéneos numa mesma plataforma de hardware e que garante, ao mesmo tempo, o isolamento dos requisitos de temporeal face às interferências introduzidas pelas características de propósito geral é a utilização da tecnologia de virtualização. Existe um interesse generalizado por parte da indústria e academia em investigar soluções de virtualização assistidas por hardware uma vez que estas apresentam vantagens ao nível de desempenho e esforço de engenharia quando comparadas com as técnicas e soluções tradicionais.

A crescente necessidade de integração de um maior número de funcionalidades e complexidade nos sistemas embebidos atuais tem sido acompanhada por melhorias, na sua quase totalidade correspondentes, de performance por parte das plataformas single-core. No entanto esse crescimento está a tornar-se gradualmente insuficiente, levando em muitos casos a consumos energéticos exagerados por parte destas plataformas devido ao aumento insustentável da performance. A única solução viável para aumentar a performance sem comprometer o consumo é a migração para plataformas multicore.

Neste contexto a presente dissertação propõe a expansão de uma framework de virtualização assistida por hardware numa configuração single-core para uma configuração multicore. A tecnologia ARM TrustZone é explorada e utilizada pela framework já existente como uma extensão de virtualização do próprio processador, garantindo a execução simultânea de um GPOS e de um RTOS. Esta dissertação tem por objetivo implementar uma configuração Asymetric MultiProcessing (AMP) numa abordagem direta: dual guest, dual core. Será também explorada a implementação de um mecanismo de comunicação inter-partição por forma a potencializar as características das partições integrantes na framework.

**Palavras Chave:** Sistemas Embebidos, Virtualização, *Multicore*, Comunicação e ARM TrustZone.

### Abstract

The embedded systems' market and its own applicability has expanded exponentially these last few years, leading to a growth in their complexity and sophistication. They have been increasingly demanded to integrate features of different operating systems classes – the real-time requirements of Real Time Operating Systems (RTOS) and the graphical interfaces of General Purpose Operating Systems (GPOS). One of the solutions which allows the coexistence of heterogenous environments in a same hardware platform and at the same time enforces the isolation of the real-time requirements against the interferences introduced by the general-purpose features is the use of virtualization technology. There is a general interest by both the industry and the scientific community to explore the hardware assisted virtualization solutions, since they present a better performance level and engineering effort when compared with traditional solutions.

The growing need for integration of a multiple number of features as well as complexity levels in embedded systems has been followed by improvements in performance rates, almost correspondently, by single-core platforms. Nevertheless, these improvements are becoming gradually insufficient, leading in many cases to an exaggerated energy consumption by those platforms due to the unsustainable need for performance levels. The only viable solution to the aforementioned problem without compromising the energy consumption is the migration to multicore platforms.

In this context, the present dissertation purposes the expansion of a single-core hardware assisted virtualization framework to a multicore configuration. The existent framework explores the use of the technology ARM TrustZone as virtualization extensions of the processor, thus granting the simultaneous execution of a RTOS and a GPOS. This dissertation has as its main goal the implementation of an Asymmetric MultiProcessing configuration in a straightforward approach: dual guest, dual core. Additionally the implementation of inter-partition communication mechanisms will be explored in order to potentiate the capabilities of the integrating parts of the framework.

**Keywords:** Embedded Systems, Virtualization, Multicore, Communication and ARM TrustZone.

## Índice

| R            | esum   | 10       |                                             | ix   |

|--------------|--------|----------|---------------------------------------------|------|

| $\mathbf{A}$ | bstra  | nct      |                                             | xi   |

| Ín           | dice   |          |                                             | xiii |

| Li           | ista d | le Figu  | iras x                                      | cvii |

| Li           | ista d | le Tab   | elas                                        | xix  |

| Li           | ista d | le Lista | agens                                       | xxi  |

| 1            | Intr   | roduçã   | 0                                           | 1    |

|              | 1.1    | Conte    | xtualização                                 | 1    |

|              | 1.2    | Motiv    | ação e Objetivos                            | 2    |

|              | 1.3    | Organ    | ização da Dissertação                       | 3    |

| 2            | Lite   | eratura  | a e Estado da Arte                          | 5    |

|              | 2.1    | Sistem   | nas Embebidos                               | 5    |

|              | 2.2    | Virtua   | alização                                    | 6    |

|              |        | 2.2.1    | Virtualização Assistida por Software        | 8    |

|              |        | 2.2.2    | Virtualização Assistida por <i>Hardware</i> | 10   |

|              |        |          | 2.2.2.1 Intel Virtualization Technology     | 10   |

|              |        |          | 2.2.2.2 ARM Virtualization Extensions       | 11   |

|              |        |          | 2.2.2.3 ARM TrustZone Security Extensions   | 12   |

|              | 2.3    | Multio   | core                                        | 13   |

|              |        | 2.3.1    | Symetric Multiprocessing                    | 16   |

|              |        | 2.3.2    | Asymetric Multiprocessing                   | 17   |

|              |        |          | 2.3.2.1 AMP Supervisionado                  | 18   |

|              | 2.4    | Comu     | nicação Inter-Partição                      | 20   |

|              |        | 2.4.1    | Xen                                         | 23   |

|              |        | 2.4.2    | OpenAMP e Linux Drivers                     | 24   |

|              |        | 2.4.3    | Mentor Embedded Multicore Framework (MEMF)  | 25   |

| 3 | Esp | ecifica | ção do S    | istema                        | 27        |

|---|-----|---------|-------------|-------------------------------|-----------|

|   | 3.1 | Arquit  | tetura AR   | kM                            | 27        |

|   |     | 3.1.1   | Arquitet    | ura ARM - Conceitos Básicos   | 28        |

|   |     | 3.1.2   | ARM Tr      | $\operatorname{rustZone}$     | 31        |

|   |     |         | 3.1.2.1     | Processador                   | 32        |

|   |     |         | 3.1.2.2     | Memória                       | 33        |

|   | 3.2 | Ambie   | ente de De  | esenvolvimento                | 34        |

|   |     | 3.2.1   | Zynq-70     | 00                            | 35        |

|   |     | 3.2.2   | Xilinx V    | Tivado e XSDK                 | 36        |

|   |     |         | 3.2.2.1     | Xilinx Vivado                 | 36        |

|   |     |         | 3.2.2.2     | Xilinx SDK                    | 37        |

|   |     | 3.2.3   | ARM Fa      | ast Models                    | 37        |

|   | 3.3 | Arquit  | tetura do   | Sistema                       | 38        |

|   |     | 3.3.1   | LTZVisc     | or                            | 38        |

|   |     |         | 3.3.1.1     | Monitor                       | 39        |

|   |     |         | 3.3.1.2     | Mundo Seguro                  | 43        |

|   |     |         | 3.3.1.3     | Mundo Não-Seguro              | 45        |

|   |     | 3.3.2   | Comunic     | cação OpenAMP                 | 46        |

|   |     |         | 3.3.2.1     | Remoteproc                    | 47        |

|   |     |         | 3.3.2.2     | VirtIO                        | 48        |

|   |     |         | 3.3.2.3     | RPMsg                         | 53        |

| 4 | LTZ | ZVisor  |             |                               | <b>59</b> |

|   | 4.1 | LTZV    | isor - Sing | gle-core                      | 59        |

|   |     | 4.1.1   | Análise     | Estrutural                    | 59        |

|   |     | 4.1.2   | Fluxo de    | e Execução                    | 63        |

|   |     | 4.1.3   | Para-Tru    | $\operatorname{ustZone}$      | 65        |

|   |     |         | 4.1.3.1     | Linux 3.3                     | 66        |

|   |     |         | 4.1.3.2     | Linux 4.0                     | 66        |

|   | 4.2 | LTZV    | isor - Mul  | lticore                       | 68        |

|   |     | 4.2.1   | Design .    |                               | 68        |

|   |     | 4.2.2   | Impleme     | entação                       | 70        |

|   |     |         | 4.2.2.1     | Arranque do Núcleo Secundário | 71        |

|   |     |         | 4.2.2.2     | Inicialização da Plataforma   | 72        |

|   |     |         | 4.2.2.3     | Sincronização – Holding Pen   | 73        |

|   |     |         | 4.2.2.4     | Guest do Mundo Seguro         | 74        |

|   | 4.3 | LTZV    | isor - Con  | nunicação Inter-Partição      | 74        |

|   |     | 121     | Dogica      |                               | 75        |

|              |       | 4.3.2                   | LTZVisor                                             |     | 77  |

|--------------|-------|-------------------------|------------------------------------------------------|-----|-----|

|              |       | 4.3.3                   | Implementação                                        |     | 80  |

|              |       |                         | 4.3.3.1 Memória                                      |     | 81  |

|              |       |                         | 4.3.3.2 Remoção Remoteproc                           |     | 82  |

|              |       | 4.3.4                   | RTOS                                                 |     | 83  |

|              |       | 4.3.5                   | GPOS                                                 |     | 84  |

|              |       |                         | 4.3.5.1 Interrupções Inter-Core                      |     | 85  |

|              |       |                         | 4.3.5.2 RPMsgSuper                                   |     | 85  |

|              |       |                         | 4.3.5.3 VirtIO – Slave                               |     | 87  |

|              |       | 4.3.6                   | Escalabilidade                                       |     | 88  |

| 5            | Res   | $\operatorname{ultado}$ | $\mathbf{s}$                                         |     | 91  |

|              | 5.1   | Multi a                 | core                                                 |     | 91  |

|              |       | 5.1.1                   | Footprint de Memória $\dots \dots \dots \dots \dots$ |     | 92  |

|              |       | 5.1.2                   | RTOS                                                 |     | 93  |

|              |       | 5.1.3                   | GPOS                                                 |     | 96  |

|              |       | 5.1.4                   | RTOS em Carga                                        |     | 97  |

|              | 5.2   | Comu                    | nicação                                              | . 1 | 100 |

|              |       | 5.2.1                   | Footprint de Memória $\dots \dots \dots \dots \dots$ | . 1 | 100 |

|              |       | 5.2.2                   | Desempenho do Context-Switch                         | . 1 | 102 |

|              |       | 5.2.3                   | Caracterização da Comunicação                        | . 1 | 103 |

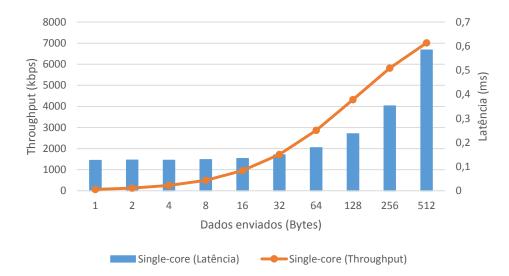

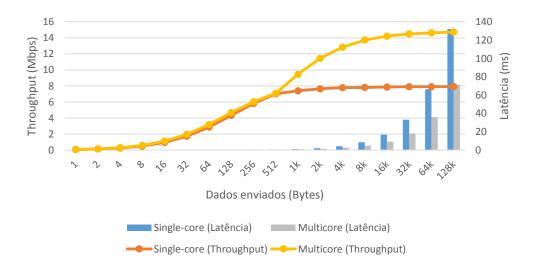

|              |       |                         | 5.2.3.1 Variação de Bytes Enviados numa Mensagem $$  | . 1 | 105 |

|              |       |                         | 5.2.3.2 Variação do Número de Mensagens Enviadas     | . 1 | 108 |

|              |       |                         | 5.2.3.3 Conclusão                                    | . 1 | 110 |

| 6            | Cor   | ıclusõe                 | es                                                   | 1   | 13  |

|              | 6.1   | Discus                  | ssão                                                 | . ] | 113 |

|              | 6.2   | Traba                   | lho Futuro                                           | . 1 | 114 |

| $\mathbf{R}$ | eferê | ncias I                 | Bibliográficas                                       | 1   | 19  |

## Lista de Figuras

| 2.1  | Virtualização multicore de uma plataforma fisíca                                      | 7  |

|------|---------------------------------------------------------------------------------------|----|

| 2.2  | $\operatorname{Modos}$ de privilégio vistos em vários tipos de processadores ARM $$ . | 11 |

| 2.3  | Compromisso entre performance e consumo energético                                    | 14 |

| 2.4  | Symetric multiprocessing (SMP) num processador quadcore                               | 17 |

| 2.5  | Asymetric multiprocessing (AMP) num processador quadcore                              | 18 |

| 2.6  | Configurações de virtualização e técnicas $multicore$ plataformas $single$ -          |    |

|      | core e multicore                                                                      | 19 |

| 2.7  | Exemplo de cooperação entre diferentes partições                                      | 21 |

| 2.8  | Exemplo de comunicação no hypervisor Xen direcionado para a                           |    |

|      | indústria aviónica [1]                                                                | 23 |

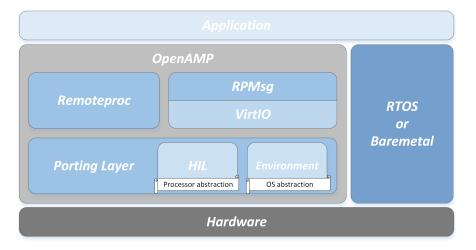

| 2.9  | Arquitetura da Implementação OpenAMP                                                  | 25 |

| 2.10 | Arquitetura do MEMF na plataforma Zynq UltraScale [2]                                 | 25 |

| 3.1  | Divisão entre cores virtuais no mesmo core físico                                     | 32 |

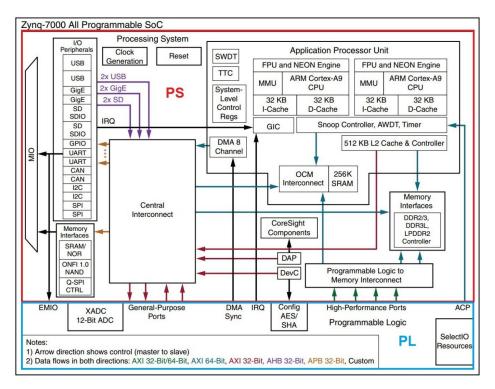

| 3.2  | Arquitetura do Zynq-7000 AP SoC [3]                                                   | 36 |

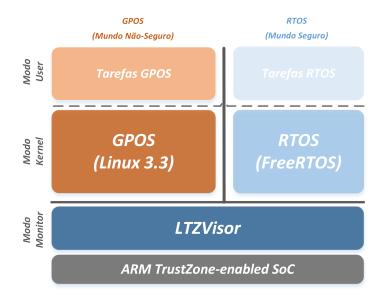

| 3.3  | Arquitetura single-core do LTZVisor                                                   | 39 |

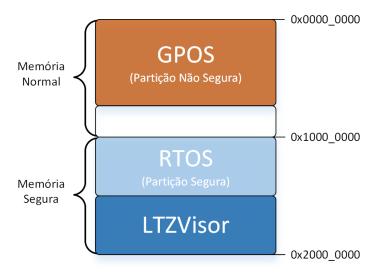

| 3.4  | Divisão da memória em termos de segurança e partições $\ \ \ldots \ \ \ldots$         | 41 |

| 3.5  | Exemplo de acesso a um dispositivo seguro no LTZVisor por parte                       |    |

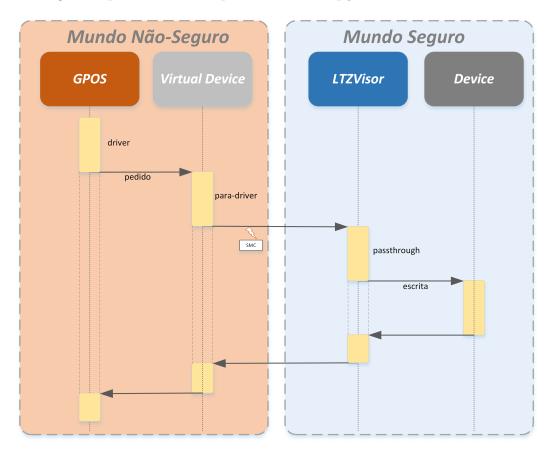

|      | do GPOS utilizando a técnica para-TrustZone                                           | 42 |

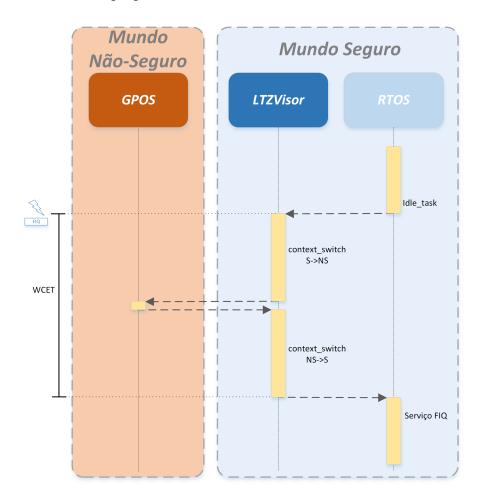

| 3.6  | Worst Case Estimated Time (WCET) da latência de serviço a uma                         |    |

|      | FIQ                                                                                   | 44 |

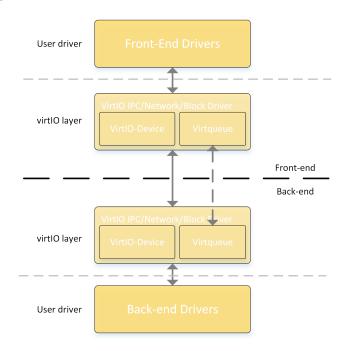

| 3.7  | Hierarquia de drivers de para-virtualização utilizando o Virt<br>IO                   | 49 |

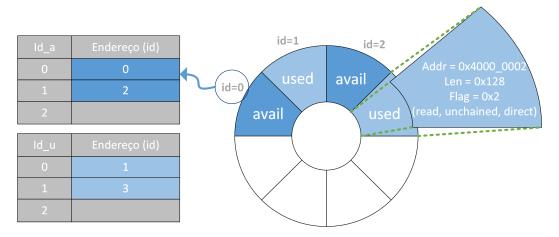

| 3.8  | Arrays circulares da camada de transporte virtqueue do Virt<br>IO $$ .                | 50 |

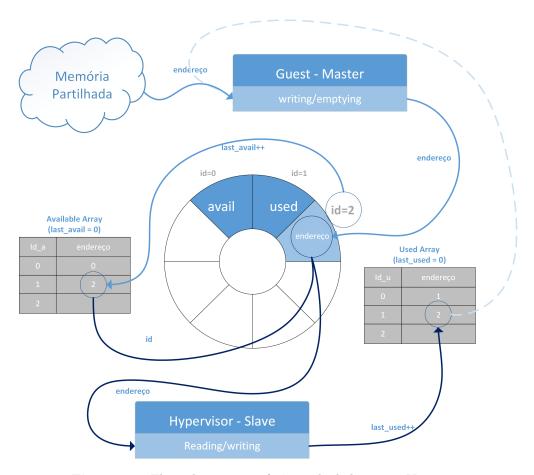

| 3.9  | Fluxo de uma transferência de dados numa Virtqueue                                    | 52 |

| 3.10 | Canal RPMsg e respetivos endpoints                                                    | 53 |

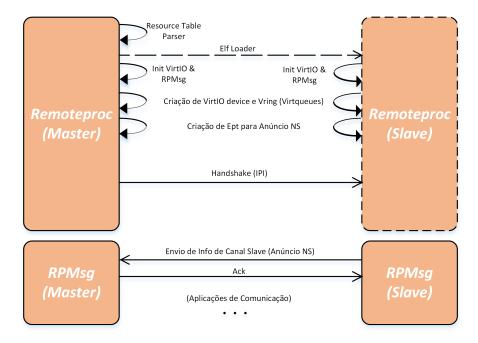

| 3.11 | Handshakenuma comunicação Remote<br>proc/RPMsg                                        | 55 |

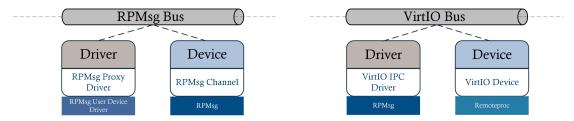

| 3.12 | Relação entre drivers e devices no OpenAMP                                            | 56 |

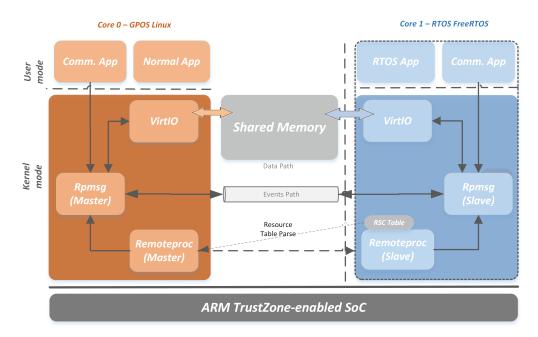

| 3.13 | Arquitetura de dois SOs utilizando Open<br>AMP<br>                                    | 56 |

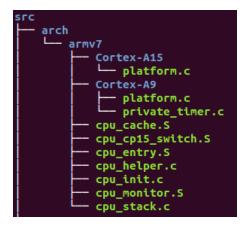

| 4.1  | Árvore da Subpasta Arch                                                               | 60 |

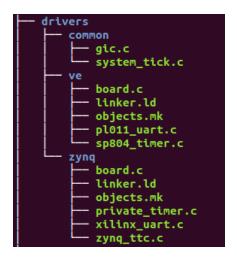

| 4.2  | Árvore da Subpasta <i>Drivers</i>                                                     | 62 |

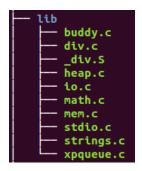

| 4.3  | Árvore da Subpasta $Lib$                                                              | 62 |

| 4.4  | Árvore da subpasta $Secure\_Guest$                                                    | 63 |

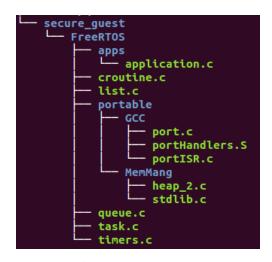

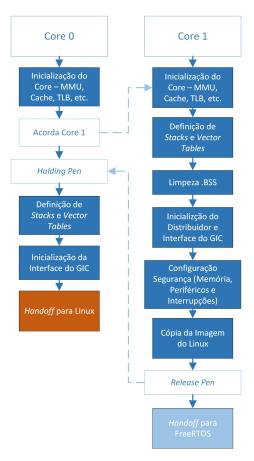

| 15   | Fluvo da Inicialização do Sistema                                                     | 64 |

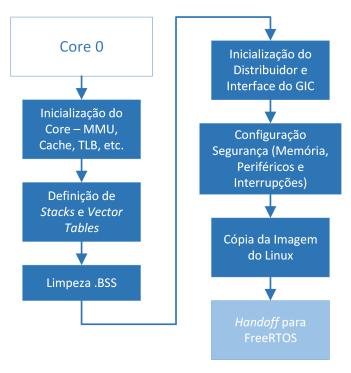

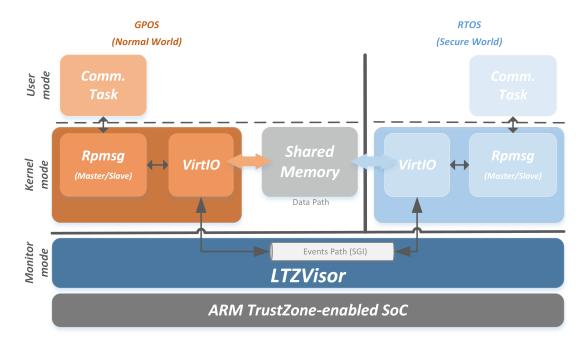

| 4.6  | Arquitetura do LTZVisor em configuração AMP                                          | 69 |

|------|--------------------------------------------------------------------------------------|----|

| 4.7  | Fluxo da inicialização do sistema em configuração AMP                                | 70 |

| 4.8  | Fluxo do Arranque do Core 1                                                          | 71 |

| 4.9  | Arquitetura da comunicação inter-partição                                            | 77 |

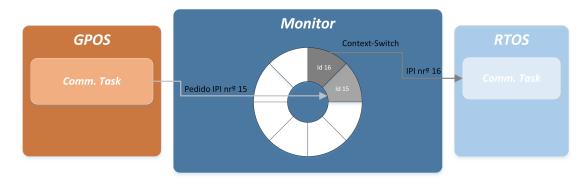

| 4.10 | Pedido e Desencadeamento de IPI através do Monitor                                   | 79 |

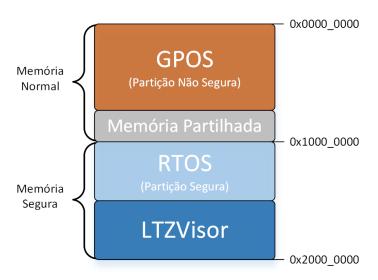

| 4.11 | Layout da memória do LTZV<br>isor com Comunicação                                    | 81 |

| 4.12 | Reformulação do Handshake                                                            | 83 |

| 4.13 | Overview da arquitetura da comunicação no Linux                                      | 87 |

| 4.14 | Buffer Circular de Armazenamento de IPIs numa Arquitetura $\mathit{Mul}$ -           |    |

|      | tiguest                                                                              | 89 |

| 4.15 | Instanciação de dois canais RPMsg num mesmo par de SOs, simu-                        |    |

|      | lando um sistema $multiguest$                                                        | 90 |

| 5.1  | Comparação entre o FreeRTOS Nativo e inserido no LTZVisor $single$                   |    |

|      | core e multicore                                                                     | 95 |

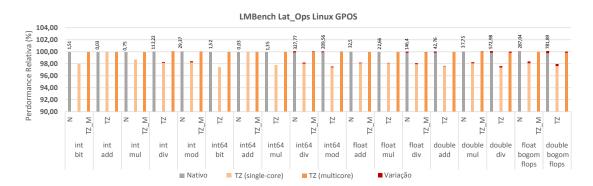

| 5.2  | Resultados do $Lat\_Ops$ para as diferentes configurações do Linux $$ .              | 97 |

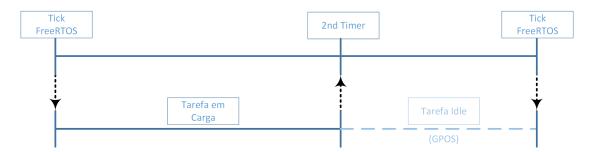

| 5.3  | Nível de Carga do Free<br>RTOS dado por um segundo $timer$                           | 98 |

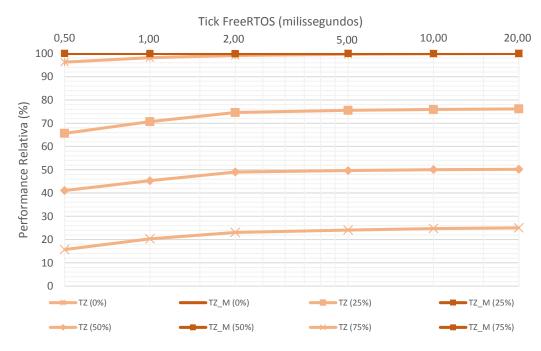

| 5.4  | Resultados do $Lat\_Ops$ para as diferentes configurações do Linux,                  |    |

|      | variando a carga e $tick$ do FreeRTOS                                                | 99 |

| 5.5  | Comunicação Singlecore – Latência de envio de uma mensagem de                        |    |

|      | diferentes tamanhos                                                                  | 06 |

| 5.6  | Comunicação Multicore – Latência de envio de uma mensagem de                         |    |

|      | diferentes tamanhos                                                                  | 06 |

| 5.7  | Comunicação – Latência de envio de uma mensagem de diferentes                        |    |

|      | tamanhos                                                                             | 07 |

| 5.8  | Comunicação Singlecore – Latência de envio de várias mensagens                       |    |

|      | de 512 bytes cada (1 a 256 mensagens – 512 a 128<br>k Bytes) $\ \ldots \ \ldots \ 1$ | 09 |

| 5.9  | Comunicação Multicore – Latência de envio de várias mensagens de                     |    |

|      | 512 bytes cada (1 a 256 mensagens – 512 a 128k Bytes)                                | 09 |

| 5.10 | Comunicação – Latência de envio de mensagens entre 1 Byte até                        |    |

|      | 128 kBytes                                                                           | 11 |

## Lista de Tabelas

| 2.1 | Modos de processamento e respetivo privilégio em processadores                                 |

|-----|------------------------------------------------------------------------------------------------|

|     | ARM                                                                                            |

| 3.1 | Diferentes processadores dentro da arquitetura ARMv7 28                                        |

| 3.2 | Modos de execução de um processador ARM e respetivos níveis de                                 |

|     | privilégio                                                                                     |

| 3.3 | Mapa de registos do processador Cortex-A9                                                      |

| 5.1 | $Footprint \ {\rm de \ Mem\'oria \ do \ Sistema \ LTZVisor + FreeRTOS - } \ multicore \ \ 92$  |

| 5.2 | Footprint de Memória do Sistema LTZVisor + FreeRTOS – comu-                                    |

|     | nicação                                                                                        |

| 5.3 | $Footprint \ de \ Mem\'{o}ria \ do \ Linux-comunicação \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ |

| 5.4 | Valores de ciclos de relógio para comutação de mundos em diferentes                            |

|     | cenários                                                                                       |

| 5.5 | Diferença entre taxa de transferência da comunicação single-core e                             |

|     | <i>multicore</i>                                                                               |

| 5.6 | Taxa de Transferência para diferentes métodos aplicados na comu-                               |

|     | nicação multicore comparativamente com comunicação single-core . 110                           |

## Lista de Listagens

| 3.1  | Estrutura resource_table                                      |

|------|---------------------------------------------------------------|

| 3.2  | Estrutura do $header$ de uma mensagem RPMsg                   |

| 4.1  | Inicialização do GIC                                          |

| 4.2  | Configurações de segurança iniciais                           |

| 4.3  | Seleção de Plataforma no Makefile                             |

| 4.4  | Algoritmo de verificação de core                              |

| 4.5  | Instanciação das vector table no CP15                         |

| 4.6  | Mudança de estado de segurança do Global Timer 67             |

| 4.7  | Acordar do core secundário                                    |

| 4.8  | Mecanismo de sincronismo Holding Pen                          |

| 4.9  | Exemplo de utilização de identificação do núcleo              |

| 4.10 | Requisito de IPI ao monitor - mundo seguro                    |

| 4.11 | Envio de IPI em altura de <i>context-switch</i>               |

| 4.12 | Estrutura de gestão de IPI presente nas VMCB 79               |

| 4.13 | Requisito de IPI ao monitor - mundo não-seguro                |

| 4.14 | Exemplo de configuração do RPMsgSuper na DTS 86               |

| 4.15 | Utilização do $guest\_id$ reservada para futura utilização 89 |

| 5 1  | Compilação dependente da variável MP AMP 93                   |

## Introdução

#### 1.1 Contextualização

Os sistemas embebidos têm vindo a tornar-se parte integrante do quotidiano das sociedades modernas, tendo agora uma maior abrangência em termos de mercado do que há uns anos atrás, nomeadamente mercados como sistemas de transporte, área medicinal e até mesmo dispositivos eletrónicos de consumo. Este aumento da área de aplicabilidade de sistemas embebidos levou consequentemente a um aumento de desafios criados pelas exigências por parte do mercado, havendo uma necessidade de integração de diferentes funcionalidades num mesmo sistema de recursos limitados concluindo num aumento de complexidade dos mesmos.

De uma forma geral, todos os sistemas embebidos apresentam as seguintes métricas: performance, tamanho e peso, time-to-market, consumo energético e lista de materiais (BOM – bills of materials). Além destas métricas, que eventualmente se transformarão em requisitos, existem também certas restrições das quais se destacam o cariz de tempo-real, a fiabilidade e/ou a segurança em relação à resistência a ataques externos, que necessitam de ser considerados pelos projetistas dos sistemas embebidos.

Existe um amplo número de soluções capazes de mitigar os problemas acima referidos e até mesmo de auxiliar o cumprimento dos requisitos impostos. Soluções como a utilização de FPGAs, utilização de tecnologia *multicore* e técnicas de virtualização estão entre as tecnologias *state-of-the-art* atualmente utilizadas na área de sistemas embebidos.

De entre as soluções supracitadas a utilização de técnicas de virtualização está entre as soluções que mais se tem destacado ultimamente. Apesar de já ser utilizada recorrentemente em sistemas de propósito geral, esta solução apenas mais recentemente tem sido utilizada em sistemas embebidos [4]. Recorrer a técnicas de virtualização assistidas por software, ou em alguns casos assistidas por hardware, tem sido uma constante para implementação de múltiplas classes de sistemas operativos num mesmo dispositivo hardware, permitindo assim otimizar o BOM, sendo que muitas vezes pode afetar métricas como a performance e time-to-market, especialmente quando implementada em software.

2 INTRODUÇÃO

Recorrendo ao suporte oferecido por extensões em hardware do próprio processador, estas soluções de virtualização conseguem mitigar as limitações de quebra de performance e time-to-marker acima referidas. Comparativamente às suas vantagens inerentes este género de solução tem tido uma aderência relativamente escassa. Esta escassez de soluções de virtualização assistidas por hardware justificase pelo preço, sendo que os processadores nas quais se encontram este tipo de extensões de hardware são tipicamente processadores de gama alta e até de cariz não determinístico e por vezes pouco apreciados.

É nesta conjuntura, de processadores de gama média-baixa para os quais existe uma necessidade de técnicas de virtualização e onde não existe um suporte próprio em hardware para a sua implementação, que surge a tecnologia ARM® TrustZone®. Desenvolvida em 2003 pela ARM, este conjunto de extensões de segurança em hardware tem o propósito de isolar partes críticas do sistema de possíveis fontes de vulnerabilidade nos sistemas operativos. Apesar desta conceção original, a tecnologia tem sido explorada para a implementação de soluções de virtualização assistidas por hardware, aparecendo diversos projetos como [5, 6, 7, 8, 9, 10, 11, 12, 13].

Dos projetos supracitados destaca-se a framework desenvolvida in-house pelo ESRG [5]. A framework explora as extensões de segurança em hardware ARM TrustZone para implementar um hypervisor assistido por hardware. A framework apresenta uma arquitetura de virtualização que possibilita a integração de um RTOS (Real Time Operating System) e de um GPOS (General Purpose Operating System) numa mesma plataforma.

### 1.2 Motivação e Objetivos

As tradicionais técnicas de virtualização, isto é, as técnicas de virtualização assistidas exclusivamente por software, apesar do seu recente ímpeto e crescente popularidade em sistemas embebidos [4], representam sempre um trade-off entre a flexibilidade e a performance. A virtualização por emulação tem um custo no desempenho do sistema, enquanto que a para-virtualização representa um grande esforço de engenharia. Neste contexto, várias entidades introduziram no hardware dos seus SoCs extensões de virtualização.

A tecnologia ARM TrustZone tem ganho particular importância pela sua predominância em processadores do domínio embebido quando comparada com as extensões de virtualização, sendo inclusivamente vistas como a única solução para processadores ARM privados das ARM Virtualization Extension (VE). Apesar de

INTRODUÇÃO 3

se tratarem de extensões de hardware direcionadas para segurança, as mesmas têm sido exploradas para a implementação de hypervisores dual-OS assistidos por hardware, como é exemplo a framework em expansão [5].

Contudo, a solução [5], por prioritizar as características de tempo-real do sistema, apresenta uma limitação, destacada por Ngabonziza *et al.* em [14]. Quando o RTOS tem um fator de carga demasiado elevado, pode, como consequência, nunca ceder o controlo do processador. Nesse caso o GPOS incorre no fenómeno de *starvation*, não tendo tempo de execução no processador.

A migração da framework para uma configuração multicore é vista como a solução para o fenómeno supracitado. A paralelização do processamento da framework permitiria solucionar a influência temporal do RTOS sobre o GPOS, eliminando por completo a sua limitação conhecida.

Neste sentido surge a presente dissertação que tem como objetivo expandir a framework para uma configuração multicore. Adicionalmente, esta dissertação pretende munir a framework de mecanismos de comunicação, tornando-a no geral, numa solução robusta e flexível, obtendo assim a versatilidade para ser utilizada numa ampla gama de problemas existentes no domínio embebido.

Abaixo estão sumarizados os objetivos individuais que esta dissertação pretende cumprir:

- Expansão da *framework* para uma configuração *multicore* AMP, dual-core, dual-OS;

- Implementação de um mecanismo de comunicação versátil e escalável, suportado em ambas as configurações single-core e multicore;

- Avaliação da configuração multicore implementada comparativamente com a framework original. Avaliação realizada em termos de footprint de memória, métricas real-time e desempenho global dos quests inclusos;

- Caracterização do mecanismo de comunicação implementado. Este deverá ser avaliado em termos de latência, throughput e impacto geral no sistema para ambas as configurações.

### 1.3 Organização da Dissertação

A presente dissertação está dividida em 6 capítulos diferentes. No presente capítulo pretendeu-se contextualizar o problema abordado assim como revelar as

INTRODUÇÃO

4

motivações para a implementação do mesmo, tendo sido posteriormente revelados os objetivos propostos na realização da dissertação.

No capítulo 2 serão abordadas as tecnologias utilizadas no decorrer da realização da dissertação, com destaque para as tecnologias de virtualização, multicore e OpenAMP. Estas são reveladas como a solução para as tendências e desafios dos sistemas embebidos. Será feita uma análise comparativa entre as tecnologias supramencionadas e as demais analisadas como solução dos diferentes problemas com que se deparam os sistemas embebidos.

O capítulo 3 é responsável por descrever detalhadamente a arquitetura ARM, com um foco na arquitetura do processador presente na plataforma utilizada no desenvolvimento da dissertação, o processador Cortex-A9. Será abordada em detalhe a tecnologia ARM TrustZone e como a mesma se correlaciona com a framework de virtualização. Posteriormente serão referenciadas as ferramentas utilizadas no desenvolvimento da dissertação. Por último é descrita a arquitetura inicial da framework de desenvolvimento, bem como a arquitetura especificada pelo OpenAMP.

O capítulo 4 foca-se nos detalhes de implementação da expansão da framework para uma configuração multicore e ainda no suporte integrado para mecanismos de comunicação inter-partição. Inicialmente será feita uma análise meticulosa estrutural da configuração inicial da framework para que seja mais fácil para o leitor entender as alterações realizadas e respetivos impactos na mesma.

Os resultados obtidos da avaliação global das soluções propostas são apresentados no capítulo 5. Os resultados debruçar-se-ão sobre o impacto das diferentes configurações do LTZVisor nos sistemas operativos *guests* e nas suas principais características comparativamente com as suas versões nativas. Será ainda realizada uma caracterização da solução de comunicação implementada.

Finalmente, o capítulo 6 apresentará as conclusões retiradas do trabalho exposto, as melhorias e limitações introduzidas na *framework*. Serão feitas recomendações de possíveis melhorias ou adições de funcionalidades ao sistema como trabalho futuro a esta dissertação.

### Literatura e Estado da Arte

#### 2.1 Sistemas Embebidos

Os sistemas embebidos estão omnipresentes, estando neste momento altamente disseminados pela sociedade moderna. Os domínios dos sistemas embebidos são realmente extensos: desde sistemas de entretenimento nos quais é exigido cada vez mais uma melhor performance, como nos dispositivos eletrónicos de consumo (e.g. telemóveis, televisões, etc.), a sistemas de suporte vital nos quais é exigida a máxima fiabilidade, sendo estes bastante comuns em sistemas de transporte (e.g., aviação, automóvel, espaço, etc.) ou na área da saúde.

A sua evolução tecnológica e consequentemente a constante mudança de funcionalidades e de hardware incluso, assim como a mudança das características requeridas nos mesmos, tornam difícil encontrar uma definição que reúna consenso. No entanto, apesar desta mudança de paradigma constante, existe algo comum a todas as gerações de sistemas embebidos. A sua especificidade e respetiva utilização. Estes são sistemas de propósito específico incorporados num sistema maior (geralmente incluindo hardware adicional e/ou partes mecânicas) com a finalidade de o controlar, monitorar ou acrescentar-lhe funcionalidades [15].

Os sistemas embebidos possuem geralmente limitações ao nível de recursos presentes no seu hardware, realçando-se a escassez de memória e a performance. Aliado a estas limitações ou mesmo pela própria aplicabilidade/finalidade dos sistemas, existem determinados requisitos que têm ditado a tendência na sua conceção e no seu aprimoramento: a) melhor performance, b) baixo consumo energético, c) tamanho e peso reduzido, d) rápido time-to-market e e) baixo bills of materials (BOM). Simultaneamente existem outros requisitos próprios de sistemas embebidos de tempo-real ou de finalidades específicas dos próprios sistemas que necessitam também de ser levados em consideração pelos projetistas de sistemas embebidos. Entre eles destacam-se as características de tempo-real, a fiabilidade e a segurança. Estes requisitos têm ganho particular importância devido ao advento da interconectividade em sistemas embebidos, proporcionada pela era da Internet of Things, bem como a junção de diferentes classes de sistemas operativos numa mesma plataforma.

Para combater este conjunto de desafios ambas a comunidade científica e indústria têm-se virado para soluções baseadas em tecnologias state-of-the-art: Multicore, FPGA e técnicas de virtualização. Vanderleest et al. em [16], refere estas soluções como a base para o futuro da tecnologia aviônica onde a maioria dos requisitos supramencionados se aplicam. A presente dissertação invoca o uso da tecnologia Multicore e extensões de hardware para utilização de técnicas de virtualização de forma a expandir a framework [5] no sentido de combater os requisitos impostos frequentemente a designers de sistemas embebidos.

### 2.2 Virtualização

A definição de virtualização em termos computacionais é a criação de uma abstração integral ou parcial em software do sistema computacional hardware. A forma mais comum de virtualização é a de criação de uma abstração do processador inteiro, criando assim um número variável de processadores virtuais (VCPU). O principal objetivo desta abstração é a possibilidade de alojar simultaneamente num mesmo processador físico (de forma time-sliced) mais do que um sistema operativo (SO), isto é, permitindo que múltiplos sistemas operativos isolados espacial e temporalmente co-habitem a mesma plataforma.

A camada de software que possibilita a abstração dos recursos do hardware e que é responsável pelo cumprimento do isolamento temporal e espacial é normalmente denominada de hypervisor ou Virtual Machine Monitor (VMM). Para que o isolamento seja garantido, esta camada deverá ser executada num modo com um nível de privilégio acima dos sistemas operativos virtualizados, também denominados de Virtual Machines (VM) [12]. Usualmente ao modo de privilégio superior do sistema está associado o controlo exclusivo de certos periféricos que são utilizados para a aplicação do isolamento temporal e espacial, como temporizadores e controladores de memória (e.g. MMU, MPU, entre outros). A atribuição exclusiva do modo superior de privilégio ao hypervisor é considerado um dos maiores desafios na implementação de técnicas de virtualização em sistemas embebidos, nos quais os processadores possuem tipicamente apenas dois modos de privilégio.

O hypervisor deverá ser responsável na maioria dos casos, à semelhança de um sistema operativo, por realizar o escalonamento dos sistemas operativos. Assim como um sistema operativo deverá também realizar o context switch e alterações necessárias, se o sistema em que o hypervisor está inserido assim o exigir, como mudanças de estados em recursos partilhados. O hypervisor deverá ainda fortalecer e aplicar o isolamento espacial e temporal entre as diferentes partições. Os

hypervisores podem ser divididos em dois tipos, de acordo com a metodologia de como são implementados:

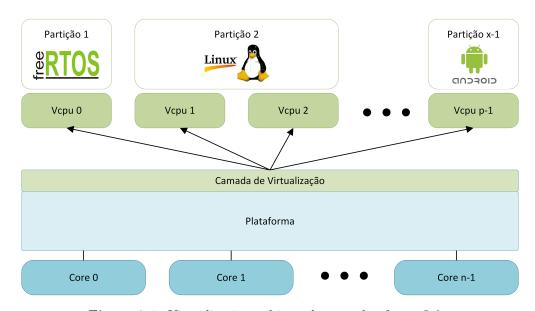

- **Tipo 1:** O hypervisor, como observado na Figura 2.1 (denominado de *Camada de Virtualização*), é executado de forma nativa/baremetal, isto é, diretamente no hardware. Este tipo de hypervisor é o mais comum na área de sistemas embebidos;

- **Tipo 2:** O hypervisor executa dentro do contexto de um sistema operativo, sendo tratado pelo SO *host* como um processo normal. Estes hypervisores são frequentemente denominados de *hosted hypervisors*. Dentro deste tipo de hypervisores destacam-se as distribuições comerciais Virtualbox e VMWare.

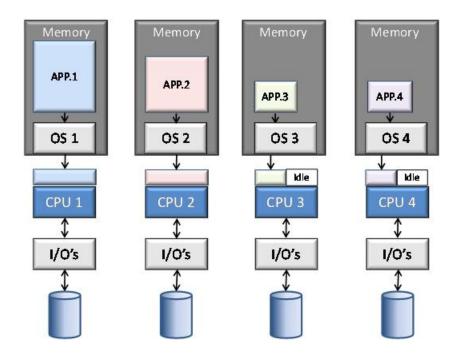

Figura 2.1: Virtualização multicore de uma plataforma fisíca

A Figura 2.1 retrata uma solução de virtualização bastante usual em sistemas embebidos onde é utilizado um hypervisor de tipo 1, uma solução existente em frameworks como a presente no projecto MultiPARTES [17] ou Xen [18]. A Figura 2.1 representa uma técnica de virtualização aplicável a uma plataforma física com número variável de cores. A virtualização neste caso cria um número variável de VCPUs, uma representação virtual de um core do processador. A cada core pode estar associado vários VCPUs, sendo nesse caso cada VCPU uma representação virtual de um time-slice desse mesmo core. Na figura pode-se ver representado várias partições, podendo cada uma delas conter um ou mais VCPUs e estar associada um guest/SO. Esses VCPUs podem pertencer a cores diferentes e correr em simultâneo observando-se uma partição multicore, como podem ser representações de um mesmo core e correr em alternância originando uma partição

single-core com uma frequência de execução mais elevada no core representado pelos VCPUs pertencentes.

Existem várias soluções de virtualização normalmente divididas em dois tipos de acordo com o suporte usado para a sua implementação: as soluções assistidas unicamente por software e as soluções que utilizam suporte em hardware. Neste subcapítulo serão expostas algumas das vantagens e desvantagens dos dois tipos de soluções sendo feita uma comparação entre ambas.

#### 2.2.1 Virtualização Assistida por Software

A virtualização assistida por software apresenta inúmeros desafios bem conhecidos, cujas soluções apresentam sempre vantagens e desvantagens obrigando sempre a um trade-off das características inerentes aos sistemas embebidos.

O principal desafio consiste no isolamento espacial e temporal das VMs participantes na virtualização. A chave para a resolução deste problema é, como supramencionado, a de executar o VMM de forma exclusiva nos modos de execução do processador de maior nível de privilégio, tendo assim acesso exclusivo aos componentes que aplicam o isolamento, levando a que qualquer possível quebra ou ataque ao isolamento por parte das VMs seja filtrada obrigatoriamente pelo hypervisor. Não obstante, esta solução apresenta uma óbvia desvantagem: as partições perdem um ou mais modos de execução (os que sejam definidos como de maior privilégio) para o hypervisor, acrescentando por si só um novo desafio.

**Tabela 2.1:** Modos de processamento e respetivo privilégio em processadores ARM

| Modo de Execução    | Privilégio |        |  |

|---------------------|------------|--------|--|

| Modo de Execução    | User       | Kernel |  |

| User                | X          |        |  |

| System              |            | X      |  |

| Abort Exception     |            | X      |  |

| Undefined Exception |            | X      |  |

| IRQ                 |            | X      |  |

| FIQ                 |            | X      |  |

| Supervisor          |            | X      |  |

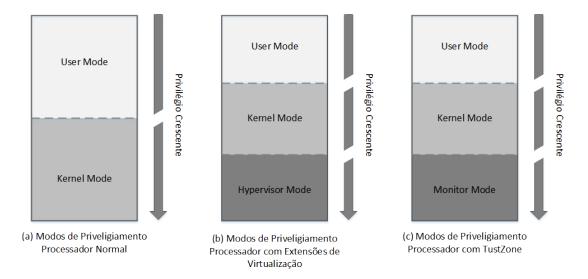

Tipicamente um processador opera em vários modos (e.g.irq, user, supervisor, system, entre outros), no entanto estes podem ser divididos em dois níveis de privilégio como observado na Tabela 2.1: user e kernel, também denominados de modo user e modo kernel. O modo user é caracterizado por conter as aplicações de utilizador, apresentando bastantes restrições de maneira a que uma falha de

uma destas aplicações não comprometa o sistema inteiro. Por outro lado, o modo kernel, que como indica o nome, é onde é executado o kernel do sistema operativo, usualmente garante ao código nele executado um nível de privilégio superior sem restrições, no qual é possível realizar as tarefas de maior importância e de maior impacto no sistema.

Concluindo, a impossibilidade de execução do sistema operativo guest no modo de execução de maior nível de privilégio do processador resume-se num desafio para o funcionamento correto do mesmo, que assim fica impedido de executar instruções exclusivas ao modo kernel. Das soluções encontradas para este desafio destacam-se a para-virtualização e a virtualização completa (full-virtualization):

- (i) Full Virtualization. Neste tipo de virtualização os sistemas operativos guests são integrados sem qualquer tipo de alteração, consequentemente traduzindo-se num rápido time-to-market. O facto de o guest não necessitar de qualquer alteração deve-se a uma tarefa executada pelo hypervisor denominada de trap and emulate. Esta tarefa tem como objetivo capturar qualquer instrução exclusiva ao modo privilégio no qual o hypervisor se encontra e posteriormente emula-la, pois ao guest não lhe é permitido executar nesses mesmos modos. Todavia, apesar de apresentar vantagens ao nível do time-to-market esta solução tem uma desvantagem muitas vezes indesejada ou até insustentável: uma degradação da performance devido ao overhead introduzido no sistema [12] levando muitas vezes a ter de se recorrer a um tipo diferente de virtualização.

- (ii) Paravirtualização. Para além da full-virtualization outro género de virtualização comum assistida por software é a paravirtualização, também denominada de "paravirtualization". Neste tipo de virtualização, contrariamente à full-virtualization, os sistemas operativos guests são modificados de maneira a suportarem hypercalls de maneira semelhante a uma system call, isto é, o guest faz um pedido explícito ao hypervisor para que este execute a instrução exclusiva ao modo de privilégio no qual o próprio hypervisor se encontra. Estas alterações eliminam o overhead introduzido pela full-virtualization na captura deste género de instruções. No entanto, o esforço de engenharia e mesmo de manutenção relacionado com estas alterações aos sistemas operativos guests levam a um aumento do custo de engenharia do produto e a atrasos consideráveis no time-to-market. Estas desvantagens tornam a solução de virtualização pouco atrativa para projetos que requeiram um rápido time-to-market e uma solução ready to use.

Uma outra desvantagem comum à virtualização em software é a de tipicamente existirem periféricos que possuem a capacidade de ultrapassar o isolamento garantido pelo hypervisor, tais como o DMA (direct memory access) ou o GPU (graphical processing unit) [19]. Daí que seja necessário que estes periféricos sejam controlados pelo hypervisor. Essa necessidade traduz-se, para além de um esforço extra de engenharia, numa degradação da performance.

#### 2.2.2 Virtualização Assistida por *Hardware*

Face ao gradual crescimento da sua popularidade mesmo com as conhecidas desvantagens adjacentes às soluções de virtualização assistidas por software, o desenvolvimento e utilização de técnicas de virtualização assistida por hardware ganhou um novo foco. Estas técnicas fazem uso de extensões em hardware integradas na própria arquitetura do processador para implementar soluções de virtualização sem a totalidade ou parte das desvantagens supracitadas.

As extensões caracterizam-se usualmente por adicionarem ao processador um novo nível de privilégio, superior aos existentes e conhecidos modo *user* e modo *kernel*, no qual será executado o hypervisor. Ao novo nível de privilégio adicionam-se outras primitivas em hardware capazes de mitigar um dos maiores desafios da virtualização: o isolamento espacial e temporal. Dependendo da própria extensão, estas primitivas podem incluir adições ou alterações aos componentes do próprio processador de maneira a produzir autênticos CPUs virtuais em hardware. Entre eles destacam-se os periféricos da plataforma, registos de propósito geral ou de coprocessadores, MMU, caches e a própria memória ou controlador de memória.

Dentro das extensões de hardware para a utilização de virtualização no domínio de sistemas embebidos destacam-se as ARM Virtualization Extensions (ARM VE) e as Intel Virtualization Technology (Intel VT).

#### 2.2.2.1 Intel Virtualization Technology

Criada em 2005, a Intel Virtualization Technology (Intel VT) também denominada de Vanderpool numa fase inicial do seu desenvolvimento, é uma extensão de virtualização em hardware presente numa vasta gama de processadores da Intel. A tecnologia VT introduz nos processadores da Intel um novo modo de privilégio denominado "root mode" (mesma propóstio do modo "hypervisor mode" da figura Figura 2.2.b)), possibilitando assim que a virtualização seja implementada sem perdas significativas de performance ou sem que existam alterações obrigatórias aos sistemas operativos quests.

**Figura 2.2:** Modos de privilégio vistos em vários tipos de processadores ARM

Em relação a versões anteriores da mesma tecnologia, a versão x (VT-x) permite, para além de uma migração fácil de ambientes não virtualizados e até de gerações da mesma tecnologia anterior, a virtualização da *page table* em hardware (e respetivo context switch) assim como atribuições de periféricos específicos a um determinado sistema operativo guest.<sup>1</sup>

#### 2.2.2.2 ARM Virtualization Extensions

Criadas em 2010 pela ARM, as extensões de virtualização ARM VE tiveram como objetivo adicionar o suporte para a implementação de técnicas de virtualização nas arquiteturas mais avançadas dos processadores ARM, uma vez que estas, devido a limitações do próprio design, apresentavam falhas que dificultavam a implementação de soluções de virtualização assitida por software.<sup>2</sup>

Estas extensões surgem depois da criação das extensões de segurança ARM TrustZone, estando por isso intrinsecamente ligadas às mesmas. A tecnologia ARM VE adiciona um modo de privilégio superior ao hypervisor denominado de hypervisor mode. De maneira idêntica à Intel VT-x a tecnologia ARM VE permite também a virtualização de periféricos em hardware assim como mecanismos para a virtualização da memória.

$<sup>^{1}</sup> https://www-ssl.intel.com/content/www/us/en/virtualization/virtualization-technology/intel-virtualization-technology.html$

<sup>&</sup>lt;sup>2</sup>https://genode.org/documentation/articles/arm virtualization

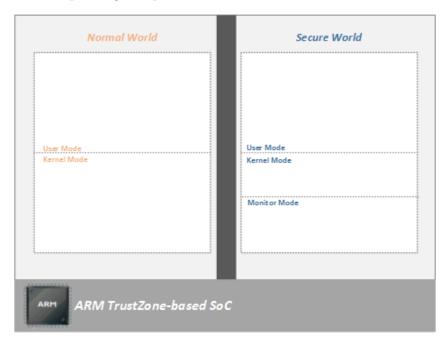

#### 2.2.2.3 ARM TrustZone Security Extensions

A tecnologia ARM TrustZone foi desenvolvida com o propósito de acrescentar características de segurança ao processador adicionando-lhe hardware adicional. Com esse objetivo o hardware adicionado divide o processador e alguns dos seus recursos em dois mundos virtuais conceptualmente chamados de mundo seguro e mundo não-seguro. O objetivo principal é o de criar um ambiente de execução seguro para o mundo virtual seguro, tendo por isso o primeiro mundo níveis de privilégio e acessos superiores ou únicos em relação ao outro mundo. A tecnologia TrustZone adiciona também ao processador um modo de execução de privilégio superior aos modos de privilégio kernel. Neste modo o processador consegue realizar exclusivamente a comutação de mundos virtuais em execução. Este modo possui a característica única de poder controlar os periféricos privilegiados e primitivas adicionadas pela tecnologia TrustZone independentemente do mundo em que se encontra, não necessitando de executar no mundo seguro para controlar e aplicar o isolamento entre os dois mundos virtuais.

Estas características adicionadas pelas extensões de segurança ARM TrustZone são bastante semelhantes a extensões de virtualização em certos aspetos, podendo por isso mesmo ser utilizada para esse efeito com um esforço minimizado quando comparado a soluções de virtualização assistidas por software. A utilização do modo monitor incluído pelas extensões para a implementação do hypervisor permite que os sistemas operativos guests possam executar no modo de privilégio "kernel mode". Os guests podem assim usufruir das instruções exclusivas ao modo kernel sem que o isolamento seja comprometido (por parte do mundo não-seguro) e sem que sejam necessárias alterações aos mesmos (excetuando o caso de acessos a periféricos partilhados). Desta forma retira-se um dos maiores problemas intrinsecamente ligados à implementação de virtualização assistida por software, que seria a eliminação do modo kernel do ponto de vista dos guests.

Para além da vantagem supramencionada, a divisão do processador em dois mundos virtuais, torna propícia a implementação de uma configuração de virtualização denominada de Dual-OS. Nesta configuração, a cada mundo virtual estará associado um sistema operativo guest, estando o isolamento espacial e temporal garantido pelo hardware incluso pela tecnologia TrustZone e pelo próprio hypervisor. No entanto, para que esta premissa seja válida, o guest incluído no mundo virtual seguro terá de fazer parte da Trusted Computing Base (TCB), isto é, deverá ser considerado seguro e capaz de não interferir com os recursos do mundo não-seguro, uma vez que este é capaz de ultrapassar facilmente o isolamento imposto pelo hardware [12].

Assim como em extensões em hardware próprias para a implementação de virtualização, a divisão do processador criada pela tecnologia TrustZone insere também o banqueamento de grande parte dos registos do coprocessador 15 – esses registos não necessitam de ser salvaguardados – e permite também ainda a coexistência de dados separadamente de ambos os mundos/guests na cache – deixa de ser necessária a limpeza ou invalidação da mesma – possibilitando assim um context switch entre guests batante mais rápido do que o realizado numa arquitetura de virtualização assistida por software [19, 12, 9].

As extensões TrustZone permitem ainda o encaminhamento das diversas exceções (abort exception, IRQ, FIQ) para o modo monitor, podendo assim ser tratadas pelo hypervisor. Uma das vantagens associadas a esta característica da tecnologia é a possibilidade de garantir as características de tempo-real de um dos sistemas operativos guests fazendo o encaminhamento das interrupções FIQ diretamente para o mundo onde o mesmo se encontra [5].

Face aos avanços das extensões de virtualização, as soluções de virtualização sofreram enormes progressos, porém a sua empregabilidade ainda é escassa devido ao limitado número de processadores capazes de suportar estas extensões, quer pelo custo adicional, quer pela forma como foram originalmente desenhados ou até mesmo pelas suas características de recursos escassos. No entanto com o anúncio da ARM de estender a tecnologia ARM TrustZone a todos processadores da série Cortex-A e com planos para expandir o seu uso aos processadores da gama Cortex-M³, a exploração desta tecnologia como extensão de virtualização ganhou destaque, tendo surgido projetos como o SafeG criado pela TOPPERS [13], o ViMoExpress [9], o SierraTEE criado pela Sierraware⁴, o projeto SASP [20], assim como própria framework em expansão nesta dissertação [5] ou até projetos como [12, 11].

#### 2.3 Multicore

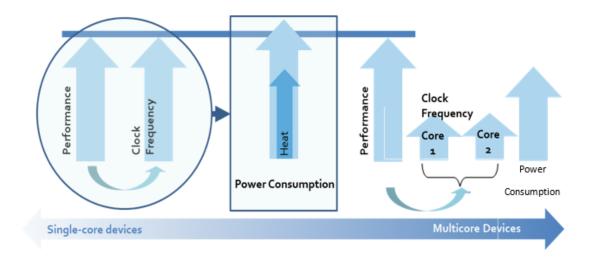

A crescente necessidade de integração de um maior número de funcionalidades e complexidade nos sistemas embebidos atuais tem sido acompanhada por melhorias, na sua quase totalidade correspondentes, de performance por parte das plataformas *single-core*. No entanto esse crescimento está a tornar-se gradualmente insuficiente ou até incomportável, levando em muitos casos a consumos

<sup>&</sup>lt;sup>3</sup>https://www.arm.com/products/security-on-arm/trustzone

<sup>&</sup>lt;sup>4</sup>http://www.sierraware.com

energéticos exagerados por parte destas plataformas devido ao aumento insustentável da performance. A única solução viável para aumentar a performance sem comprometer o consumo de energia é a migração para plataformas *multicore*.

Figura 2.3: Compromisso entre performance e consumo energético

Através da Figura 2.3 é possível observar uma ilustração do compromisso entre performance e consumo energético. Tipicamente, num sistema single-core a forma de obter uma performance superior é através de um aumento da frequência de relógio do processador, o qual se traduzirá num aumento de consumo de energia e de potência dissipada pelo processador. Esse aumento de energia consumida e potência dissipada pode muitas vezes ser insustentável ou até mesmo prejudicial no mundo de sistemas embebidos. Por essa razão, recorre-se à migração para um sistema multicore, no qual o aumento de performance é realizado recorrendo ao processamento paralelizado através da utilização de mais de um core. Existindo um aumento da frequência de relógio dos processadores pertencentes ao sistema, este será repartido pelos CPUs existentes evitando assim os problemas supramencionados. A migração para sistemas multicore é vista na área de sistemas embebidos como inevitável.

Para além do problema do consumo energético associado ao aumento da frequência do processador surge ainda o problema da própria frequência de relógio do processador que pode muitas vezes ser prejudicial no sistema embebidos em que se insere. Um exemplo concreto desta situação será no domínio espacial onde a frequência do processador é limitada devido à presença de radiação, levando por isso a que exista uma maior necessidade de migração para plataformas multicore [17].

Esta tecnologia apesar de relativamente recente tem sido amplamente adoptada pela indústria, produtores e comunidade científica. É uma tecnologia que permite adicionar flexibilidade e escalabilidade ao design de um sistema embebido. Permite que a performance seja aumentada pelo aumento de cores participantes no sistema como permite ao mesmo tempo diferentes configurações (confinando diferentes camadas de software a diferentes cores).

A tecnologia *multicore*, também usualmente designada de processamento paralelo, apenas pode ser executada em plataformas que o permitam (plataformas *multicore*). Estas plataformas contém mais de um core no seu *System-on-Chip* (SoC). O processamento executado em cada core é feito independentemente, sendo que os cores processam literalmente em simultâneo, levando muitas vezes a problemas de concorrência.

Os cores revelam-se normalmente independentes uns dos outros, excetuando a partilha de certos recursos, como a memória RAM principal e certos periféricos de I/O. Existe ainda um nível de cache (tipicamente L2) que é também partilhado entre os cores incluídos na plataforma, sendo que as caches mais importantes (L1) são particulares a cada core. Nestes níveis de cache associados a cada core pode usualmente ocorrer um problema de coerência: as caches de diferentes cores podem conter valores diferentes de um mesmo endereço da memória principal. Nesta situação recorre-se usualmente a soluções de hardware como a SCU nos processadores da ARM ou recorrendo a soluções baseadas em software responsáveis por manter a coerência transversalmente entre as caches de cada core.

As plataformas *multicore* podem-se dividir em dois grupos: i) plataformas homogéneas e ii) plataformas heterogéneas. O primeiro grupo caracteriza-se por todos os cores pertencentes à plataforma serem idênticos, enquanto que no segundo grupo os cores poderem ser diferentes e até mesmo de diferentes famílias de processadores. O SoC Zynq-7000 é um exemplo das plataformas homogéneas contendo dois processadores idênticos ARM Cortex-A9. Por sua vez o SoC Zynq UltraScale, um exemplo de plataformas heterogéneas, contém até quatro processadores ARM Cortex-A53 e dois processadores ARM Cortex-R5.

O processamento paralelo e recursos partilhados são desafios importantes na configuração de um sistema embebido que utilize uma plataforma *multicore* e são muitas vezes as fontes de problemas de migração de aplicações *single-core*. Estes problemas são geralmente mitigados recorrendo a mecanismos de sincronização e comunicação, por vias da implementação de um sistema virtualizado ou recorrendo a certas características do hardware incluso na plataforma *multicore*. Existem diferentes tipos de configuração *multicore* sendo que cada um contém os seus

próprios desafios, revelados em parte neste subcapítulo.

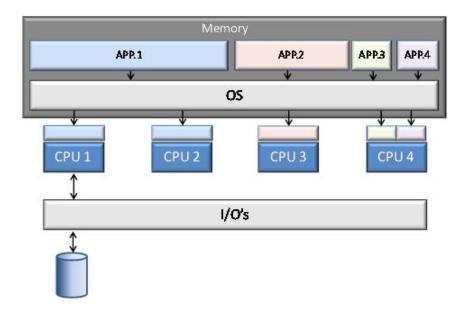

# 2.3.1 Symetric Multiprocessing

A configuração SMP (Symetric Multiprocessing) é apenas vista em plataformas homogéneas e caracteriza-se pelo papel de cada core ser determinado dinamicamente por um mesmo sistema operativo, isto é, existe apenas um sistema operativo que comanda os cores da plataforma pertencentes à configuração SMP.

Qualquer aplicação, processo ou tarefa, que não possua afinidade a um dos cores, pode ser executado em qualquer core, sendo o trabalho do *scheduler* do sistema operativo de migrar essas mesmas tarefas para os diferentes cores. O objetivo principal será o de atingir uma carga de trabalho ótima transversalmente a todos os cores, através da migração das diferentes tarefas. Essa migração, no entanto, não deverá ser muito frequente pois a mudança de tarefas entre cores, poderá afetar a performance da Cache.

Na Figura 2.4 observa-se a arquitetura de um processador multicore com uma configuração SMP, na qual um sistema operativo comanda a totalidade de processadores presentes na plataforma. Esta configuração multicore é a que apresenta o menor footprint de memória pois os diferentes cores correm a mesma imagem do sistema operativo. Todos os cores têm a mesma visão da memória e do hardware partilhado. Usualmente a um dos cores será atribuída a responsabilidade por realizar o boot do sistema operativo assim como garantir o arranque dos restantes cores e ainda eventualmente deverá 'comandar' o acesso a periféricos I/O partilhados.

Num sistema operativo single-core é necessário recorrer a mecanismos de sincronismo para o correto funcionamento das tarefas que partilham os mesmos recursos, pois as mesmas executam em paralelo, i.e., podem ser escalonadas intervaladamente. Num sistema operativo multicore SMP a situação é agravada pelo facto de a execução ser verdadeiramente paralela, sendo necessário a implementação de mecanismos de sincronismo próprios para multicore (por exemplo, spinlock) de maneira a evitar problemas de concorrência de tarefas.

Nesta configuração em que os cores têm acesso à mesma memória (*i.e.*, a memória principal será um partilhada entre os cores) é necessário recorrer a hardware próprio para manter a coerência entre os dados em Cache e na memória principal.

Figura 2.4: Symetric multiprocessing (SMP) num processador quadcore

# 2.3.2 Asymetric Multiprocessing

A configuração AMP (Asymetric Multiprocessing) define-se por tratar cada core de forma individual, isto é, cada core executa independente dos outros cores, correndo em cada uma sua versão individual de um SO. A configuração AMP pode ser considerada homogénea se cada um dos cores correr uma cópia individual do mesmo sistema operativo ou heterogénea se cada core tiver um sistema operativo diferente dos executados nos restantes cores.

Na Figura 2.5 pode-se observar a arquitetura de um processador *multicore* com configuração AMP. Esta configuração é caracterizada por aumentar bastante o *footprint* de memória, pois cada core terá uma cópia própria da sua versão do sistema operativo que executa.

Cada core pode ter uma visão diferente da memória disponível e do hardware partilhado. Não necessitam de mecanismos de coerência de dados, pois cada core teria a sua própria memória, Cache e MMU, salvo claro nas situações de recursos partilhados onde teriam de ser implementados mecanismos de sincronismo ou comunicação.

Tipicamente, os sistemas operativos não podem equilibrar a carga de trabalho efetuada por cada core (através de por exemplo migração de tarefas entre cores), pois tratam-se de cores independentes e com sistemas operativos diferentes, levando em certos casos a níveis de carga de trabalho bastante diferentes e por vezes comprometedoras da estratégia de *multicore* escolhida. Esta situação é facilmente ultrapassada recorrendo a mecanismos de comunicação RPC como vistos

**Figura 2.5:** Asymetric multiprocessing (AMP) num processador quadcore

na arquitetura multicore em [2], referidos na Subsecção 2.4.

Do ponto de vista de cada core, o mesmo corre como se estivesse numa configuração single-core. Isto é, devido à natureza da configuração (cada core tem o seu OS), nenhum core sabe da existência dos outros (à excepção dos mecanismos de sincronização e comunicação). Esta particularidade permite ter um ambiente de execução idêntico ao de uma configuração single-core facilitando assim a migração de aplicações legacy.

## 2.3.2.1 AMP Supervisionado

Similarmente à tecnologia de virtualização, a configuração AMP *multicore* é uma outra forma de obter diferentes classes de sistemas operativos dentro de uma mesma plataforma física. Encontra-se, no entanto, limitado à utilização de um número de sistemas operativos igual ao número de núcleos existentes na plataforma *multicore*.

Comparativamente à técnica de virtualização dual-guest, a utilização da configuração AMP permite níveis de desempenho melhorados uma vez que o tempo de processamento não é partilhado, mas sim paralelizado. Esta paralelização contribui para a mitigação de problemas de starvation. Atribuindo a cada core um diferente sistema operativo garante-se um isolamento temporal suficiente para impedir o problema supracitado. Este problema reflete-se em sistemas virtualizados,

quando um dos sistemas operativos, pelo tipo de escalonamento utilizado, não dispõe de tempo necessário para cumprir prazos de tempo-real ou em último caso de tempo necessário para sequer executar.

A atribuição de um sistema operativo a um determinado core pode ocorrer de forma estática em design time ou de forma dinâmica, recorrendo a mecanismos de comunicação inter-core. Apesar do isolamento temporal fornecido pela configuração assimétrica, esta carece de um isolamento espacial. Este isolamento, como supracitado, é imposto de forma estática ou através de mecanismos de comunicação inter-core. No entanto, ambas as soluções carecem de um isolamento próprio, uma vez que em casos de funcionamento defeituoso de uma das partes integrantes, o isolamento é quebrado.

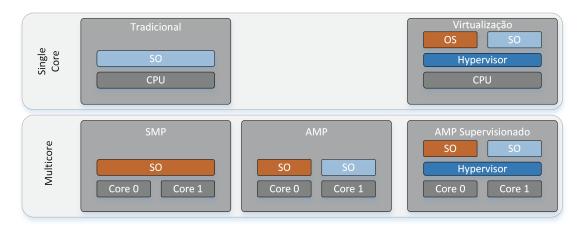

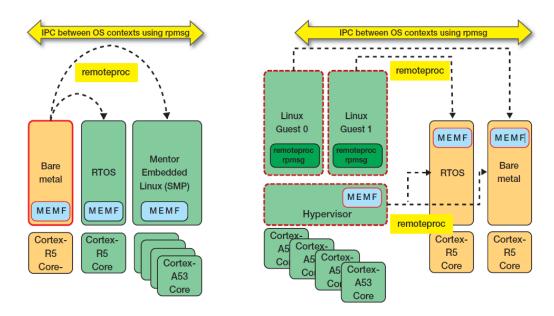

A solução encontrada para esta falta de isolamento é a virtualização do sistema multicore. Esta solução pode também ser vista como uma migração de um sistema virtualizado para uma arquitetura multicore. Esta solução, também designada de AMP supervisionado, é uma integração da tecnologia multicore (AMP) e das técnicas de virtualização, como observado na Figura 2.6. Esta técnica permite obter os níveis de desempenho atribuídos às plataformas multicore e ao mesmo tempo um isolamento seguro entre os guests imposto pelo hypervisor.

**Figura 2.6:** Configurações de virtualização e técnicas *multicore* plataformas *single-core* e *multicore*

Do ponto de vista de um sistema AMP nativo, para além do isolamento a nível de segurança e requisitos de tempo-real, a virtualização do mesmo vem reduzir a complexidade dos próprios sistemas operativos habitantes. Esta redução deve-se à partilha dos diferentes recursos entre os diferentes cores passar a ser gerida pelo hypervisor.

Apesar de ser uma tecnologia relativamente jovem e de ainda haver múltiplos desafios à implementação da virtualização *multicore* em sistemas embebidos, esta,

pelas suas garantias, flexibilidade e acima de tudo escalabilidade tem sido uma das tecnologias mais procuradas. De entre os trabalhos realizados na área destacam-se a presença de hypervisores comerciais como o Mentor Embedded Hypervisor, Wind River Hypervisor ou Xen e ainda hypervisores provindos do âmbito académico como o Xtratum [17] e o SASP [20] que procuram obter o máximo proveito das capacidades oferecidas pela plataforma *multicore*.

# 2.4 Comunicação Inter-Partição

Em sistemas virtualizados a comunicação é um dos componentes vitais para o aproveitamento das potencialidades do próprio sistema. Apesar de não ser obrigatória, a sua presença em sistemas virtualizados é uma constante dado as diversas vantagens inerentes à capacidade de comunicação das partições. A comunicação pode ser realizada entre as próprias partições do sistema, como pode ser realizada entre as partições e o próprio hypervisor, tendo ambas funcionalidades distintas.

Quando realizada entre partição e hypervisor, a comunicação tem como objetivo garantir à partição o acesso a um qualquer dispositivo presente no sistema. Esta comunicação deverá ser realizada através do hypervisor de forma a que o mesmo possa controlar os acessos ao dispositivo e inviabilizar aqueles que possam comprometer o isolamento do sistema. Em casos específicos como no hypervisor Xen, a gestão de dispositivos é migrada para a partição de maior prioridade, "dom0", sendo requerido às restantes partições a comunicação com o "dom0" e não com o hypervisor. Também frequentemente denominada de para-virtualização de dispositivos, esta forma de comunicação é implementada usualmente através de uma abordagem própria ao autor, como observado nas para-drivers desenvolvidas pela XenProject, com uso exclusivo no seu hypervisor Xen. No entanto, surgiu uma tecnologia que tem vindo a ser considerada como "de-facto" standard na virtualização de dispositivos [21], utilizada em hypervisores como o lguest [22], kvm [23] e ainda outros projectos [24].

A comunicação inter-partição ocorre entre partições de um sistema virtualizado seja ele *single-core* ou *multicore*, ou entre partições de um sistema *multicore* não supervisionado. Este tipo de comunicação tem um espectro de funcionalidades mais amplo:

i) **Nivelação da carga de trabalho**: Esta situação é vista em sistemas *multicore* assimétricos virtualizados e não virtualizados, onde a cada core é

atribuído um sistema operativo próprio. Se um sistema operativo estiver sobrecarregado e o nível de carga de trabalho dos restantes for diminuto, podese utilizar a comunicação inter-partição para que os restantes executem parte do seu trabalho, se houver essa compatibilidade. Esta aplicação da comunicação permite criar uma nivelação de cargas de trabalho transversalmente aos cores da plataforma, permitindo potencializar o subaproveitamento de um ou mais cores.

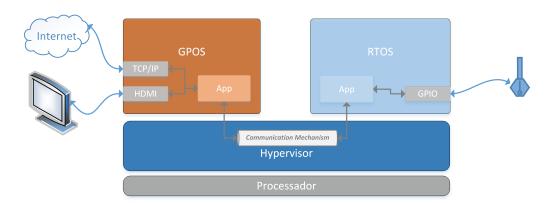

ii) Cooperação entre partições: Esta cooperação será definida pela aplicação, tendo consequentemente uma abrangência mais ampla. A motivação mais usual para esta cooperação é o aproveitamento de características únicas dos guests integrados nas diferentes partições. Nestes casos, existindo sistemas operativos heterogéneos de classes distintas, os mesmos através da comunicação podem usufruir das capacidades uns dos outros. Isto é, um sistema operativo de tempo-real poderá fazer uso das propriedades gráficas do sistema através da cooperação com o sistema operativo de propósito geral, como observado na Figura 2.7. Esta cooperação pode ser motivada em casos esporádicos pela atribuição exclusiva de um recurso a uma partição por parte do hypervisor, sendo necessária a comunicação inter-partição para a utilização desse recurso por parte de partições não autorizadas.

Figura 2.7: Exemplo de cooperação entre diferentes partições

Em sistemas virtualizados, a comunicação inter-partição pode ser realizada de diversas maneiras. Pode ser dividida de acordo com o seu sincronismo e de acordo com a existência ou não de memória partilhada assim como o seu nível de privilégio.

Quanto ao seu sincronismo, existem duas opções possíveis:

• Comunicação Síncrona: Também denominada de comunicação com bloqueio, é caracterizada por cada partição necessitar de esperar pela resposta

da outra parte integrante na comunicação. Este tipo de comunicação devido à sua ineficiência é menos comum em sistemas virtualizados, principalmente em sistemas de tempo-real em que o bloqueio causado pela comunicação poderá ter como última consequência o incumprimento de prazos de tempo-real. Por outro lado, esta é também o tipo de comunicação considerado mais seguro e usado inclusivamente nas especificações de comunicação de TEEs (Global Platform's TEE Client API Specifications).

• Comunicação Assíncrona: Também denominada de comunicação por eventos, é caracterizada por utilizar eventos para notificar as partes integrantes de que existe uma receção de mensagem. Esta abordagem é considerada a mais eficiente pois permite às partições que continuem a executar enquanto que esperam por uma resposta/mensagem. Isto é possível separando o canal de dados do canal de eventos e recorrendo ao uso de callbacks para servirem as mensagens recebidas fora do tempo esperado. No entanto, se não for corretamente implementada, esta abordagem pode ser alvo de diverso ataques, entre os quais o DoS ("Denial-of-Service") onde uma partição impede o funcionamento normal de outra através do envio sucessivo/excessivo de notificações.

Do ponto de vista do canal de dados existem também duas opções, sendo que cada abordagem representa um *trade-off* entre performance e segurança. O canal de dados é implementado com recurso a:

- Memória partilhada: Esta primeira abordagem representa uma comunicação mais rápida e de menor segurança, sendo o seu principal alvo de ataque a própria memória partilhada. Esta pode ter um controlo de acesso (realizado pela MMU) ao nível de privilégio de execução, podendo ser apenas acedida em modo kernel ou em modo user (implementação da comunicação no SafeG ainda que com certos requisitos impostos [25]). Apesar de ter controlo de acesso, se contornado significa uma porta aberta para a quebra do isolamento entre partições. A gestão da memória partilhada neste tipo de comunicação é usualmente feito a partir de uma abordagem própria, porém existe uma tendência em criar um standard centrado na tecnologia VirtIO, como demonstram os trabalhos [2, 26, 24].

- Cópia de memória, realizada pelo hypervisor: Esta abordagem proporciona uma maior segurança em comparação com a primeira abordagem, em detrimento da performance. A diminuição de performance deve-se sobretudo a um excessivo número de cópia de dados assim como um aumento do

número de trocas de contexto ("context-switch") [27, 28]. No entanto, esta abordagem permite evitar ataques à comunicação relacionados com falhas de memória causadas pela remoção de páginas partilhadas ou corrupção da própria memória.

Nas próximas subsecções serão discutidas algumas das diferentes comunicações inter-partição implementadas em diversos hypervisores ou sistemas supervisionados. Será dado um enfase extra à especificação OpenAMP e correspondente implementação *open-source* desenvolvida em conjunto pela Xilinx e Mentor Graphics.

### 2.4.1 Xen

O Hypervisor Xen [18] é um hypervisor com suporte multicore e multiquest, permitindo a conjugação de diferentes sistemas operativos numa mesma plataforma. O mecanismo de comunicação implementado no hypervisor é utilizado para comunicação inter-partição per se, assim como para a para-virtualização de dispositivos realizada através da partição de maior privilégio denominada de "dom0".

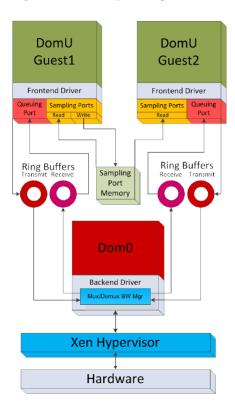

Figura 2.8: Exemplo de comunicação no hypervisor Xen direcionado para a indústria aviónica [1]

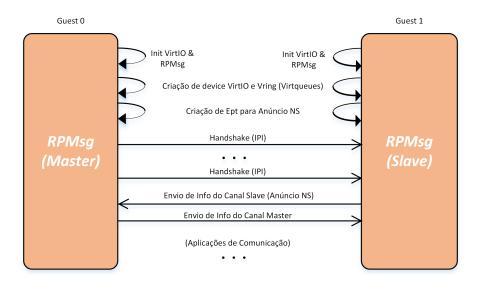

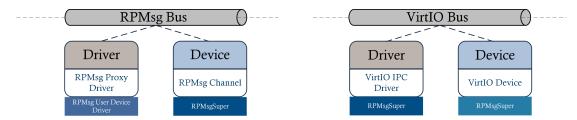

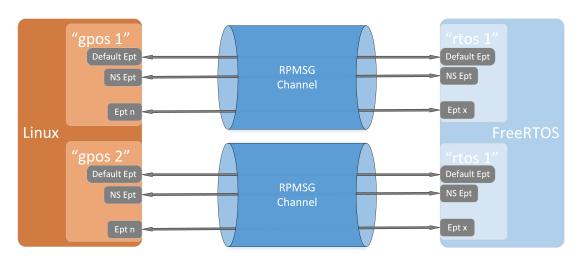

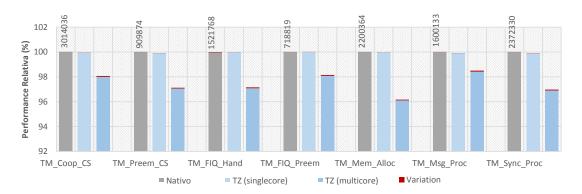

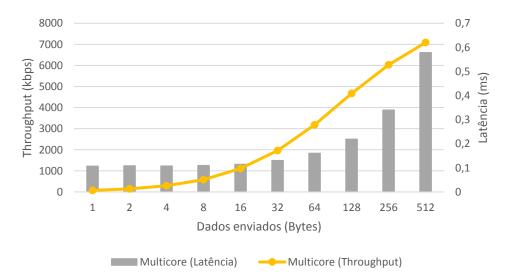

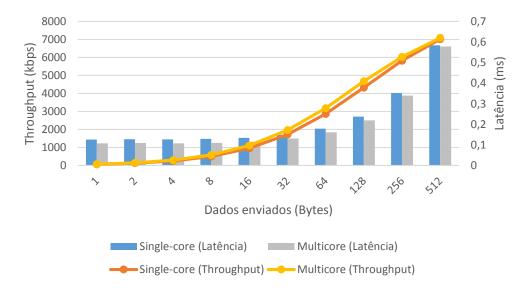

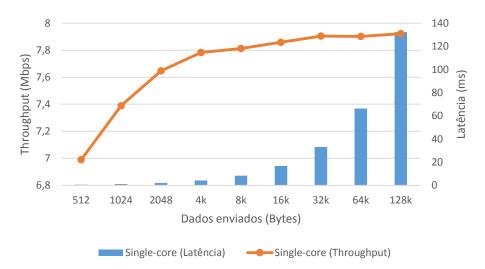

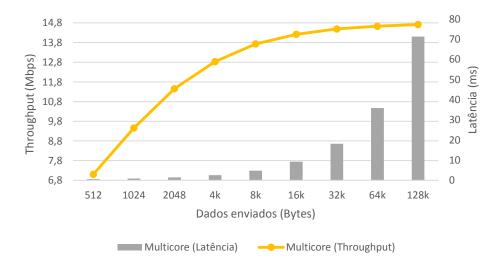

A Figura 2.8 representa uma implementação da comunicação direcionada para a industria aviónica [1]. A utilização de buffers circulares unidirecionais e de portas de amostragem é implementada fazendo uso de memória partilhada ao nível